Fターム[5F032DA03]の内容

Fターム[5F032DA03]に分類される特許

1 - 20 / 243

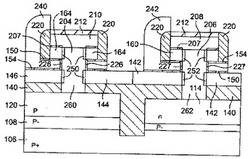

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOIウェハに高耐圧素子の領域と低耐圧素子の領域とが形成された半導体装置であって、製造工程の中で、作業ステージに静電吸着したり、異常放電を引き起こしたりすることを抑えることができる半導体装置を提供する。

【解決手段】半導体層2と、半導体層2の上に形成された絶縁層3と、絶縁層3の上に形成された半導体の第1領域10aと、絶縁層3の上に形成され、第1領域10aに隣接する半導体の第2領域20と、絶縁層3の上に形成され、第1領域10aの側面を覆うように取り囲み、第1領域10aと第2領域20とが直接接続するように開口された開口部31aを有する絶縁体の第1絶縁壁30aとを具備する。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

絶縁膜の形成方法

【課題】均一で高い充填密度を有し、かつ欠陥が少ない絶縁膜を形成することができる方法の提供。

【解決手段】基板表面に、二酸化ケイ素微粒子と、ポリマーと、界面活性剤と、分散媒とを含む二酸化ケイ素分散液を塗布し、次いでポリシラザン組成物を塗布した後、加熱して絶縁膜を形成させる、絶縁膜の形成方法。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイおよび周辺回路領域の素子分離領域の深さを調節しつつ、周辺回路部の素子分離領域に形成されるマイクロトレンチ形状の影響を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられデータを記憶する複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられメモリセルアレイを制御する周辺回路部とを備えている。素子分離部は、複数のメモリセルおよび周辺回路部が形成されるアクティブエリア間に設けられている。側壁膜は、周辺回路部におけるアクティブエリアの側面に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域とメモリセル領域の外周に周辺回路領域を有する半導体装置の製造において、セルフアラインダブルパターニングを用いてメモリセル領域の半導体基板に溝を形成する際、メモリセル領域端部において正常に溝が形成されないという問題がある。

【解決手段】メモリセル領域の第1のマスクパターンを幅W1、ピッチW3(但し、W3>2×W1)のラインパターンに形成し、その上に犠牲膜をW1の幅のギャップが残るように形成した後、塗布法で第2のマスクパターンとなる膜を形成し、犠牲膜と第2のマスクパターンとなる膜をエッチバックして第1のマスクパターン表面を露出させる。その後、第1及び第2のマスクパターン間の犠牲膜を選択的に除去し、溝パターンを形成する。周辺回路領域では、メモリセル領域との境界部を残して第1のマスクパターンを形成せず、境界部に形成される第1のマスクパターンの幅W2をW1の1〜4倍とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝を塗布系の材料で埋め込む素子分離構造において、熱処理時に素子分離溝に大きな応力が作用することを防止する。

【解決手段】メモリセル領域に形成され第1の開口幅を有する第1の素子分離溝と、周辺回路領域に形成され第1の開口幅より大きい第2の開口幅を有する第2の素子分離溝と、第1の素子分離溝の内面に形成された第1の酸化膜と、第1の酸化膜上に形成されて前記第1の素子分離溝内に埋め込まれた第1の塗布型酸化膜と、第2の素子分離溝の内面のうちの側部に形成された第2の酸化膜と、第2の素子分離溝内の内面のうちの底部上に形成された第3の酸化膜と、第3の酸化膜上に形成されて第2の素子分離溝内に埋め込まれた第2の塗布型酸化膜とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】金奥不純物を除去するゲッタリングの効果を高めるために有利な技術を提供する。

【解決手段】半導体装置の製造方法は第1絶縁膜102を形成する工程と、第1絶縁膜102を除去する工程とポリシリコン膜103を形成する工程と、第1面の1011側および第2面1012の側のポリシリコン膜103の上に第2絶縁膜201を形成する工程と、開口OPを有するマスクを使って第1面1011の側の第2絶縁膜をエッチングする処理を含み、半導体基板101の第1面1011における開口105によって規定される領域に素子分離を形成する工程と、第1面1011の側および第2面1012の側の第2絶縁膜201を除去する工程と、第1面1011および第2面1012のうち第1面1011の側のポリシリコン膜103を除去する工程と、第2面1012の側のポリシリコン膜103が除去されないように保護する保護膜を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板にアライメントマークとなる溝を形成し、アライメントマークに位置合わせして素子分離領域となる領域を露出し素子領域となる領域を覆うマスク膜を形成し、マスク膜をマスクとして半導体基板を異方性エッチングし、半導体基板の素子分離領域となる領域に素子分離溝を形成し、素子分離溝を絶縁膜で埋め込み素子分離絶縁膜を形成する半導体装置の製造方法において、溝を形成する工程では、マスク膜の厚さに相当する深さよりも浅い溝を形成する。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体装置

【課題】半導体装置における素子形成領域エッジ部分の電界集中を抑制し、素子の消費電力低減を図る。

【解決手段】半導体装置は、シリコンを含む絶縁膜上に選択的に形成された厚さが35nm以下の半導体膜と、半導体膜の周囲に、半導体膜以上の厚みの酸化シリコン膜で絶縁膜上に形成された素子分離膜と、素子分離膜上及び半導体膜上に、素子分離膜及び半導体膜で構成される凹部に沿って平面図で直線状に形成されたゲート電極膜と、を有するため、半導体膜上面は、その周囲に設けられた酸化シリコン膜の上面よりも低く構成される。そのため、ゲート電極膜が半導体膜の側面の一部にまわりこんで形成されることはなく、従来のような電界集中の問題を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】第2絶縁膜からセルフアラインに所定の距離だけ離して半導体素子を形成可能で、第2絶縁膜と単結晶層との界面の上部でのリーク電流の発生の低減が可能な半導体装置の製造方法を提供する。

【解決手段】SOI基板の単結晶層の上方に形成した第1絶縁膜をストッパに単結晶層と第1耐酸化膜をエッチングして第1絶縁膜の上に単結晶柱5aを形成し、第1耐酸化膜を単結晶柱5aの上に配置したまま単結晶柱5aを一部熱酸化し単結晶柱5aの側面を囲むように閉ループパターンで形成され第1耐酸化膜の外周部の直下にせり出し部10aを有する第2絶縁膜10を形成し、第1耐酸化膜を除去して単結晶柱5aの上面を露出させ、単結晶柱5aの上面に半導体素子を形成する。第2絶縁膜10を形成したことにより、せり出し部10aの下の単結晶柱5aの上面は、側面の近くになるにつれ徐々にその上面の高さが低くなり側面につながる傾斜面になっている。

(もっと読む)

1 - 20 / 243

[ Back to top ]