Fターム[5F033HH04]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 半導体(基板を除く) (1,867) | 多結晶Si (1,545)

Fターム[5F033HH04]に分類される特許

161 - 180 / 1,545

半導体装置

【課題】 製造が容易でかつ絶縁性に優れ、平坦な上面(表面)を持つパッシベーション構造を備えた配線構造を、低コストかつ短リードタイムで形成する、半導体装置を提供する。また、配線抵抗が小さくボンディング耐性が高い配線構造を提供する。

【解決手段】 所望の素子領域の形成された基板表面に形成された配線層と、前記配線層表面を覆う層間絶縁膜と、前記層間絶縁膜表面全体を覆うように形成された窒化シリコン膜と、前記窒化シリコン膜の上層に形成された最上層メタルとしての金層からなるメタル配線層と、前記窒化シリコン膜と前記メタル配線層との間に形成されたバリア層と、前記メタル配線層上に形成されたポリイミドからなる平坦化絶縁膜とを含み、前記バリア層と前記配線層は、前記窒化シリコン膜と前記層間絶縁膜に形成されたスルーホールを通じて接続されており、前記平坦化絶縁膜が一部領域で除去せしめられ、前記メタル配線層にボンディングがなされていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 エアギャップ構造を簡易な方法で形成する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、半導体基板上に導電層を含む被加工膜を形成する工程と、前記被加工膜上にダミー膜を形成する工程と、を備えている。さらに、前記ダミー膜を所望の形状にデポ条件の異方性エッチングにより加工する工程と、前記被加工膜を所望の形状に異方性エッチングにより加工する工程と、前記所望の形状に加工された被加工膜上の前記ダミー膜を異方性エッチングにより除去する工程と、前記被加工膜上に上層膜を形成する工程と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】センシング部を複数の基板で封止した半導体装置において、基板の平面方向に配線を設けたとしても、配線のレイアウトを簡略化することができる構造、およびその製造方法を提供する。

【解決手段】キャップ部300は、センサ部100に設けられた第1固定部と第2固定部とを電気的に接続したクロス配線部323を備え、クロス配線部323はキャップ部300の一面301に配置されたクロス配線322を備えている。また、キャップ部300は、キャップ部300を貫通し、一端がクロス配線322に電気的に接続され、他端がキャップ部300の他面302に配置された貫通電極344を備えている。これにより、貫通電極344を介してクロス配線322の電位、すなわち、センサ部100の第1固定部および第2固定部の電位をキャップ部300の他面302に取り出すことができる。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置

【課題】複雑な形状を有しながらも応力分布のばらつきが少ない活性領域を有する半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、素子分離領域を有する基板と、前記素子分離領域に分離された、不純物拡散領域を有する前記基板上の複数の四角形の活性領域と、前記複数の活性領域の集合からなり、段差を含む輪郭形状を有する大活性領域とを有する。前記複数の活性領域の前記不純物拡散領域のうち、前記素子分離領域を挟んで向かい合う不純物拡散領域は、電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】実施の形態の半導体装置は、シリコンを含む半導体基板10上の層間絶縁膜11に形成されたコンタクトホール12の底部14に形成され、コンタクトホール12に形成されるコンタクトプラグ21と電気的に接続するニッケルシリサイド膜18を有する。このニッケルシリサイド膜18は、ニッケルシリサイド膜18とコンタクトプラグ21の界面18aが半導体基板10と層間絶縁膜11の界面10aより高い。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

インクの調製方法及びパターン形成方法

【課題】インクからナノ粒子の集合体をより確実に取り除き、これによって機能性に優れたパターンを形成可能とする。

【解決手段】ナノ粒子を含むインクの調製方法であって、インクを遠心分離し、ナノ粒子の集合体を取り除くことを特徴とする。

(もっと読む)

導電材埋め込み方法及び半導体装置の製造方法

【課題】 従来の方法と比較して、短時間で凹部の全体に導電材を埋め込むことができる技術を提供する。

【解決手段】 本願に係る導電材の埋め込み方法は、半導体装置の製造過程において表面に形成される凹部22に導電材を埋め込む方法に関する。この方法は、凹部22の少なくとも底面に露出する下地層10の表面に不純物24aを定着させる不純物定着工程と、不純物24aが定着した下地層10を利用して導電材をVLS成長させて、凹部の全体に導電材を埋め込むVLS成長工程とを有する。この方法では、VLS成長によって凹部22に導電材を埋め込むため、短時間で導電材を埋め込むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置およびその製造方法

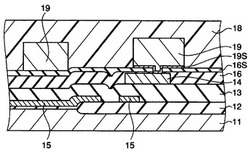

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置

【課題】2つのトランジスタを混載した半導体装置において、ダミー配線を介して配線間で短絡が発生するのを防止し、信頼性の高い混載デバイスを実現可能にする。

【解決手段】本発明の半導体装置は、微細CMOS4Aと、微細CMOS4Aに接続される微細配線15とを有する微細CMOS領域と、微細CMOS4Aよりも耐圧が高い高耐圧デバイス4Bと、高耐圧デバイス4Bに接続され、平面視において微細配線15よりも配線幅が広いドレイン配線115及びソース配線116と、を有する高耐圧デバイス領域と、を具備し、高耐圧デバイス領域には、電気的に孤立したダミー配線14が少なくともドレイン配線115及びソース配線116に隣接して配置されない。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体装置

【課題】低抵抗かつ微細化が可能なグラフェン配線を有する半導体装置およびその製造方法を提供する。

【解決手段】一実施の形態によれば、半導体装置は、配線と前記配線に接続されるコンタクトプラグを有する。前記配線は、長さ方向の両側面に触媒層を有する基体と、前記基体の前記両側面上に前記触媒層と接して形成され、前記基体の前記両側面と垂直に積層された複数のグラフェンを有するグラフェン層を有する。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

161 - 180 / 1,545

[ Back to top ]