Fターム[5F033HH08]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Al (4,491)

Fターム[5F033HH08]の下位に属するFターム

Al合金 (1,292)

Fターム[5F033HH08]に分類される特許

201 - 220 / 3,199

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

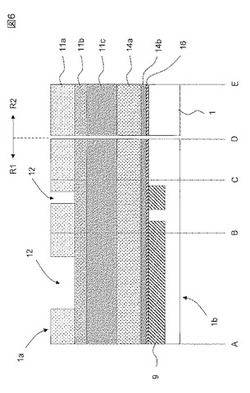

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、Si基板の表面にシリサイド層を形成しつつ、Si基板の裏面における低融点金属とSi基板のSiとの相互拡散を防止できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体素子の製造方法は、Si基板の裏面に低融点金属を形成する工程と、該Si基板の表面に高融点金属層を形成する工程と、該高融点金属層の上にレーザ吸収層を形成する工程と、該レーザ吸収層にレーザ光を照射し、該低融点金属と該Si基板のSiとの相互拡散を防ぐように該低融点金属の温度を低く保ちつつ、該レーザ吸収層と該高融点金属層の界面、及び該高融点金属層と該Si基板の界面にシリサイド層を形成する工程と、該レーザ吸収層をエッチングする工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】一つの実施形態によれば、半導体装置は、電極、メッキ膜、半田、及びコネクタが設けられる。電極は、半導体チップ表面に設けられた第一の電極部と、第一の電極部上に設けられた絶縁膜の開口部を覆うように設けられ、第一の電極部に接続された突起状の第二の電極部とから構成される。メッキ膜は、第二の電極部上に設けられる。半田は、絶縁膜及びメッキ膜上に設けられる。コネクタは、一端の第一の構成部が半田上に設けられ、他端の第二の構造部が端子に接続され、電極と電極端子の間を接続する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得る。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

(もっと読む)

光電変換装置、撮像システム及びその製造方法

【課題】 フローティングディフュージョン部の容量の増大を抑制することが可能な光電変換装置を提供する。

【解決手段】 光電変換素子と、フローティングディフュージョン部と、転送トランジスタと、増幅トランジスタとが配された半導体基板と、第1の配線層と、第2の配線層とを含む複数の配線層と、を有する光電変換装置において、転送トランジスタのゲート電極と、前記第2の配線層とがスタックコンタクト構造で接続されている。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

電子素子用金属層、電子素子用金属層積層体、電子素子、トランジスタ素子

【課題】電流のリークを抑制する電子素子用金属層を提供する。

【解決手段】被形成面12に、金属インクを塗布し金属粒子層を形成しパターニングする。基板側からランプ照射し、金属粒子層の下層部分のみを溶融させ、下層部分の金属粒子どうしを融着させる。金属粒子の融着層14Aと金属粒子の非融着層14Bとをこの順で有する積層体で構成されたゲート電極14とする。

(もっと読む)

半導体装置及びその配線の形成方法

【課題】 密着性を低下させることなく切削性を向上させることが可能な半導体装置及びその配線の形成方法を提供する。

【解決手段】 基板1上に開口部を形成するように絶縁樹脂4を形成する工程と、前記絶縁樹脂4上と、前記開口部の側壁面5aと底面とに第1配線層7を形成する工程と、前記第1配線層7上に第2配線層8を設ける工程と、前記開口部の前記側壁面5a上に形成された前記第1配線層7を露出するように切削して平坦化する工程とを含み、前記第1配線層7を形成する工程では、前記開口部の前記側壁面5aに形成される前記第1配線層7の厚さより前記底面に形成される前記第1配線層7の厚さの方が厚くなるように形成することを特徴としている。

(もっと読む)

半導体集積回路装置およびその製造方法ならびにそれを用いた電子システム

【課題】再配線のランド部にバンプ電極が接続された半導体集積回路装置において、再配線と半田バンプとの接着強度を向上させる。

【解決手段】再配線20のランド部20Aは、再配線20を構成する5層の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16および第2Ni膜17)のうち、最上層の第2Ni膜17の面積が他の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16)の面積よりも大きくなるように構成され、この第2Ni膜17の表面に半田バンプ21が接続されている。そして、半田バンプ21の端部では、第2Ni膜17の直下にポリイミド樹脂膜22が形成されている。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

厚膜金属電極の形成方法、及び厚膜レジストの形成方法

【課題】炭化珪素基板に形成された回路素子層上に、厚さが7μm以上で、かつ面内均一性に優れたポジ−ネガ反転型レジストが形成可能な厚膜金属電極の形成方法、及び厚膜レジストの形成方法を提供する。

【解決手段】HMDS処理された回路素子層の上面に、第1の粘性値を有した第1のポジ−ネガ反転型レジストを形成し、次いで、第1のポジ−ネガ反転型レジスト上に、第1及び第2のポジ−ネガ反転型レジスト(厚膜レジスト)の合計の厚さが7μm以上となるように、第1の粘性値よりも大きい第2の粘性値を有した第2のポジ−ネガ反転型レジストを形成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

201 - 220 / 3,199

[ Back to top ]