Fターム[5F033HH09]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Al (4,491) | Al合金 (1,292)

Fターム[5F033HH09]の下位に属するFターム

Si、Cu以外を含むもの (235)

Fターム[5F033HH09]に分類される特許

161 - 180 / 1,057

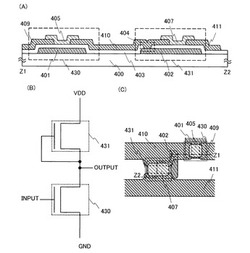

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】IGZO層とITO層とを電気的に接続する場合には、易加工性を備え電気抵抗率が低いアルミ等の金属と高融点金属としてのチタン等との積層構造を用いる必要があるが、積層構造を形成する場合、複数の金属層を形成する必要がある。そのため製造工程が増えると共に、パーティクル等の発生確率が増え、歩留まりを落とすという課題がある。

【解決手段】ITO等の金属酸化物を用いた画素電極2aが、層間絶縁層9に形成されたコンタクトホール9aを介してIGZO層を用いた配線層7aと電気的に接続している。画素電極2aとAl−Nd合金を用いた上電極6cと直接接触させた場合、コンタクト抵抗が高くなるが、配線層7aにIGZO層を用い、画素電極2aにITO等の第2金属酸化物配線層を用いた場合、互いの構造が類似していることから、密接させるだけで接触抵抗の増大を招くことなく電気的に導通を取ることが可能となる。

(もっと読む)

デバイスの製造方法及びデバイス

【課題】メモリ機能等を有する機能膜の水による劣化を防止すること。

【解決手段】成膜装置内で、機能膜が形成された基板上に、上記機能膜を覆うように、絶縁膜を形成する絶縁膜形成工程と、形成した上記絶縁膜の表面をプラズマに曝すプラズマ処理工程とを繰り返すこと。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuバンプを形成可能とする半導体装置を提供する。

【解決手段】半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上に形成されるCuから成るスタッドバンプ26とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ14とを有し、前記Cuワイヤ14と前記Cu配線層9との間には合金層13が配置されることを特徴とする。

(もっと読む)

薄膜トランジスタパネルの製造方法

【課題】 液晶表示装置の薄膜トランジスタパネルにおいて、Al系金属からなるゲート電極等がレジスト現像液およびレジスト剥離液によるダメージを受けにくいようにする。

【解決手段】 Al系金属からなるゲート電極2およびゲート配線3の上面にAl酸化膜2a、3aを形成すると、ゲート電極2およびゲート配線3の上面がレジスト膜43a、43b、43c用の現像液および剥離液にさらされることがなく、ゲート電極2およびゲート配線3がレジスト膜43a、43b、43c用の現像液および剥離液によるダメージを受けにくいようにすることができる。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

配線形成方法

【課題】樹脂基板上に、接着層等を形成するための別の工程を加えることなく、基板との密着性の高い導電性配線を簡単に形成することができる配線形成方法を提供することを目的とする。

【解決手段】樹脂基板1上に、導電性微粒子を含有する分散溶液の塗布層3を形成する工程と、レーザ光6を塗布層3の特定領域に連続的に照射していくことで、導電性微細配線4を形成する工程と、導電性微細配線4以外の領域の材料を除去する工程とを備え、塗布層3の厚さをd、塗布層3の光吸収係数をα、レーザ光6の入射光強度をI0、樹脂基板1上に到達するレーザ光6の透過光強度をI1とするとき、以下の関係式から成り立つことを特徴とする。

log(I1/I0)=−αd

(もっと読む)

半導体装置

【課題】金属配線を保護する保護膜の被覆性を向上させることができる半導体装置を得る。

【解決手段】金属配線14の屈曲部16の配線幅が広くなると、配線をパターニングするためのレジストの塗布幅が広くなる。レジストの塗布幅が広くなるとレジストの量が増え、レジストプロファイルのテーパー形状が強くなる(側面が寝てくる)。これにより、パターニングされた金属配線14の側面(メタルエッチング形状)もテーパー形状が強くなる(側面が寝てくる)ため、屈曲部16を覆うパッシベーション保護膜の膜厚が厚くなる。これにより、金属配線を保護する保護膜の被覆性を向上させることができる。

(もっと読む)

半導体装置

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】半導体基板1上に積層された複数の層間絶縁膜16、19、22と、複数の層間絶縁膜16、19、22の最上面の上に形成され、外部からプローブが当てられるプローブ接触領域を有するパッド25と、複数の層間絶縁膜16、19、22の間に形成される複数層の配線12,15、18と、パッド25のプローブ接触領域の直下の領域に形成され、前記層間絶縁膜22が充填される非直線状スリットか孔の少なくとも一方を有する導電性パターンを有する応力緩和部42とを有する。

(もっと読む)

貫通電極付き半導体デバイスの製造方法

【課題】既にデバイスや配線が形成されている半導体基板に対し、効率良く貫通電極を形成する貫通電極付き半導体デバイスの製造方法を提供する。

【解決手段】半導体基板11の主面に第1のシリコン酸化膜12を形成し、主面Aからもう一方の主面側の第1のシリコン酸化膜12に達する細孔13を形成し、細孔13の孔壁に第2のシリコン酸化膜14を形成し、第1のシリコン酸化膜12上に第1の金属薄膜15および第2の金属薄膜16を形成し、細孔13の端部における第1のシリコン酸化膜12を除去し、細孔13内に導電性物質を充填し貫通電極17を形成する貫通電極付き半導体基板の製造方法。細孔13を、DRIE法で形成する。導電性物質を、溶融金属吸引法または印刷法により細孔13内に充填する。

(もっと読む)

半導体装置

【課題】パワーMISFETのゲート抵抗を低減し、装置の特性の向上を図る。

【解決手段】チップ領域CAのY方向にストライプ状に形成された複数の溝の内部の多結晶シリコン膜よりなるゲート部と電気的に接続されるゲート電極GEを、前記ストライプ状の溝の間に形成されるソース領域と電気的に接続されるソース電極SEと同層の膜で形成し、さらに、ゲート電極GEを、チップ領域CAの周辺に沿って形成されたゲート電極部G1と、チップ領域CAをX方向に2分割するよう配置されたゲートフィンガー部G2とで構成し、ソース電極SEを、ゲートフィンガー部G2の上部に位置する部分と、下部に位置する部分とで構成し、ゲート電極GEおよびソース電極SEをバンプ電極を介してリードフレームと接続する。

(もっと読む)

層間絶縁膜の平坦化方法

【課題】配線層による層間絶縁膜の凹凸の影響を排除することで、平坦化を容易とすることができる層間絶縁膜の平坦化方法を提供する。

【解決手段】層間絶縁膜の平坦化方法は、まず、配線層12a,12bを形成し、高密度プラズマCVDにより配線層12a,12bを覆って第1HDP酸化膜13を形成し、テトラエトキシシランガスを用いたプラズマCVDにより第1HDP酸化膜13上にPL−TEOS酸化膜14を形成し、高密度プラズマCVDによりPL−TEOS酸化膜14上に、第2HDP酸化膜15を形成する。次に、PL−TEOS酸化膜14が露出するまでCMPにより第2HDP酸化膜15を研磨する。そして、PL−TEOS酸化膜14が除去されるまで、第2HDP酸化膜15とPL−TEOS酸化膜14とを同時にCMPにより平坦化する。そうすることで、平坦化された層間絶縁膜10を得ることができる。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面側で、Al電極膜表面にボイドが形成され難くすることのできる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の一方の主面側に半導体機能領域と所要のコンタクトホール8を含む層間絶縁膜7パターンを形成した後、該半導体基板1の前記一方の主面側の全面に、厚膜のアルミニウム膜またはアルミニウム合金膜を成膜して前記コンタクトホール8の底面を含む半導体基板1表面に導電接触させて所要の電極膜9を形成する際に、前記アルミニウムの成膜工程を膜厚に関して複数回に分け、複数回の前記アルミニウム成膜工程の間に、直前のアルミニウム膜表面の凹凸を等方性エッチングにより平坦化する工程を設ける半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ13とを有することを特徴とする。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】半導体装置において、多層配線構造におけるライン間容量を低減しながら、多層配線構造の機械的強度の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板の上に配された多層配線構造とを備え、前記多層配線構造は、第1の導電ラインと、前記第1の導電ラインを覆う絶縁膜と、前記半導体基板の表面に垂直な方向から透視した場合に前記第1の導電ラインと交差するように前記絶縁膜の上に配された第2の導電ラインとを含み、前記絶縁膜は、前記第1の導電ラインと前記第2の導電ラインとの交差する領域にギャップを有し、前記ギャップにおける前記第2の導電ラインに沿った方向の幅は、前記第1の導電ラインの幅以下である。

(もっと読む)

161 - 180 / 1,057

[ Back to top ]