Fターム[5F033HH09]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Al (4,491) | Al合金 (1,292)

Fターム[5F033HH09]の下位に属するFターム

Si、Cu以外を含むもの (235)

Fターム[5F033HH09]に分類される特許

201 - 220 / 1,057

半導体装置及びその製造方法

【課題】 貫通電極を有する半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 本発明の半導体装置は、半導体チップ10Aと、前記半導体チップ10Aの表面上に第1の絶縁膜11を介して形成されたパッド電極12と、前記パッド電極12の一部上及び前記第1の絶縁膜11上に形成され、かつ前記パッド電極12を露出する開口部14を有した第2の絶縁膜13と、前記開口部14を通して前記パッド電極12と電気的に接続されて前記第2の絶縁膜11の一部上に延びる第1の配線層15と、前記パッド電極12を介して前記開口部14に対峙し、前記半導体チップ10Aの裏面から当該パッド電極12に到達し、かつ前記開口部14と実質的に同等の開口径を有するビアホール16と、前記ビアホール16内に形成され、かつ当該ビアホール16を通して前記パッド電極12と電気的に接続された貫通電極20と、を備えることを特徴とする。

(もっと読む)

配線剥離防止構造を有する半導体集積回路

【課題】 半導体集積回路のチップ面積を増大させることなく、配線層の剥離防止構造を作製し、チップへの応力による配線の切断を防止する。

【解決手段】

多層配線構造の半導体集積回路チップ周辺部の金属配線層202〜205上に、当該金属配線層同士を接続するためのスルーホール、或いは最下層の金属配線層と基板上に形成された素子とを電気的に接続するためのコンタクトホールを、夫々、当該金属配線層の直上にスルーホールが形成される領域101と、当該金属配線層の直下にスルーホール或いはコンタクトホールが形成される領域102とが基板面内で重なり合わないように、金属配線層上に複数、集中して配置する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】現在のLSI、すなわち、半導体集積回路装置の製造工程においては、デバイスの組み立て(たとえばレジン封止)後に、高温(たとえば摂氏85から130度程度)・高湿(たとえば湿度80%程度)の環境下での電圧印加試験(すなわち、高温・高湿試験)が広く行われている。これに関して、高温・高湿試験中に、正電圧が印加されるアルミニウム系ボンディング・パッドの上面端部において、封止レジン等を通して侵入した水分に起因する電気化学反応により、反射防止膜である窒化チタン膜が酸化されて膨張し、上部膜との剥がれや、膜クラックが発生することが、本願発明者等によって明らかにされた。

【解決手段】本願発明は、アルミニウム系ボンディング・パッドの周辺部において、パッド上の窒化チタン膜をリング・スリット状に除去するものである。

(もっと読む)

液晶パネル

【課題】複数個のアレイ基板を同時に形成するためのアレイ基板用マザー基板にスピンコ

ーターを用いてレジスト塗布する際、表示領域内に放射状の塗布ムラが生じないような配

線パターンとされたアレイ基板を備えた液晶パネルを提供すること。

【解決手段】本発明の液晶パネルは、液晶層を挟持して対向配置された一対の基板を有し

、前記一対の基板の一方の表示領域には複数のサブ画素がマトリクス状に形成されている

と共に、表示領域の周縁部には表示領域からゲート配線39G及びソース配線39Sが端

子領域まで延在されている液晶パネルにおいて、前記互いに隣接するゲート配線39G及

びソース配線39S等の引き回し配線の直近の屈曲点P1同士を順次結んでなるラインが

、端子領域が形成されている辺と実質的に平行な直線ラインL1とされている。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属パターン層30を形成する工程と、絶縁層12に、素子ZDの接続部に到達するコンタクトホールCHを形成する工程と、コンタクトホールCH内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属パターン層30に接続されると共に、コンタクトホールCHを通して素子ZDに接続される配線層40,40aを形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

表示装置用Al合金膜、薄膜トランジスタ基板および表示装置

【課題】Al合金膜とTFTの半導体層との間のバリアメタル層を省略可能な新規のSiダイレクトコンタクト技術を提供する。詳細には、Al合金膜をTFTの半導体層と直接接続しても、AlとSiの相互拡散を防止でき、良好なTFT特性が得られると共に、TFTの製造工程でAl合金膜に約100〜300℃の熱履歴が加わった場合でも、低い電気抵抗と優れた耐熱性が得られる新規なSiダイレクトコンタクト技術を提供する。

【解決手段】本発明の表示装置用Al合金膜は、表示装置の基板上で、薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、上記Al合金膜は、Geを0.1〜4原子%;La、GdおよびNdよりなる群から選ばれる少なくとも1種を0.1〜1原子%;並びにTa、Nb、Re、ZrおよびTiよりなる群から選ばれる少なくとも1種を含有する。

(もっと読む)

半導体素子の製造方法

【課題】柱状残渣の発生を抑制した半導体素子の製造方法の提供。

【解決手段】基板12上に配線層14を形成する工程と、基板12および配線層14を覆うように、第3絶縁膜22、第2絶縁膜(SiN膜)24、および第1絶縁膜(PSG膜)26を順に積層した層間絶縁層20を形成する工程と、第1絶縁膜26上にマスクパターンを形成する工程、ウェットエッチング処理によって第1絶縁膜26のコンタクトホール30形成部分を除去する工程、少なくとも等方性ドライエッチングを含むエッチング処理によって第2絶縁膜24のコンタクトホール30形成部分を除去する工程、およびエッチング処理によって第3絶縁膜22のコンタクトホール30形成部分を除去する工程、を経て配線層14表面が露出するよう層間絶縁層20にコンタクトホール30を形成する工程と、を有する半導体素子10の製造方法。

(もっと読む)

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

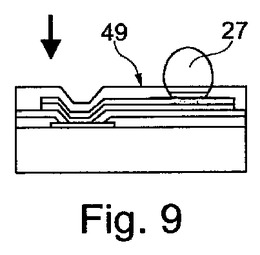

基板接触のためのコンタクト配置

この発明は、基板接触、特に半導体基板(21)の端子面を接触させるためのコンタクト配置(47,48,49,50,55,56,57)に関し、基板の底部端子面によって基板表面に形成された、コンタクト配置の少なくとも1つの内側コンタクト(25)と、内側コンタクトの外側端縁領域と周辺部とを少なくとも被覆するパッシベーション層(34,35)と、内側コンタクト(25)から横方向に離れるようにパッシベーション層(34,35)の上に延在する少なくとも1つの下側コンタクトストリップ(36)と、下側コンタクトストリップの上に延在するもう1つの上側のコンタクトストリップ(37,38,39)とを含み、このもう1つのコンタクトストリップは、コンタクトメタライゼーションによって形成されており、このコンタクトメタライゼーションは、ニッケル(Ni)層からまたはニッケルとパラジウム(Pd)とを含有する層構造(38,39)から実質的に構成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】洗浄処理での腐食を抑えた高性能で高品質の半導体装置を提供する。

【解決手段】例えば、LCOSデバイスにおける画素電極90を形成する際、画素電極90の材料となる層に、間口の開口幅A1に対して底部の開口幅A2が狭い溝91を形成して、個々の画素電極90を形成した後、洗浄処理を行う。溝91の間口を広くすることで、洗浄処理時の液の滞留が抑えられ、画素電極90の腐食が抑えられるようになる。

(もっと読む)

半導体装置の製造方法

【課題】欠陥の発生を防止し且つ電気的特性に優れた強誘電体キャパシタを用いた半導体装置の製造方法を提供する。

【解決手段】第1の導電層40を形成し、第1の導電層40の表面に酸化膜10を形成し、酸化膜10を大気にさらし、酸化膜10を、減圧下且つ第1の温度で減圧加熱処理し、減圧加熱処理された酸化膜10を大気にさらすことなく、減圧下且つ第1の温度よりも低い第2の温度で、非晶質の第1の誘電体層41を酸化膜10上に形成し、第1の温度よりも高い第3の温度で、非晶質の第1の誘電体層41を結晶化する。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

デバイス及びその製造方法

【課題】微細孔の内壁と微細孔に充填した導電性物質からなる貫通電極との間で発生する隙間や拡散、酸化を抑制し、パッドと貫通電極との電気的接続の安定性を向上させることが可能なデバイスの製造方法を提供する。

【解決手段】第一基板と、該第一基板の一方の面側に配された、機能素子及び該機能素子に第一配線を介して電気的に接続されたパッドと、該パッドと電気的に接続され、前記第一基板の一方の面から他方の面に至る微細孔内に第一導電体を充填してなる貫通電極とを、少なくとも具備してなるデバイスの製造方法であって、前記第一基板の他方の面から、Deep-Reactive Ion Etching 法を用いて、前記パッドが露出するまで前記微細孔を形成する工程Aと、前記微細孔の内面の少なくとも一部に、前記第一導電体とは異なる第二導電体からなる導電部を形成する工程Bと、前記微細孔の内部に前記第一導電体を充填する工程Cと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性でかつ高レイアウト密度配線と混載可能な容量素子を備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明は、容量素子を有する半導体装置であって、アルミニウム合金膜102と、高融点金属膜を含む上層バリア膜103とを含む金属配線200aおよび下部電極200bと、下部電極200b上に形成された容量絶縁膜104と、容量絶縁膜104上に形成された上部電極105とを有する。高融点金属膜の膜厚は、40nm以上、80nm以下であり、容量絶縁膜104は、有機シランを原料としたシリコン酸化膜からなることを特徴とする。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

半導体装置の製造方法及び半導体基板

【課題】表面に段差部分を有する構造物を覆う上部絶縁膜を基板全面に亘って均一に表面平坦化し、上部絶縁膜の表面平坦化及び膜厚均一化を共に実現して、所期の半導体素子を安定且つ確実に形成する。

【解決手段】半導体基板1上に、多層配線構造の下層部分2を適宜形成した後、半導体基板1のベベル部1aを覆うように、下層部分2と略同等の膜厚に縁部絶縁膜14を形成し、上部絶縁膜11aをCMPで表面研磨して平坦化する。

(もっと読む)

半導体装置の製造方法

【課題】製造過程の絶縁膜の剥離や飛散を抑制して半導体装置を歩留まり良く製造する。

【解決手段】ウェーハの上方に下地となる第1絶縁膜を介して第2絶縁膜を形成し(ステップS1,S2)、熱処理を行った後(ステップS3,S4)、その熱処理後の第2絶縁膜の一部を選択的に除去する(ステップS5)。熱処理の間、第1絶縁膜を第2絶縁膜で覆い、熱処理時の第1絶縁膜の剥離及び飛散を抑制する。

(もっと読む)

201 - 220 / 1,057

[ Back to top ]