Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

581 - 600 / 2,592

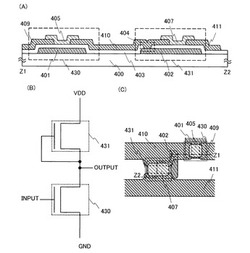

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグの上面の形状を工夫することにより、半導体装置の電気的特性において、信頼性の向上を図ることができる技術を提供する。

【解決手段】本願発明におけるプラグPLGは、上面がコンタクト層間絶縁膜CILの表面(上面)よりも突出した上に凸のドーム形状をしている。つまり、プラグPLGは、上面が上に凸のドーム形状となっており、コンタクト層間絶縁膜CILの上面の高さよりもバリア導体膜BF1の上端部の高さが高く、かつ、タングステン膜WFの上端部の高さはバリア導体膜BF1の上端部の高さよりも高くなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】配線構造に接続される低抵抗の貫通プラグ、または貫通プラグ及びコンタクトプラグを有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板1と、半導体基板1の表面近傍に埋め込まれた素子分離絶縁膜2と、素子分離絶縁膜2を貫通するように半導体基板1の裏面から表面まで貫通し、半導体基板1中で素子分離絶縁膜2に囲まれた領域を有する上段部101aと上段部101aよりも径が大きい下段部101bとを含む多段構造を有する貫通プラグ101と、貫通プラグ101の半導体基板1の表面側の端部に接続され、半導体基板1の表面側の上方に形成された電極パッド104と貫通プラグ101を接続するコンタクトプラグ103と、を有する。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】樹脂突起の成型時に導電膜に変形が生じ、導電膜が断線することを防止する。

【解決手段】まず、保護絶縁膜120上に選択的に硬化型の樹脂層を形成することにより、複数の外部接続端子それぞれのコアとなる複数の凸部202を形成する。次いで、凸部202を硬化させる前に、対向面22(表面)が平坦である成型用治具20を複数の凸部202の上面に押し付けることにより、複数の上面それぞれに平坦部を形成する。次いで、複数の凸部202を硬化させる。ついで、複数の凸部202、保護絶縁膜120、及び複数の電極パッド130上に導電膜を選択的に形成することにより、複数の外部接続端子、及び複数の配線を形成する。

(もっと読む)

半導体装置

【課題】レジストパターンの解像不良を引き起こす反応阻害物質を確実に除去することが可能なダマシン構造の半導体装置及びその製造方法の提供。

【解決手段】基板上に、少なくとも第1層間絶縁膜6及び低誘電率膜からなる第2層間絶縁膜4を有し、第2層間絶縁膜上に形成した第1レジストパターン1aを用いてビアホール9を形成し、アミン成分を含有する有機剥離液で有機剥離処理を行った後、続いて第2層間絶縁膜上に第2レジストパターン1bを形成する工程を含む半導体装置の製造方法であって、ウェット処理後、第2レジストパターン下層の第2反射防止膜2bを塗布する前に、アニール処理、プラズマ処理、UV処理又は有機溶媒処理の少なくとも一の処理を行い、露光時にレジスト中で発生する酸の触媒作用を阻害するアミン成分を除去して第2レジストパターン1bの解像度の劣化を防止する。

(もっと読む)

膜形成用組成物、絶縁膜および半導体装置

【課題】低誘電率で、かつ、強度に優れ、膜厚の不本意なばらつきが抑制された絶縁膜を提供すること、前記絶縁膜の形成に好適に用いることができる膜形成用組成物を提供すること、また、前記絶縁膜を備えた半導体装置を提供すること。

【解決手段】本発明の膜形成用組成物は、重合性の官能基を有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含むものであり、前記重合性化合物は、分子内に、アダマンタン型のかご型構造を含む部分構造Aと、重合反応に寄与する2つの重合性反応基とを有するものであり、前記重合性反応基は、芳香環と、当該芳香環に直接結合する2つのビニル基とを有するものであり、前記重合性化合物は、前記部分構造Aを中心に、前記重合性反応基が対称的に結合した構造を有するものである。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法を使用して配線を形成する半導体装置の製造技術において、信頼性の高い配線を形成する技術を提供する。

【解決手段】ハードマスク膜HM1上にハードマスク膜HM2が形成され、このハードマスク膜HM2上に有機樹脂膜ORFが形成された状態で、レジストCMPを実施する。これにより、ハードマスク膜HM2上に形成されている有機樹脂膜ORFが除去されるとともに、ハードマスク膜HM2の膜厚が膜減りする。その後、膜減りしたハードマスク膜HM2を除去し、露出したハードマスク膜HM1をマスクにしてトレンチを加工する。

(もっと読む)

半導体装置

【課題】グラフェンのバリスティック(弾道)伝導性を利用し、パターン形状によらず電気抵抗の上昇を抑えることができ、さらにエレクトロマイグレーションやストレスマイグレーション等のマイグレーションに対する耐性に優れた低抵抗配線を備えた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、配線層絶縁膜5中に形成されたシングルダマシン構造を有する配線10と、コンタクト層絶縁膜2中に形成され、上層の配線10と下層の導電部材1を電気的に接続するコンタクト3と、コンタクト層絶縁膜2と配線層絶縁膜5との間に形成されたエッチングストッパ膜4と、配線層絶縁膜5上に形成された拡散防止膜6と、を有する。配線10は、芯材14と、芯材14の底面および両側面に接するグラフェン層13と、グラフェン層13の底面および両側面に接する触媒層12と、触媒層12の底面および両側面に接する下地層11とを含む。

(もっと読む)

配線を形成する方法及び半導体装置の作製方法

【課題】生産性がよく、信頼性を向上した配線の作製方法とそれを用いた半導体装置の作製方法を提供する。

【解決手段】液滴吐出法によりゲート電極を形成する半導体装置の作製方法であって、基板上に半導体を形成し、半導体上にゲート絶縁膜を形成し、ゲート絶縁膜上に絶縁膜を形成し、絶縁膜にコンタクトホールを形成し、コンタクトホールにバリア膜として機能する金属膜をスパッタリング法または蒸着法により形成し、液滴吐出法により、コンタクトホールに銅からなる導電層をコンタクトホールを充填するように形成し、金属膜と導電層からなるゲート電極を形成する半導体装置の作製方法。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuバンプを形成可能とする半導体装置を提供する。

【解決手段】半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上に形成されるCuから成るスタッドバンプ26とを有する。

(もっと読む)

デバイスの製造方法及びデバイス

【課題】メモリ機能等を有する機能膜の水による劣化を防止すること。

【解決手段】成膜装置内で、機能膜が形成された基板上に、上記機能膜を覆うように、絶縁膜を形成する絶縁膜形成工程と、形成した上記絶縁膜の表面をプラズマに曝すプラズマ処理工程とを繰り返すこと。

(もっと読む)

半導体装置

【課題】半導体チップのサイズを縮小化することのできる技術を提供する。

【解決手段】まず、絶縁膜9上にパッド10およびパッド以外の配線11a、11bを設ける。このパッド10および配線11a、11b上を含む絶縁膜9上に表面保護膜12を形成し、表面保護膜12に開口部13を設ける。開口部13はパッド10上に形成されており、パッド10の表面を露出する。この開口部13を含む表面保護膜12上にバンプ電極8を形成する。ここで、バンプ電極8の大きさに比べてパッド10の大きさを充分小さくなるように構成する。これにより、バンプ電極8の直下であって、パッド10と同層に配線11a、11bが配置されるようにする。すなわち、パッド10を小さくすることにより形成されたバンプ電極8下のスペースに配線11a、11bを配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ14とを有し、前記Cuワイヤ14と前記Cu配線層9との間には合金層13が配置されることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】多層配線を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に第1配線用絶縁膜IM1を形成し、第1配線用絶縁膜IM1に配線溝TM1を形成する。その後、配線溝TM1に銅を主体とする導体膜を埋め込むことで配線MW1を形成する。続いて、配線MW1上にキャップ導体膜MC1を形成した後、キャップ導体膜MC1に表面研磨を施す。特に、キャップ導体膜MC1はALD法によって配線MW1上に選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】銅を用いた多層配線を有する半導体装置を高性能化する。

【解決手段】シリコン基板上に第1配線層用絶縁膜Z1を形成し、第1配線層用絶縁膜Z1に第1配線用孔部H1を形成する。その後、第1配線用孔部H1の側壁および底面を覆うようにして、タンタルまたはチタンを含む下部バリア導体膜eb1と、ルテニウムを主体とする上部バリア導体膜et1とからなる第1配線用バリア導体膜EM1を形成する。続いて、上部バリア導体膜et1をシード層として、電気めっき法により、銅を主体とする第1配線用導体膜EC1を形成し、CMP法により第1配線用導体膜EC1を第1配線用孔部H1に埋め込む。特に、上部バリア導体膜et1として、1〜5%の濃度で炭素を含ませるようにして、ルテニウムを主体とする導体膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】耐湿性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10の一主面11上に第1層層間絶縁膜14を設け、第1層層間絶縁膜14上に第1層台座181を有する第1配線層18を設け、第1配線層18上に第2層層間絶縁膜20を設け、第1層台座181上の第2層層間絶縁膜20にビアホール22を設け、第2層層間絶縁膜20上に第2層台座241を有する第2配線層24を設け、第2層台座241を第1層台座より大きくし、一主面11に垂直な方向からみた場合に、第1層台座全体181が第2層台座241の内側にあるようにする。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体デバイスのための電力グリッド構造体及びその製造方法

【課題】 半導体デバイスに電力を提供する電力グリッド構造体及びその製造方法を提供する。

【解決手段】 本発明の一実施形態は、誘電体層の内部に形成された第1の導電性材料のスタッドと、底部及び側壁を有する第2の導電性材料のビアであって、底部及び側壁は導電性ライナで覆われ、底部はスタッドの直接上に形成され、かつ、導電性ライナを通してビアと接触した状態にある、ビアと、ビアの側壁において導電性ライナを通してビアに接続する第3の導電性材料の1つ又は複数の導電性パスとを含むことができる半導体構造体を提供する。半導体構造体を製造する方法も提供される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

581 - 600 / 2,592

[ Back to top ]