Fターム[5F033HH20]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Mo (732)

Fターム[5F033HH20]に分類される特許

721 - 732 / 732

半導体装置の作製方法

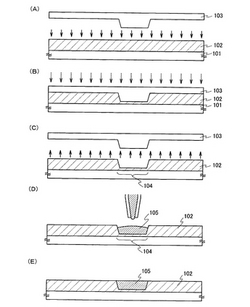

【課題】 より高精細なパターンの形成が可能な、液滴吐出法を用いた半導体装置の作製方法の提供を課題とする。

【解決手段】 パターンが形成されたモールドを絶縁膜に押し付けた状態で絶縁膜の硬化を行なった後、モールドを取り外すことで、絶縁膜に凹部を形成し、導電材料を有する液滴を吐出することにより、凹部に導電膜を形成し、導電膜を覆うようにゲート絶縁膜を形成し、ゲート絶縁膜上に島状の半導体膜を形成することを特徴とする半導体装置の作製方法。

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

補強された内部接続メタライゼーションを有するワイヤボンディングされた半導体部品

ドープされたシリコン基板製の半導体チップ2を含む半導体部品であって、前記チップは、半導体デバイスの中へドープされて構造化され、そして、コンタクトウインドウ中に内部接続メタライゼーション7を含み、前記半導体チップの前記内部接続メタライゼーションは、ワイヤボンド接続9によって、各外部接続メタライゼーションと接続され、前記内部接続メタライゼーションは、前記ドープされたシリコン基板上に開放格子構造体を有する補強システム8を含むことを特徴とする半導体部品。  (もっと読む)

(もっと読む)

金属−カルボニルプリカーサから金属層を堆積させる方法。

【課題】 金属−カルボニルプリカーサから金属層を堆積させる方法を提供することである。

【解決手段】 熱化学気相成長(TCVD)プロセスによって半導体基板上に金属層を堆積させる方法を提供する。TCVDプロセスは、金属層を堆積させるように金属−カルボニルプリカーサを含む希釈したプロセスガスの大流量を利用する。本発明の1つの実施形態では、金属−カルボニルプリカーサは、W(CO)6、Ni(CO)4、Mo(CO)6、Co2(CO)8、Rh4(CO)12、Re2(CO)10、Cr(CO)6、およびRu3(CO)12の少なくとも1つから選ばれることができる。本発明の別の実施形態では、約410℃の基板温度および約200mTorrのチャンバ圧力で、W(CO)6プリカーサを含むプロセスガスよりW層を堆積させる方法は、提供される。

(もっと読む)

製造方法

【課題】 基板内に導電性構造体を形成する方法を提供すること。

【解決手段】 表面上に多段階層構造体を形成する方法が記載される。この方法は、表面上に硬化可能な液体層を堆積させるステップと、内部に多層パターンを有するスタンプを液体層に圧入し、該パターンによって定められる多段階層構造体を該液体層内に生成するステップと、液体層を硬化させ、内部に多段階層構造体を有する固体層を生成するステップとを含む。機械的位置合わせを用いて、構造体を形成することになる基板上に離間配置された複数の突出部及びスタンプのパターン内の相補的陥凹部を介して、基板に対するスタンプの光学的位置合わせを強化することができる。

(もっと読む)

無電解堆積のエンドポイントを検出するための装置および方法

基板の表面に向けて電磁放射を方向付けて、該基板の該表面上の部材から反射された該電磁放射の強度の変化を1つ以上の波長で検出することによって無電解堆積プロセスをコントロールするための装置および方法。一実施形態において、該基板が検出機構に対して移動されると、無電解堆積プロセスステップの検出された終了が測定される。別の実施形態において、多数の検出ポイントが、該基板の該表面にわたる該堆積プロセスの状態を監視するために使用される。一実施形態において、該検出機構は該基板上で無電解堆積流体に浸される。一実施形態において、コントローラは、記憶されたプロセス値、異なる時間に収集されたデータの比較、および種々の算出された時間依存データを使用して無電解堆積プロセスを監視、記憶および/またはコントロールするために使用される。 (もっと読む)

液晶表示装置の製造方法

アクティブマトリクス型液晶表示装置の薄膜トランジスタにおける下地電極上の絶縁膜上にフォトエンボッシング材料を用いて凹凸を有する有機膜を形成し、この有機膜にドライエッチングを施して有機膜の膜厚を減少させてコンタクトホール形成領域の絶縁膜を露出させる。その後、露出した絶縁膜にドライエッチングを施してコンタクトホールを形成すると共に下地電極を露出させ、得られた構造上に反射電極を形成して、露出した下地電極と反射電極とを接続する。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

半導体基板上の、超臨界流体による物質の蒸着

集積回路デバイス製造のための半導体基板のような基板上への、超臨界流体を利用した物質の蒸着。蒸着は、基板表面に蒸着される物質の前駆体を含む、超臨界流体をベースとする組成物を使用して行われる。そのようなアプローチにより、気相蒸着工程に必要な揮発性および搬送性がないために、蒸着への適用には全く不適切であった前駆体の使用が可能になる。 (もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

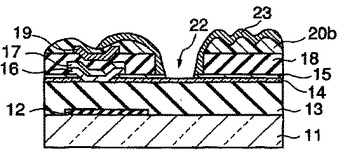

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

721 - 732 / 732

[ Back to top ]