Fターム[5F033HH22]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | 高融点金属の合金 (485)

Fターム[5F033HH22]の下位に属するFターム

TiW (366)

Fターム[5F033HH22]に分類される特許

81 - 100 / 119

表示装置及びその作製方法

【課題】表示装置において、低抵抗材料を配線に用いることが望まれてきたが、これまでは、有効な配線形成の手段が存在しなかった。

【解決手段】第1の導電膜を形成し、第1の導電膜上に選択的にレジストを形成し、第1の導電膜及びレジスト上に第2の導電膜を形成し、レジストを除去すると共にレジスト上に形成された第2の導電膜を除去し、第1の導電膜上に形成された第2の導電膜を覆うように第3の導電膜を形成し、第1の導電膜及び第3の導電膜を選択的にエッチングし、複数の配線及び電極を形成する。これにより、大型パネルに低抵抗材料を用いた配線を形成することができるため、信号遅延等の問題を解決できる。

(もっと読む)

基板装置の製造方法

【課題】歩留まりの低下を防止したアレイ基板の製造方法を提供する。

【解決手段】第1層間絶縁膜17とゲート絶縁膜14とを貫通してコンタクトホール19を形成する。コンタクトホール19を通して活性層5のドレイン領域13と電気的に接続するドレイン電極22を形成する際に、薄膜トランジスタおよび第1層間絶縁膜17を含む絶縁性基板3の温度が120℃以上の状態でスパッタリングして活性層5と接触するようにバリアメタル膜26を形成する。バリアメタル膜26上に形成した導電膜25とともにドライエッチングする。バリアメタル膜26の結晶粒径を大きくして第1層間絶縁膜17の括れ部分にバリアメタル膜26を形成することを防止し、ドライエッチング後の残渣の発生を防止して、残渣によるショートなどでの歩留まりの低下を防止できる。

(もっと読む)

半導体装置およびその作製方法

【課題】工程数を増やすことなく、段切れ不良、及びコンタクト不良を防ぐ方法を提供し、それにより動作性能および信頼性の高い集積回路を作製することを課題とする。

【解決手段】配線の乗り越え部分において、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを配線形成用のフォトリソグラフィ工程に適用し、2層構造の下層配線となる導電層を形成し、下層配線が下層配線1層目と、1層目の幅より短い2層目の幅を有するようにレジストパターンを形成し、急峻な段差を緩和することを目的とした下層配線を形成する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】工程時間を短縮でき、不良発生率を減少させて生産効率を高めることができる液晶表示装置及びその製造方法を得る。

【解決手段】基板100上の非表示領域に形成された、第1多結晶半導体と第1ゲート電極と第1ソース電極と第1ドレイン電極を有するp型の駆動薄膜トランジスタ、第2多結晶半導体と第2ゲート電極と第2ソース電極と第2ドレイン電極を有するn型の駆動薄膜トランジスタと、基板上100の表示領域に形成された、相互に交差して画素領域を定義するゲート配線GLとデータ配線DLと、第3多結晶半導体パターンと第3ゲート電極と第3ソース電極と第3ドレイン電極を有する画素薄膜トランジスタと、前記第3ドレイン電極を上から覆う画素電極170と、前記第1ソース電極及びドレイン電極と前記第2ソース及び第2ドレイン電極を上から覆う遮断パターンと、前記データ配線と前記第3ソース電極を上から覆う遮断配線173を含む。

(もっと読む)

配線、これを含む薄膜トランジスタ基板、及びその製造方法

【課題】 配線、これを含む薄膜トランジスタ基板、及びその製造方法が開示される。

【解決手段】 本発明の一実施例による配線は、下部構造物上に形成されたバリア膜、前記バリア膜上に形成された銅又は銅合金を含む銅導電膜、前記銅導電膜上に形成された中間膜、及び前記中間膜上に形成されたキャッピング膜を含むか、又は下部構造物上に形成されたバリア膜、前記バリア膜上に形成された第1中間膜、前記第1中間膜上に形成された銅又は銅合金を含む銅導電膜、前記銅導電膜上に形成された第2中間膜、及び前記第2中間膜上に形成されたキャッピング膜を含む。

(もっと読む)

半導体装置及びその製造方法並びに電子装置

【課題】 外部基板へ実装した際に、接続不良を低減できる半導体装置を提供する。

【解決手段】 本発明に係る半導体装置1は、一面に電極を配してなる半導体基板2と、 半導体基板1の一面を覆うように配され、かつ、前記電極が露呈するように開口部を有すると共に、厚さが異なる部分を有する中間層21と、中間層21を覆い、外部基板との接続領域に配された第一導電部6A、6aと、前記開口部を通して前記電極と第一導電部6A、6aとを電気的に接続する第二導電部と、第一導電部6A、6aに接合されるバンプ9A、9aと、を少なくとも備え、第一導電部6A、6aが配された中間層21の厚さに応じて体積の異なるバンプ9A、9aを有する。図1に示す構成例は、第一中間層4に第二中間層5を重ねた厚い中間層21上に配されるバンプ9Aが、第一中間層4のみからなる薄い中間層21上に配されるバンプ9aに比べて、小さな体積を有する場合を示す。

(もっと読む)

表示装置及び表示用薄膜半導体装置

【課題】薄膜トランジスタの活性層となる半導体薄膜のレーザアニールによる再結晶化処理を均一化及び最適化するとともに、ゲート配線の低抵抗化を図る。

【解決手段】表示装置は、各薄膜トランジスタ4のゲート電極1を互いに接続するゲート配線6と、各薄膜トランジスタ4のソース電極Sを互いに接続する信号配線7とが絶縁基板上で互いに交差する様に形成されている。ゲート配線6は、個々のゲート電極1と一体的に形成された一体部6aと、これらを互いに接続する別体部6bとに分かれている。ゲート電極1はゲート配線6の別体部6bより低い熱伝導性を有し、ゲート配線6の別体部6bはゲート電極1より低い電気抵抗を有する。信号配線7とゲート配線6の一体部6aとが絶縁膜14をはさんで交差する。

(もっと読む)

半導体装置およびその作製方法

【課題】幅の異なるLDD領域を自己整合的に形成し、それらの幅を個々の回路に応じて精密に制御する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いることによって、ゲート電極の膜厚の薄い領域の幅を自由に設定でき、そのゲート電極をマスクとして自己整合的に形成できる2つのLDD領域の幅を個々の回路に応じて異ならせることができる。なお、一つのTFTにおいて、幅の異なる2つのLDD領域は、両方ともゲート電極と重なる構造である。

(もっと読む)

薄膜トランジスター基板及びその製造方法

【課題】フレキシブル基板を用いた液晶表示装置の製造工程に際し、基板の膨張及び収縮による誤整列に備えることを可能にする。

【解決手段】ベース基板110上に形成されたゲートライン120と、ゲートラインと絶縁されて形成されたデータライン、及びゲートラインとデータラインとが交差する領域に形成され、ゲートラインの線幅は少なくとも前記データラインの線幅よりも大きく形成される薄膜トランジスターと、を備え、データラインは、前記ゲートラインと絶縁されて交差する第1のデータライン160a、160cと、第1のデータラインと交差し、その一端が第1のデータラインと電気的に接続される第2のデータライン160bと、を備え、薄膜トランジスターのドレイン電極170は、データラインと所定の間隔だけ離して配置されることを特徴とする。

(もっと読む)

電子基板の製造方法及び電気光学装置の製造方法並びに電子機器の製造方法

【課題】製造コストを抑えつつ、高精度の電子素子を形成できる電子基板の製造方法および電気工学装置の製造方法並びに電子機器の製造方法を提供する。

【解決手段】配線パターンを有する基板Pに対してマスク22を貼着する工程と、マスク22の開口部22aを介して配線パターンの一部を除去して抵抗素子を形成する工程とを備える。マスク22は、基板Pに貼着される第1フィルム材22Aと、第1フィルム材22Aに剥離可能に貼り合わされる第2フィルム材22Bとを有する。マスク22の所定領域に開口部22aを形成し、開口部22aが形成されたマスク22を負圧環境下で基板Pに貼着する。

(もっと読む)

エッチング液、これを用いた配線形成方法及び薄膜トランジスタ基板の製造方法

【課題】モリブデン/銅/窒化モリブデン多重膜配線用エッチング液を提供すること。また、前記エッチング液を利用する配線形成方法を提供すること。さらに、前記エッチング液を利用する薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】エッチング液、これを利用する配線形成方法及び薄膜トランジスタ基板の製造方法が提供される。モリブデン/銅/窒化モリブデン多重膜配線用エッチング液は過酸化水素10ないし20重量%、有機酸1ないし5重量%、トリアゾール系化合物0.1ないし1重量%、ふっ素化合物0.01ないし0.5重量%及び残量の超純水を含む。

(もっと読む)

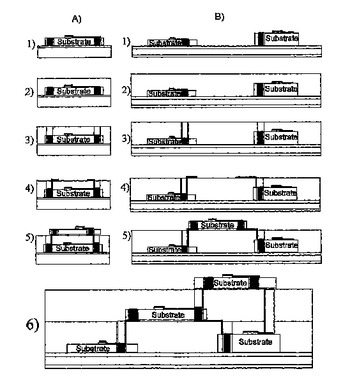

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

多層薄膜、並びに該多層薄膜を有する薄膜トランジスタ及び薄膜トランジスタ表示板の製造方法

【課題】薄膜トランジスタの特性及び表示装置の性能を向上させる。

【解決手段】基板41上に多結晶シリコン膜42が形成され、その上に多結晶シリコン膜の表面を露出させるコンタクトホール44を有する絶縁膜43が形成されている。該絶縁膜上には、非晶質シリコン膜45及び導電膜46を有するゲート線が形成され、コンタクトホールを介して多結晶シリコン膜42と接続している。また、ゲート線上に絶縁膜とデータ線が形成されている。このように、非晶質シリコン膜45を設けて側面傾斜を多様にし、基板を熱処理して導電膜46と非晶質シリコン膜45の間の接着力を向上させることで、接触抵抗を低減することができ、薄膜トランジスタの特性及び信頼性が向上される。

(もっと読む)

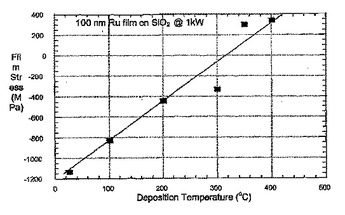

ルテニウム系材料およびルテニウム合金

本明細書には、ルテニウムおよび元素周期表のIV族、V族、もしくはVI族の元素の少なくとも1つの元素またはこれらの組合せが含まれる、蒸着法または原子層堆積法において用いるための合金が記載される。また、本明細書には、ルテニウム系材料またはルテニウム系合金を含む少なくとも1つの層、および元素周期表のIV族、V族、もしくはVI族の元素の少なくとも1つの元素またはそれらの組合せを含む少なくとも1つの層が含まれる積層材料が記載される。  (もっと読む)

(もっと読む)

金属表面の粗面化処理方法

【課題】チタン、チタン合金、アルミニウム、アルミニウム合金およびステンレスを溶液に浸漬させて、短時間に腐食量が少なく、あらゆる複雑な形状のチタン、チタン合金、アルミニウム、アルミニウム合金およびステンレスを表面粗さ2〜20μmに、歪みなく、粗面化する処理方法を提供することにある。

【解決手段】 チタン、チタン合金、アルミニウム、アルミニウム合金およびステンレスを、弗化水素の濃度0.5〜60重量%の弗酸に増粘剤を加え、粘度1000〜1560000mPa・sにした溶液(液温が0〜60℃)中に浸漬することによって、チタン、チタン合金、アルミニウム、アルミニウム合金およびステンレス表面を粗面化する処理方法を提供する。

(もっと読む)

平坦な表面における誘電体エッチング停止を用いて誘電体オーバーエッチングを低減するための方法

実質的に平坦な表面が、導電性フィーチャまたは半導体フィーチャと誘電体エッチング停止材料とを同時露出させる。誘電体エッチング停止材料とは異なる第2の誘電材料を、実質的に平坦な表面上に堆積する。選択的なエッチングによって、第2の誘電材料に孔または溝をエッチングして、エッチングが導電性フィーチャまたは半導体フィーチャおよび誘電体エッチング停止材料上で停止するようにする。好ましい実施形態において、実質的に平坦な表面は、導電性フィーチャまたは半導体フィーチャの間のギャップに酸化物のような第1の誘電体を満たし、酸化物を窪ませ、窒化物のような第2の誘電体を満たし、その後、窒化物と導電性フィーチャまたは半導体フィーチャとを同時露出させるように平坦化することにより形成される。  (もっと読む)

(もっと読む)

銅配線層、銅配線層の形成方法、半導体装置、及び半導体装置の製造方法

【課題】広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な銅配線層の形成方法を提供すること。

【解決手段】基板上に銅シード層のパターンを形成する工程、及び前記銅シード層のパターン上に銅配線層を無電解めっき法で形成する工程を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜トランジスタの静電破壊を抑制することができ、信頼性を高めた半導体装置およびその製造方法を提供する。

【解決手段】複数の薄膜トランジスタ100により回路が形成された半導体装置であって、複数の薄膜トランジスタ100に共通接続されたゲート配線22が分割されており、分割されたゲート配線22同士が、ゲート配線22よりも上層に配置された接続配線29により電気的に接続されている。

(もっと読む)

1ないし5nmの厚さの金属キャップを用いる改良されたオンチップCu相互接続

【課題】 1から5nmの厚さの金属キャップを用いた改良されたオンチップCu相互接続を提供する。

【解決手段】 開示されているのは、層間の誘電体又は誘電体拡散障壁層の堆積に先立って、1から5nmの厚さの元素でCuダマシン配線の表面をコーティングする手順である。そのコーティングは、酸化に対する防御をもたらし、Cuと誘電体の間の密着力を増し、そしてCuの界面拡散を減少させる。さらに、その薄いキャップ層はCuのエレクトロマイグレーション寿命を増し、応力により誘起されたボイド発生を減らす。選択された元素は、Cu配線間のショートを引き起こすことなしに、下層の誘電体中に埋込まれたCuの上に直接堆積することができる。これらの選ばれた元素は、酸素及び水に関する負の高い還元電位と、Cuへの低い溶解度、及びCuとの化合物形成に基づいて選ばれている。

(もっと読む)

微細加工処理剤、及びそれを用いた微細加工処理方法

【課題】 タングステン膜及びシリコン酸化膜の積層膜に対して、エッチレートを制御して微細加工処理をすることが可能な微細加工処理剤、及びそれを用いた微細加工処理方法を提供する。

【解決手段】 本発明の微細加工処理剤は、フッ化水素及び硝酸を含み、基板上に積層されたタングステン膜及びシリコン酸化膜を微細加工する微細加工処理剤であって、前記タングステン膜に対する25℃でのエッチレートが0.5〜5000nm/分の範囲内であり、且つ、前記シリコン酸化膜に対する25℃でのエッチレートが、前記タングステン膜に対する25℃でのエッチレートの0.5〜2倍の範囲内であることを特徴とする。

(もっと読む)

81 - 100 / 119

[ Back to top ]