Fターム[5F033HH22]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | 高融点金属の合金 (485)

Fターム[5F033HH22]の下位に属するFターム

TiW (366)

Fターム[5F033HH22]に分類される特許

101 - 119 / 119

微細加工処理剤、及びそれを用いた微細加工処理方法

【課題】 タングステン膜及びシリコン酸化膜の積層膜に対して、エッチレートを制御して微細加工処理をすることが可能な微細加工処理剤、及びそれを用いた微細加工処理方法を提供する。

【解決手段】 本発明の微細加工処理剤は、フッ化水素及び硝酸を含み、基板上に積層されたタングステン膜及びシリコン酸化膜を微細加工する微細加工処理剤であって、前記タングステン膜に対する25℃でのエッチレートが0.5〜5000nm/分の範囲内であり、且つ、前記シリコン酸化膜に対する25℃でのエッチレートが、前記タングステン膜に対する25℃でのエッチレートの0.5〜2倍の範囲内であることを特徴とする。

(もっと読む)

半導体装置およびその作製方法、並びに電子機器

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

トランジスタおよびその作製方法、並びに半導体装置

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

薄膜蝕刻方法及びこれを用いた液晶表示装置の製造方法

【課題】フェムト秒レーザーを用いて薄膜を蝕刻することによって工程の単純化及び生産性の向上が図られる薄膜蝕刻方法及びこれを用いた液晶表示装置の製造方法を提供する。

【解決手段】基板上に薄膜を形成する段階と、この薄膜上部にパターン形状が定義されたマスクを整列する段階と、このマスクに定義されたパターン形状を有するように前面にフェムト秒レーザーを照射して薄膜を選択的に除去する段階とを備える。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

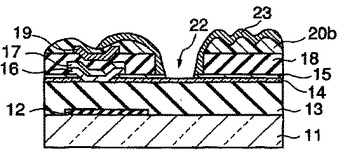

半導体装置及びその製造方法

【課題】 本発明は、貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10上に第1の絶縁膜11を介して形成されたパッド電極12上に、高融点金属層13を形成する。次に、パッド電極12及び高融点金属層13上を含む半導体基板10の表面上にパッシベーション層14を形成し、さらに、樹脂層15を介して支持体16を形成する。次に、半導体基板10をエッチングして、半導体基板10の裏面からパッド電極12に到達するビアホール17を形成する。次に、第2の絶縁膜18を介して、ビアホール17の底部で露出されたパッド電極12と電気的に接続された貫通電極20及び配線層21を形成する。さらに、ソルダーレジスト層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

電気光学装置の製造方法

【課題】外部接続用配線の要素であるクロム層とITO層との間のコンタクト抵抗を低く維持し、駆動用ICが誤動作するのを防止する。

【解決手段】TFD素子の第1金属膜及び外部接続用配線の第1導電層を夫々クロムにて形成し、次にその上に酸化タンタルを形成する。次に、アニール処理Aを約300℃(保持時間60分)で実行する。次に、第2金属膜を形成し、その直後に、データ線及びTFD素子の上にオーバーレイヤーを形成する。これにより、TFD素子の第2金属膜の表面及び外部接続用配線の第1導電層の表面に酸化膜が形成されるのを防止できる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 抵抗が低く、画素電極または半導体層との接触性が優れた配線を有する薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】 本発明は、液晶表示装置または有機発光表示装置用薄膜トランジスタ表示板の配線に関し、モリブデン(Mo)にニオビウム(Nb)、バナジウム(V)またはチタニウム(Ti)を所定量含むモリブデン合金層とアルミニウム層の積層構造を形成することによって、既存の純粋モリブデン(Mo)を使用した場合に比べて、モリブデン合金層とアルミニウム層の相対的なエッチング速度の差が減少し、エッチング工程時におけるアンダーカット、オーバーハング及びマウスバイトなどが発生しない。更に、半導体層または画素電極との接触特性も改善されたことを特徴とする低抵抗性及び耐薬品性を同時に有する薄膜トランジスタ表示板及びその製造方法である。

(もっと読む)

積層金属膜のパターン構造及びパターン形成方法並びに該積層金属配線を備える液晶表示装置又は半導体装置

【課題】ウェットエッチングによる積層金属膜のエッチング速度の面内ばらつきを低減し、所望のテーパー形状を得ることができる積層金属膜のパターン構造及びパターン形成方法並びに液晶表示装置または半導体装置の提供。

【解決手段】Al又はAl合金とMo又はMo合金などのバリア金属膜とからなる積層金属膜(好ましくは卑金属側が下層に存在するような積層金属膜)をウェットエッチング法で一括エッチング処理してパターン形成する場合において、製品素子領域に配線パターンを形成すると共に、非製品素子領域のエッチング開口部にも任意の微細パターンを形成し、製品素子領域及び非製品素子領域双方のエッチング開口部全域の電池反応を促進させ、エッチング速度の面内分布を均一化させる。これにより、積層金属配線の断面形状を良好なテーパー形状として、製品の歩留まりや長期信頼性を向上させる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】水素の触媒作用によるコンタクトプラグ不良を防止する。

【解決手段】ソース領域、ドレイン領域およびゲートからなるトランジスタが集積化された半導体基板上に、前記ソース領域またはドレイン領域に接続されたコンタクトプラグと、前記コンタクトプラグに接続された下部電極と、前記下部電極の間に埋め込まれた酸素バリアを有する絶縁膜と、前記容量絶縁膜に形成された上部電極からなる強誘電体キャパシタにおいて、前記下部電極が酸素に対する導電性バリアを含み、さらに前記下部電極と絶縁膜との間に前記下部電極との反応を防止するための絶縁性反応防止膜を備えた構造になっている。

(もっと読む)

電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置

【課題】 電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置を提供する。

【解決手段】 層を別にして交互される二層以上の導電層を含む電子装置において、導電層のうち、少なくとも何れか一層は、長手方向に沿って幅を別にする幅変動部を備えるが、幅変動部は、隣りの導電層との非交差部に形成されることを特徴とする薄膜トランジスタ構造体。また、基板の一面上に形成される薄膜トランジスタ層と、薄膜トランジスタ層と電気的疎通をなす一つ以上の画素を備える画素層と、を含み、薄膜トランジスタは、層を別にして交互される二層以上の導電層を含み、導電層のうち少なくとも何れか一層は、長手方向に沿って幅を別にする幅変動部を備えるが、幅変動部は、隣りの導電層との非交差部に形成されることを特徴とする平板ディスプレイ装置。

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度に優れると共に、低抵抗であって且つ絶縁膜に対する密着性の高いバリアメタル膜を有する半導体装置を提供する。

【解決手段】 基板(1)上に形成された絶縁膜(6)と、絶縁膜(6)中に形成された埋め込み金属配線(10)と、絶縁膜(6)と金属配線(10)との間に形成されたバリアメタル膜(A1)とを備えた半導体装置において、バリアメタル膜(A1)は、絶縁膜(6)が存在している側から金属配線(10)が存在している側へ向かって順に積層されている金属酸化物膜(7)、金属化合物膜(8)及び金属膜(9)よりなる。金属化合物膜(8)の弾性率は、金属酸化物膜(7)の弾性率よりも大きい。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた平板表示装置及びその平板表示装置の製造方法

【課題】 薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた平板表示装置及びその平板表示装置の製造方法を提供する。

【解決手段】 チャンネル領域、ソース、及びドレイン領域を有する活性層と、前記チャンネル領域に信号を印加するゲート電極と、前記ソース及びドレイン領域にそれぞれ接続し、Ti、Ti合金、Ta、及びTa合金のうち少なくとも一つを含むソース及びドレイン電極と、前記ソース及びドレイン電極と前記活性層との間に介在され、シリコンナイトライドを含む絶縁膜と、を含むことを特徴とする薄膜トランジスタ。これにより、ソース/ドレイン電極の配線抵抗を低め、活性層からの汚染を防止し、画素電極との接触抵抗特性が改善され、活性層への水素供給を円滑にして移動度、オンカレント特性、スレショルド電圧特性などに優れたTFT及びそれを備えた平板表示装置が得られる。

(もっと読む)

薄膜トランジスタの作製方法

【課題】 しかし、薄膜トランジスタを有する表示装置では、同一対象物、例えば同一絶縁膜のエッチング条件を最適化することが難しかった。これは、同一絶縁膜において、エッチングする絶縁膜の膜厚や面積が異なるためである。特に面積の小さなコンタクトホールは、エッチングする量がその他の開口部と異なる。

【解決手段】 上記課題を鑑み本発明は、第1のマスクを用いて、第1の領域の対象物をエッチングして広面積な開口部を形成し、第2のマスクを用いて、第2の領域の前記対象物をエッチングして微細な開口部、つまりコンタクトホールを形成することを特徴とする。

(もっと読む)

半導体装置の製造方法とこの方法により得られる半導体装置

この発明は、仮基板(2)を有する半導体基体(1)内において、少なくとも一つの半導体素子(3)が形成され、半導体素子(3)が、半導体基体(1)の基板(2)とは反対側に少なくとも一つの接続領域(4)を備え、そして、前記側に誘電体(5)が形成され、そして、接続領域(4)を露出させるようにパターンニングされ、その後、接続領域(4)と接続するように誘電体(5)上部に金属層(6)が堆積され、金属層(6)が接続領域(4)の電気的接続導電体として機能し、その後、仮基板(2)が除去され、そして、金属層(6)が半導体装置(10)の基板として機能する半導体装置(10)の製造方法に関する。この発明によれば、金属層(6)が堆積される前に、誘電体(5)のパターンニングされた部分の周囲と半導体素子(3)の周囲とに誘電体(5)よりも厚い樹脂のリング状領域(7)が形成され、そして、長方形のリング状領域(7)内部に金属層(6)が堆積される。このようにして、金属層(6)が堆積された後に、好ましくは、装置(10)を領域(7)外部に押圧することにより各装置(10)が容易に形成できる。好ましくは、誘電体(5)と領域(7)とのために(異なる)フォトレジストが選ばれる。この発明は、さらに、このようにして得られる半導体装置(10)を備える。  (もっと読む)

(もっと読む)

電気光学装置の製造方法、電気光学装置、及び電子機器

【課題】 良好な素子特性を有する非線形素子を備え、もって高画質表示を可能にした電気光学装置を歩留まりよく製造する方法を提供する。

【解決手段】 基板上に、第1導電層と絶縁層と第2導電層とを積層してなる非線形素子と、該非線形素子から延出されたコンタクト部と、前記非線形素子およびコンタクト部を覆う層間絶縁膜と、前記コンタクト部と電気的に接続された画素電極とを具備した電気光学装置の製造方法であって、本線部106bとコンタクト部36を迂回する支線部106aとを有する金属膜106をパターン形成する工程と、前記金属膜106を陽極酸化処理することにより前記金属膜106上に酸化膜からなる絶縁層を形成する工程と、前記支線部106aの先端部を残して前記金属膜106を除去し、前記第1導電層および導電層を形成する工程と、前記絶縁層上に前記第2導電層およびコンタクト部36を形成する工程とを含む製造方法とした。

(もっと読む)

液晶表示装置の製造方法

アクティブマトリクス型液晶表示装置の薄膜トランジスタにおける下地電極上の絶縁膜上にフォトエンボッシング材料を用いて凹凸を有する有機膜を形成し、この有機膜にドライエッチングを施して有機膜の膜厚を減少させてコンタクトホール形成領域の絶縁膜を露出させる。その後、露出した絶縁膜にドライエッチングを施してコンタクトホールを形成すると共に下地電極を露出させ、得られた構造上に反射電極を形成して、露出した下地電極と反射電極とを接続する。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

101 - 119 / 119

[ Back to top ]