Fターム[5F033KK06]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 半導体(基板を除く) (1,188) | 単結晶Si (33)

Fターム[5F033KK06]に分類される特許

1 - 20 / 33

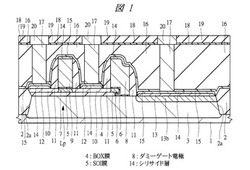

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

基板のエッチング方法及びシステム

【課題】シリコンの表面上にシリコン酸化膜が形成された基板をエッチングする方法において、コンタクト抵抗を低くできるエッチング方法を提供する。

【解決手段】ハロゲン元素を含むガス、及び塩基性ガスを基板W上に供給し、シリコン酸化膜にハロゲン元素を含むガス及び塩基性ガスを化学反応させた凝縮層105を生成して、シリコン酸化膜104をエッチングする。F2ガス、XeF2ガス及びClF3ガスの群から選ばれる少なくとも一つを含むシリコンエッチングガスを基板W上に供給し、シリコンエッチングガスによって基板W上のシリコンをエッチングする。シリコン酸化膜104のエッチング及びシリコンのエッチングの後、基板W上の凝縮層105を加熱して除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増大を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散領域101aを表面に有する半導体基板100と、半導体基板100を覆う層間絶縁膜107と、層間絶縁膜107上に形成され、拡散領域109aを表面に有する半導体層108と、層間絶縁膜107および半導体層108を貫通する貫通口119a内に形成され、拡散領域101aに接し、且つ側面の一部が拡散領域109aに接するソース線プラグ116aと、ソース線プラグ116aと層間絶縁膜107との間に介在し、且つソース線プラグ116aが拡散領域109aと接する部分を除いてソース線プラグ116aと半導体層108との間に介在する側壁絶縁膜117aと、を具備する。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、マンガン(Mn)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でMnが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、ニッケル(Ni)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でNiが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

縦型電界効果トランジスタを備える半導体装置及びその製造方法

【課題】縦型電界効果トランジスタを利用した半導体装置において、集積度を更に向上させること。

【解決手段】半導体装置1は、絶縁性基板10と、絶縁性基板10上に形成された第1導電型の第1半導体層21と、第1半導体層21上にソース及びドレインの一方が形成された第1導電型チャネルの第1縦型電界効果トランジスタNFETと、絶縁性基板10上に形成された第2導電型の第2半導体層22と、第2半導体層22上にソース及びドレインの一方が形成された第2導電型チャネルの第2縦型電界効果トランジスタPFETと、を備える。第1半導体層21と第2半導体層22は、直接接触している。

(もっと読む)

半導体装置およびその製造方法

【課題】TFTに接続された各配線を形成する際のプラズマエッチング工程においてチャージアップに起因するプラズマダメージが生じることを防止する。

【解決手段】TFT10のソース領域13sに接続されたソース配線17s、TFT10のドレイン領域13dに接続されたドレイン配線17d、およびTFT10に対して電気的に接続されない配線18を共通のプラズマエッチング工程によって形成する際、ソース配線17sとドレイン配線17dとの間隔を、ソース配線17sと配線18との間隔およびドレイン配線17dと配線18との間隔よりも狭くする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新たなレイアウトパターンを作成せずにNMOSの駆動力を向上することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板100と、第1の導電型の第1の半導体素子が設けられる半導体基板100に形成される第1の半導体素子領域と、第2の導電型の第2の半導体素子が設けられる半導体基板100に形成される第2の半導体素子領域と、第1の半導体素子領域と第2の半導体素子領域とを分離する素子分離領域120とを備え、第1の半導体素子領域は、第1の半導体素子領域に隣接する素子分離領域120より高い位置に形成され、素子分離領域120の表面からの第1の半導体素子領域の表面までの距離が、第1の半導体素子領域の上面視における幅以下である。

(もっと読む)

半導体装置、および、その製造方法

【課題】フィンの数に応じた電流比で電流を流す場合に、その電流比の精度を向上させる。

【解決手段】第1のfinFET100と、第2のfinFET200と、第3のfinFET300とについて、ドレイン電流の値に応じてフィンの数を増加させるが、第1のfinFET100と、第2のfinFET200と、第3のfinFET300とのそれぞれにおいて、一対のソース・ドレイン領域に接続させるコンタクトを同一の数にする。

(もっと読む)

半導体装置

【課題】大型絶縁基板に非単結晶Si半導体素子と単結晶Si半導体素子とを形成し、高性能なシステムを集積化した半導体装置を製造する場合に、単結晶Si部分の製造工程を簡略化し、かつ大型絶縁基板に転写した後、高精度のフォトリソグラフィなしに微細な単結晶Si半導体素子の素子分離を実現し得る半導体基板、半導体装置、及びそれらの製造方法を提供する。

【解決手段】チャネル領域17、ソース領域4及びドレイン領域5を含む活性層6を有し、ウエル構造及びチャネルストップ領域を有しない単結晶Siウエハ8と、単結晶Siウエハ8上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極2と、活性層6の周囲の単結晶Siウエハ8上に形成された、ゲート絶縁膜3よりも膜厚の厚いLOCOS酸化膜7と、ゲート電極2及びLOCOS酸化膜7上に形成された平坦化絶縁膜1を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を提供することを課題とする。

【解決手段】多階調マスクを用いることで1つのフォトレジスト層を1枚のマザーガラス基板から遠ざかる方向に向かって断面積が連続的に減少するテーパ形状を有するフォトレジスト層を形成する。1本の配線を形成する際、1枚のフォトマスクを用い、金属膜を選択的にエッチングすることで、場所によって側面形状(具体的には基板主平面に対する角度)が異なる1本の配線を得る。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域をシリサイド化しても、リーク電流を可及的に抑えることを可能にする。

【解決手段】半導体領域7を有するシリコン基板2と、半導体領域に離間して形成されたソース/ドレイン領域11a、15a、11b15bと、ソース領域とドレイン領域との間の半導体領域上に形成された絶縁膜9aと、絶縁膜上に形成されたゲート電極10aと、ゲート電極の側部に形成された側壁絶縁膜13aと、第1ソース/ドレイン領域上に形成され、少なくとも{111}面となる表面を有する単結晶シリコン層17a、17bと、少なくとも単結晶シリコン層の{111}面上に形成され、かつ側壁絶縁膜に接する部分を有し、この部分と単結晶シリコン層との界面が単結晶シリコン層の{111}面であるNiSi層21a、21bと、NiSi層に接する第1のTiN膜23a、23bと、を有する第1のMOSFETと、を備えたことを特徴とする。

(もっと読む)

低コンタクト抵抗を示すMOS構造およびその形成方法

低コンタクト抵抗を示すMOS構造(100,200)と、このようなMOS構造の形成方法が提供される。一方法では、半導体基板(106)が提供され、前記半導体基板上にゲートスタック(146)が形成される。前記半導体基板内に、前記ゲートスタックと整合された不純物ドープ領域(116)が形成される。前記不純物ドープ領域から延びる隣接するコンタクトフィン(186)が形成され、前記コンタクトフィン上に金属シリサイド層(126)が形成される。前記コンタクトフィンの少なくとも1つに存在する前記金属シリサイド層の少なくとも一部に対するコンタクト(122)が形成される。  (もっと読む)

(もっと読む)

表示装置およびスパッタリングターゲット

【課題】バリアメタル層の省略を可能にすると共に、工程数を増やすことなく簡略化し、Al合金膜を導電性酸化膜に対し直接且つ確実に接触することだけでなく、Al合金膜に対し、比較的低い熱処理温度を適用した場合でも、電気抵抗率を低減でき、且つ導電性酸化膜と直接接触したときの接触電気抵抗も低減でき、更には優れた耐熱性と耐食性を達成することのできる技術を提供する。

【解決手段】Al合金膜の上に導電性酸化膜が直接接触する構成を備えた表示装置において、該Al合金膜が、Niを0.05〜2.0原子%と、Inおよび/またはSnを合計で0.05〜1.0原子%含有するように調整する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】 本発明は、半導体層あるいは画素電極との密着性が高い酸化被膜を形成して、配線材料等の酸化を防止できると共に、導電率が高いソース電極あるいはドレイン電極を備えた液晶表示装置及びその製造方法を提供することにある。

【解決手段】 本発明では、液晶表示装置を構成するTFT基板上のTFT電極において、ソース電極あるいはドレイン電極が、銅を主体とした層と、該銅を主体とした層を被覆する酸化物からなることを特徴とする。さらに、本発明は、前記TFT電極において、半導体層あるいは画素電極と、前記ソース電極あるいはドレイン電極とが、オーミック接合していることを特徴とする。

(もっと読む)

1 - 20 / 33

[ Back to top ]