Fターム[5F033KK29]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | シリサイド (1,324) | 高融点金属のシリサイド (608) | MoSi (55)

Fターム[5F033KK29]に分類される特許

1 - 20 / 55

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

SiCの除去法

【課題】基板に形成されたカーバイドシリコン層の少なくとも露出された部分を除去するための方法を提供する。

【解決手段】カーバイドシリコン層45を酸素含有プラズマに曝すことにより、前記カーバイドシリコン層45の少なくとも露出された部分を酸化シリコン層に変換し、そして基板から前記酸化シリコン層を除去するステップからなる。

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

液晶表示パネル及びその製造方法

【課題】スイッチング素子としてのトップゲート式TFTと、前記TFTを遮光するため

の遮光膜とが設けられた液晶表示パネルにおいて、遮光膜の材料としてMoを採用し、遮

光膜の被覆絶縁層にドライエッチング処理を施してMoの表面を露出させる場合にも、オ

ーバーエッチングによる遮光膜の消失を防げるようにした液晶表示パネルを提供すること

。

【解決手段】本発明の液晶表示パネル1は、遮光膜11がMoからなり、かつ、遮光膜1

1と上層金属配線との電気的接続が、バッファ絶縁膜12とゲート絶縁膜14を貫通する

第1コンタクトホール27を経て遮光膜11と電気的に接続されていると共に層間絶縁膜

16に被覆された第1導電部材25と、層間絶縁膜16を貫通する第2コンタクトホール

28を経て層間絶縁膜16の表面の金属配線と電気的に接続された第2導電部材26と、

を経て行われている。

(もっと読む)

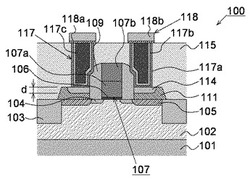

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置

【課題】ゲート電極とのコンタクトのためのコンタクトホールの形成時に、ゲート電極が深く掘り下げられることを防止できる半導体装置を提供すること。

【解決手段】ゲートトレンチ6を有するエピタキシャル層3に、ボディ領域5、ドレイン領域4、ソース領域9およびボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート電極8を埋設する。エピタキシャル層3には、層間絶縁膜11を積層する。ゲート電極8と層間絶縁膜11との間には、エピタキシャル層3とはエッチングレートの異なる材料からなるエッチングストッパ層14を介在させる。そして、エッチングにより、ゲート電極8およびボディコンタクト領域10それぞれとのコンタクトのための、ゲートコンタクトホール13およびソースコンタクトホール15を同時に形成する。ゲートコンタクトホール13は、平面視でエッチングストッパ層14と重なるように形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】小型化の進んだ回路セルでも回路信頼性の低下を防止できる回路レイアウトの設計方法を提供する。

【解決手段】ゲート電極1に電位差の大きい電源電位あるいは基準電位からのノイズの影響が及んで誤動作を起こしてしまうことを防ぐために、ゲート電極1に接続するプラグ5と電源電位あるいは基準電位が供給されるプラグ6との間は、プラグ5に電源電位あるいは基準電位からのノイズの影響が及ばない十分な距離だけ離間させるために、配線4下にて等間隔で配置されているプラグ6のうち、プラグ5(5A)と十分離間していない配置位置6Aに配置されるプラグ6のみを平面レイアウトの設計時に消去する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】簡易なプロセスで抵抗層上の所定領域を選択的にサリサイド化することができ、かつ、抵抗の占有面積を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】第1素子形成領域1と第2素子形成領域2とを有し、第2素子形成領域2に第1抵抗層30を形成し、その上に第1絶縁層40と導電層を形成し、第2素子形成領域2の導電層を高抵抗化し、導電層の一部を除去して、第1素子形成領域1にゲート電極50を形成すると同時に、第2素子形成領域2に第2抵抗層52を形成し、第2素子形成領域2の第2抵抗層52の上方に第2絶縁層90を形成し、第1素子形成領域1の半導体基板10に不純物を注入して、ソース領域およびドレイン領域70a,70bを形成し、ソース領域およびドレイン領域70a,70bの上と、第2素子形成領域2の第1抵抗層30および第2抵抗層52の上と、にシリサイド層80を形成する。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】膜厚バラツキを抑制し、かつドライエッチングダメージの発生を抑制できる優れた素子特性を兼ね備えた薄膜半導体装置及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極、前記ゲート電極の側壁に形成された、低温酸化膜、低温窒化膜及び低温酸化膜の3層構造のサイドウォールスペーサー、及び島状半導体層及びゲート電極を覆う層間絶縁膜を具備することを特徴とする。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】支持基板上に、単結晶半導体層を多層構造とした、多層集積回路を形成する場合の、工程数の簡略化を図る。また同集積化の向上を図る。

【解決手段】複数の半導体素子が絶縁層を介して積層される半導体装置において、絶縁層を介して半導体素子を構成する半導体層が積層された構造を有し、一の半導体層が配線とコンタクトする領域が、絶縁層を介して設けられる他の半導体層と重畳するように配置された構成とする。当該コンタクトする領域は、該一の半導体層に設けられる一導電型不純物領域から延在するシリサイド層によって形成される。すなわち、一の半導体素子と配線とのコンタクト領域をシリサイドで形成すると共に上層半導体素子と重畳する位置に配置させ、該半導体素子を構成する一導電型不純物領域と配線とのコンタクト領域との間をシリサイドで連結する構成を有する。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド膜上に形成されるシリコン窒化膜の膨れや剥離を抑えることができる半導体装置の製造方法を提供する。

【解決手段】表面にシリサイド膜が形成された領域を有する半導体基板を、酸素元素を含むガス雰囲気中でプラズマ処理してシリサイド膜の上に酸化膜を形成する工程と、その酸化膜を形成した後、半導体基板の表面を覆うシリコン窒化膜を形成する工程と、を備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層上に抵抗値の上昇が抑制されたコンタクトを備え、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10内に形成された活性領域50と、活性領域50の上面に形成されたシリサイド層45と、半導体基板10およびシリサイド層45の上に形成された第1の層間絶縁膜15と、シリサイド層45上に形成され、第1の層間絶縁膜15を貫通するコンタクトプラグ60とを備えている。コンタクトプラグ1個当たりのシリサイド層45の面積は、コンタクトプラグの面積以上、且つ、100μm2以下である。

(もっと読む)

半導体装置およびその作製方法

【課題】無線信号から生成できる電流値及び電圧値の範囲内で駆動できるメモリを搭載した半導体装置を提供することを課題とする。また、半導体装置製造後にデータの書き込みを行える追記型のメモリを提供することも課題とする。

【解決手段】絶縁表面を有する基板上にアンテナと、アンチヒューズ型のROMと、駆動回路とを形成する。アンチヒューズ型のROMを構成する一対の電極の間に、シリコン膜とゲルマニウム膜との積層を設ける。この積層を有するアンチヒューズ型のROMは、書き込み電圧のバラツキを低減することができる。

(もっと読む)

1 - 20 / 55

[ Back to top ]