Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

721 - 740 / 801

半導体装置の製造方法

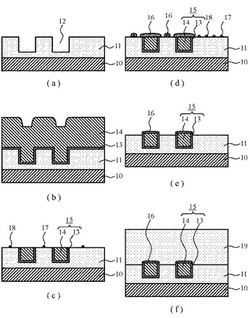

【課題】 絶縁膜中に形成されている配線用の溝に埋め込まれている配線層の上部に選択的に金属拡散防止膜を形成する半導体装置において、部分的選択破れ等に起因する配線間リーク電流を抑制する半導体装置の製造方法を提供する。

【解決手段】 ダマシン法により配線15を第1の絶縁膜11中に形成する。そして、電解メッキ法等により、配線15上のみに選択的に金属拡散防止膜16を形成する。その後、第2の絶縁膜19形成前に、第1の絶縁膜11上に存在する部分的選択破れにより意図せず生じた金属拡散防止膜16や、残留金属イオン17等を除去するCMP工程をする。

(もっと読む)

半導体装置の製造方法

【目的】 p−lowk膜上にバリアメタルを連続に形成することを目的とする。

【構成】 本発明の半導体装置の製造方法は、基体上に、表面にメチル(CH3)基が結合している絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜表面に、イミド系の高融点金属化合物を原料として、バリアメタル膜を形成するバリアメタル膜形成工程(114)と、を備えたことを特徴とする。そして、前記バリアメタル膜形成工程において、原子層気相成長法によりバリアメタル膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 疎水性の低誘電率絶縁膜を用いて、信頼性および電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】 アンモニアプラズマ14によって、SiOC膜8の表面に形成された疎水性のダメージ層を親水性の改質層15に変える。改質層15はフッ酸水溶液などに可溶であるので、改質層15を除去することによって、表面に清浄なSiOC膜8を露出させることができる。改質層15の膜厚は0.5nm〜10nmであることが好ましく、1nm〜5nmであることがより好ましい。

(もっと読む)

半導体装置

【課題】 ウェハのダイシングにより半導体チップの端部に発生するクラック(裂け目)が回路領域に到達するのを抑制する。

【解決手段】 シリコン基板1上に形成した半導体チップの端部付近で回路領域の周囲を覆うように形成されたシールリング5として、底面および側面をバリア膜で被覆した埋め込み銅配線14、18、22を積層し、それぞれの上層に積層される埋め込み配線18、22、26の第一の面6側の側面位置が、上層ほど半導体チップの端部側(左側)にずれるようにした。

このような構成とすることにより、層間絶縁膜2の中で埋め込み銅配線14、18、22の上面の銅が第一の面6側に露出するのを抑制することができる。これによりウェハをダイシングする際に半導体チップの端部からクラックが入った場合、銅の酸化による新たなクラック発生を抑制し、クラックが回路領域に侵入するのを防ぐことができる。

(もっと読む)

半導体装置

【課題】 二つの素子領域間に介在するガードリングを通じたノイズ伝搬を抑制する。

【解決手段】 半導体チップ100は、ロジック部およびアナログ部153を有する。また、半導体チップ100は、シリコン基板101と、シリコン基板101上に設けられた第一絶縁膜123〜第六絶縁膜143と、第一絶縁膜123〜第六絶縁膜143中に埋設された第一導電リング125〜第六導電リング145により構成されロジック部およびアナログ部153外周を取り囲む環状のシールリング105と、を有する。そして、ロジック部からシールリング105を経由してアナログ部153に至る経路の導通を遮断する非導通部104として機能するpn接合部が、シールリング領域106中に設けられている。

(もっと読む)

半導体装置の製造方法

【目的】 選択的に拡散防止膜を形成する場合でも、配線同士間でショートが生じてしまう原因となる導電性材料の研磨残りを生じさせないようにすることを目的とする。

【構成】 基体上の開口部に形成された導電性材料膜上に前記導電性材料膜に用いる導電性材料の拡散を防止する拡散防止膜を選択的に形成する拡散防止膜形成工程(S120〜S122)と、前記拡散防止膜が形成された後、前記基体上に絶縁膜を形成する絶縁膜形成工程(S124〜S128)と、前記絶縁膜形成工程の後、前記絶縁膜表面を研磨する平坦化工程(S130)と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】 シールリングまで剥離が進行することを防止して、さらに生産性の優れた半導体装置を提供する。

【解決手段】 半導体装置は、銅配線19が内部に形成された低誘電率膜5a〜5cと、低誘電率膜5cの上側に配置された酸化珪素膜6,7aと、酸化珪素膜6,7aの上側に配置された表面保護膜43と、回路形成領域の周りを取り囲むように形成されたシールリング23と、平面視したときにシールリング23の外側に形成された溝部22とを備える。溝部22は、底部が低誘電率膜5cよりも上側に位置するように形成され、底部が、銅配線19の上端よりも低くなるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 Cu系金属を充填したダマシン配線の信頼性、特にストレスマイグレーション(SM)耐性を向上させる。

【解決手段】 下地絶縁膜1上の層間絶縁膜2にトレンチ3を設け、トレンチ3に第1バリアメタル膜5を介して埋め込む第1Cu膜6を成膜し、20℃〜200℃範囲の第1の熱処理を施し清浄化した第1Cu膜6aにする。次に、第1Cu膜6aの第1キャップ層2c上の不要部分を化学的機械研磨で除去し、上記トレンチ3にCu配線8を形成する。その後に、300℃〜400℃の温度でCu配線8に第2の熱処理を施し、結晶性の優れたCu配線8aを形成する。同様に、ビアホールに埋め込む第2Cu膜を成膜した後に、300℃〜400℃範囲の第3の熱処理を施し、その後に化学的機械研磨してCuビアプラグを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線と接続部との間の接触抵抗を低減し、エレクトロマイグレーション特性を向上させる。

【解決手段】その表面に、配線を構成する銅の拡散等を防止するためのタングステン膜CM1が形成された第1層配線上の絶縁膜(24a、24b、24c、26b、26c)をエッチングすることによりコンタクトホールC2および配線溝HM2を形成する際、コンタクトホールC2底部のタングステン膜CM1を除去し、バリア膜PM2aを形成した後、コンタクトホールC2底部のバリア膜PM2aを除去し、銅膜(PM2b、PM2c)を形成した後、その表面を研磨することにより第2層配線M2およびその下層のプラグP2を形成する。また、タングステン膜CM1又はバリア膜PM2aの少なくとも一方を除去するか、それらを不連続な膜で構成する。その結果、第1層配線M1とプラグP2との間の接触抵抗を低減できる。

(もっと読む)

平坦化材料、反射防止膜形成材料、及びこれらを用いた半導体装置の製造方法

【課題】 デュアルダマシン構造形成時に、レジストパターンの解像不良を生じる反応阻害物質を除去する。

【解決手段】 露光に伴って発生する酸性物質との反応により、露光部が現像液に可溶(あるいは、不溶)となる化学増幅型レジスト膜の形成面の平坦化を行う平坦化材料、または、前記化学増幅型レジスト膜の直下に塗布される反射防止膜形成材料の少なくとも一方に、光酸発生剤または熱酸発生剤を含有する材料を使用する。前記材料が光酸発生剤を含有する場合は、化学増幅レジスト膜の形成前に全面露光を行い、また、前記材料が熱酸発生剤を含有する場合は、化学増幅レジスト膜の露光前に加熱を行うことで、酸性物質を発生させる。これにより、下層の炭素含有シリコン酸化膜等の低誘電率膜からなる第2の絶縁膜4等の中に存在する窒素に起因した塩基性物質を、当該材料の酸性物質で除去し、化学増幅型レジスト膜に拡散することを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】 洗浄工程において、配線を形成する材料がピンホールを介して消失することを防止できる半導体装置およびその製造技術を提供する。

【解決手段】 酸化シリコン膜37に埋め込むように配線41を形成する。続いて、配線41上を含む酸化シリコン膜37上に炭窒化シリコン膜43を形成する。ここで、炭窒化シリコン膜43は、ピンホール43aが貫通しない程度の膜厚で形成する。次に、炭窒化シリコン膜43を加工して、酸化シリコン膜37上の炭窒化シリコン膜43の膜厚を配線41およびその近傍領域上に形成された炭窒化シリコン膜43の膜厚よりも薄くする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 接続線と配線との接続部において、接続線周囲の配線幅の拡大や接続線個数の増大に伴う配線ピッチの増大によるレイアウト面積の損失を抑えつつ、かつ、エレクトロマイグレーションの発生を抑える。

【解決手段】 上層配線と下層配線と、上層配線と下層配線とを接続する接続線とを備える半導体装置において、接続線に対して電子の流れの下流側の配線の、少なくとも接続線に接続する接続部の直下又は直上部分、及び接続部から下流側の部分の膜厚を厚くして、厚膜化領域を設ける。

(もっと読む)

半導体装置の製造方法及び製造装置

表面に絶縁領域と金属領域とが露出した基板の該表面を、有機系洗浄液を用いて洗浄する。洗浄された基板の表面に紫外線を照射する。これにより、基板表面に残留物が残ることを抑制することができる。  (もっと読む)

(もっと読む)

成膜方法、半導体装置の製造方法、半導体装置、プログラムおよび記録媒体

【課題】 半導体装置のCu拡散防止膜とCu配線との密着力を良好とし、半導体装置の信頼性を良好とする。

【解決手段】 被処理基板上にCu膜を成膜する成膜方法であって、前記被処理基板上に形成されたCu拡散防止膜上に密着膜を形成する第1の工程と、前記密着膜上にCu膜を成膜する第2の工程と、を有し、前記密着膜はPdを含むことを特徴とする成膜方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10上に第1の絶縁膜11を介してパッド電極12を形成する。次に、パッド電極12上を含む第1の絶縁膜11上に、パッド電極12を露出する開口部14を有した第2の絶縁膜13を形成する。次に、開口部14を含む第2の絶縁膜13上に、当該開口部14を通してパッド電極12と電気的に接続された第1の配線層15を形成する。次に、半導体基板10の裏面からパッド電極12に到達するビアホール16を形成する。次に、ビアホール16の底部のパッド電極12と電気的に接続された貫通電極20及び第2の配線層21を形成する。さらに、保護層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体基板に形成された開口部の形成状態を、断面観察しないでも確認できるようにすることを目的とする。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成されたパッド電極3を露出するように基板裏面から開口部が形成され、この開口部を介して前記パッド電極3に配線層10が形成されて成るものにおいて、前記開口部の形成状態をモニターするためのモニター開口部6bをスクライブライン上に形成することを特徴とするものである。

(もっと読む)

多層配線構造を有する半導体装置およびその製造方法

多層配線構造は、第1の層間絶縁膜と、前記第1の層間絶縁上に形成された第2の層間絶縁膜と、前記第1の層間絶縁膜中に形成され第1のバリアメタル膜で側壁面および底面が覆われた配線溝と、前記第2の層間絶縁膜中に形成され第2のバリアメタル膜で側壁面と底面が覆われたビアホールと、前記配線溝を充填する配線パターンと、前記ビアホールを充填するビアプラグとよりなり、前記ビアプラグは前記配線パターンの表面にコンタクトし、前記配線パターンは前記表面に凹凸を有し、前記配線パターンは、前記配線パターン中において前記表面から前記配線パターン内部に向かって延在する結晶粒界に沿って、前記表面におけるよりも高い濃度で酸素原子を含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10上に第1の絶縁膜11を介して形成されたパッド電極12上に、高融点金属層13を形成する。次に、パッド電極12及び高融点金属層13上を含む半導体基板10の表面上にパッシベーション層14を形成し、さらに、樹脂層15を介して支持体16を形成する。次に、半導体基板10をエッチングして、半導体基板10の裏面からパッド電極12に到達するビアホール17を形成する。次に、第2の絶縁膜18を介して、ビアホール17の底部で露出されたパッド電極12と電気的に接続された貫通電極20及び配線層21を形成する。さらに、ソルダーレジスト層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10をエッチングして、半導体基板10の裏面からパッド電極12に到達するビアホール16を形成する。ここで、上記エッチングは、ビアホール16の底部の開口径Aが、パッド電極12の平面的な幅Cよりも大きくなるようなエッチング条件により行われる。次に、ビアホール16の底部でパッド電極12を露出する第2の絶縁膜17を、当該ビアホール16を含む半導体基板10の裏面上に形成する。次に、ビアホール16の底部で露出されたパッド電極12と電気的に接続された貫通電極20及び配線層21を形成する。さらに、保護層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

銅相互接続配線およびこれを形成する方法

集積回路のための相互接続構造体における使用のための銅相互接続配線層(602)の表面上のキャッピング層(614)およびガスクラスタイオンビーム処理の適用による集積回路のための改良された集積相互接続構造体を形成する方法。低減された銅拡散と改善されたエレクトロマイグレーション寿命が結果として得られ、また選択的金属キャッピング技法の使用とそれらに付随する歩留まり問題とが回避される。 (もっと読む)

721 - 740 / 801

[ Back to top ]