Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

761 - 780 / 801

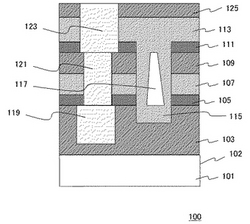

半導体装置

【課題】 半導体装置中のクラックの伝播を抑制し、他の領域に影響を与えないようにする。

【解決手段】 シリコン基板101上に設けられたSiCN膜105およびSiOC膜107を貫通する凹部の側面を覆う界面補強膜115を設ける。界面補強膜115はSiOC膜113と連続一体に形成され、エアギャップ117を有する。

(もっと読む)

半導体集積回路装置

【課題】 低い比誘電率を有し、かつ望ましい特性を有する絶縁膜を有する半導体集積回路装置を提供することである。

【解決手段】 半導体集積回路装置は、層間絶縁膜の一部として比誘電率が2.5以下のSiC:H膜を含む。

(もっと読む)

デュアル・ダマシン配線及びその形成方法

【課題】 デュアル・ダマシン配線の形成方法を改善し、デュアル・ダマシン配線効率を向上させる新たなデュアル・ダマシン配線構造体を提供すること。

【解決手段】 デュアル・ダマシン相互接続構造体及び該構造体を形成する方法であり、該構造体はデュアル・ダマシン配線を誘電体層に含み、該デュアル・ダマシン配線は該誘電体層の厚さと比べて小さい距離にわたって該誘電体層内に延び、デュアル・ダマシン・ビア・バーは該デュアル・ダマシン配線の底面と一体になっており、かつ、該底面から該誘電体層の底面に向かって延びる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ボイドの移動経路となるバウンダリーが顕著に低減されるため、SIV不良の発生を効果的に抑制することができ、信頼性の高い半導体装置を提供する。

【解決手段】 相対的に広幅の第2銅配線110,126の上面において、銅のグレインが数10μm程度と非常に大きい。第2銅配線110,126の配線幅は0.3μm〜数10μm程度であるので、第2銅配線110,126の上面において配線幅方向のバウンダリーが顕著に低減され、第2銅配線110,126とビア113との接続部分にボイドが集中・合一して大きなボイドが形成されることを抑制することができ、SIVの発生が効果的に抑制される。相対的に狭幅の第1銅配線111,127の面方位はEM耐性を向上させるために主にCu(111)であり、相対的に広幅の第2銅配線110,126の面方位はSIV耐性を向上させるために主にCu(200)である。

(もっと読む)

積層金属膜のパターン構造及びパターン形成方法並びに該積層金属配線を備える液晶表示装置又は半導体装置

【課題】ウェットエッチングによる積層金属膜のエッチング速度の面内ばらつきを低減し、所望のテーパー形状を得ることができる積層金属膜のパターン構造及びパターン形成方法並びに液晶表示装置または半導体装置の提供。

【解決手段】Al又はAl合金とMo又はMo合金などのバリア金属膜とからなる積層金属膜(好ましくは卑金属側が下層に存在するような積層金属膜)をウェットエッチング法で一括エッチング処理してパターン形成する場合において、製品素子領域に配線パターンを形成すると共に、非製品素子領域のエッチング開口部にも任意の微細パターンを形成し、製品素子領域及び非製品素子領域双方のエッチング開口部全域の電池反応を促進させ、エッチング速度の面内分布を均一化させる。これにより、積層金属配線の断面形状を良好なテーパー形状として、製品の歩留まりや長期信頼性を向上させる。

(もっと読む)

半導体装置の製造方法

【課題】 貫通電極を有した半導体装置の製造方法において、工程を簡略化して製造コストを極力低く抑えると共に、歩留まりの向上を図る。

【解決手段】 半導体基板10の表面に第1の絶縁膜11を形成し、その一部をエッチングして、半導体基板10の一部を露出する開口部11aを形成する。次に、開口部11a内から第1の絶縁膜11上に延びるパッド電極12を形成する。半導体基板10の裏面上には第2の絶縁膜15を形成する。次に、開口部11aよりも大きい開口径を有したビアホール16を形成する。そして、ビアホール16内から第2の絶縁膜15上に延びる第3の絶縁膜17を形成し、ビアホール16の底部の第3の絶縁膜17をエッチングしてパッド電極12を露出する。その後、ビアホール16内に貫通電極19及び配線層20を形成する。最後に、半導体基板10を複数の半導体チップ10Aに切断分離する。

(もっと読む)

多層配線構造と多層配線構造を有する半導体装置とこれらの製造方法

【課題】 多層配線構造における上層配線の下層配線に対する接続部の形成にあたり、その接続導体の接続部の清浄化処理において問題となる特性劣化を確実に回避する。

【解決手段】 下層配線溝(第1配線溝)11g内の埋込み配線(第1埋込み配線)11bに上層配線(第2埋込み配線)12bが接続導体12cを介して接続される構成において、接続導体12cの形成時の第1埋込み配線11b表面の水素ラジカルないしは水素ブラズマによる清浄化に耐性を有する保護膜7を、この清浄化の雰囲気にさらされ侵食される第2埋込み配線12bが埋め込まれる配線溝12g、接続導体12cが充填される配線接続孔12hの内表面に形成することによって、上述した清浄化に際して絶縁層が侵食されることを回避し、充分な洗浄を行うことができるようにして特性劣化の改善を図る。

(もっと読む)

半導体装置の製造方法

【課題】 貫通電極を有する半導体装置の製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 パッド電極11に対応した位置で半導体基板10を貫通するビアホール16を形成する。次に、ビアホール16を含む半導体基板10の裏面上に絶縁膜17を形成する。次に、半導体基板10の裏面上に、ビアホール16の開口部の縁でオーバーハング部18aを有する補強用絶縁膜18を形成する。そして、補強用絶縁膜18をマスクとして、ビアホール16の側壁の絶縁膜17を残存させつつ、当該底部の絶縁膜17をエッチングして除去する。次に、ビアホール16を含む半導体基板10の裏面に、貫通電極21、配線層22、及び導電端子24を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

半導体装置およびその製造方法

【課題】 有機シロキサン系絶縁膜を用いて電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】 半導体基板の上に形成された多層配線構造を備える半導体装置において、この多層配線構造は、比誘電率が3.1以下で硬度が2.7GPa以上である有機シロキサン系絶縁膜を少なくとも一部に備えた層間絶縁膜を有する。また、この有機シロキサン系絶縁膜は、(炭素原子数/珪素原子数)の比が0.5以上1.0以下である。さらに、この多層配線構造は、有機シロキサン系絶縁膜から炭素が抜けて(炭素原子数/珪素原子数)の比が0.1以下になった絶縁層を有機シロキサン系絶縁膜の上面に有することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置は、層間絶縁膜1と、層間絶縁膜1内に形成された下部配線5と、層間絶縁膜1上に形成されたライナー膜11と、ライナー膜11上に形成された層間絶縁膜12とを備えている。下部配線5に下部孔8が開口しており、ライナー膜11および層間絶縁膜12には下部孔8に繋がる上部孔10が開口しており、下部孔8の口径d2は上部孔の口径d1よりも大きくなっている。さらに、下部孔8の内壁面に形成された導電膜15と、上部孔10の内壁面に沿って形成されたバリアメタル13と、上部孔10内および下部孔8内を埋めるように形成されたCu膜19とを備えている。導電膜15はバリアメタル13と同じ物質を含んでいる。

(もっと読む)

半導体装置の製造方法

【目的】 不純物の残留を抑制し、バリアメタルを高純度に成膜することを目的とする。

【構成】 基体上にTa[N((CH3)2]5を供給するTa[N((CH3)2]5供給工程(S102)と、前記Ta[N((CH3)2]5におけるTaとは異なるCを除去するH2供給工程(S106)と、前記Cが除去された前記Ta[N((CH3)2]5の吸着分子に基づいて前記TaN膜を生成するNH3供給工程(S108)と、を備え、前記Ta[N((CH3)2]5工程とH2供給工程とNH3供給工程とを繰り返すことで、前記基体上にTaN膜を堆積させることを特徴とする。

(もっと読む)

半導体装置の製造方法

【目的】 CVD法により形成された多孔質low−k膜上にバリアメタルを連続に形成することを目的とする。

【構成】 基体上に、有機物質原料を用いてCVD法により多孔質絶縁膜を形成するポーラスlow−k膜形成工程(S104)と、前記ポーラスlow−k膜表面に結合されるCH3基をエッチングするエッチング工程(S112)と、前記CH3基がエッチングされた前記ポーラスlow−k膜表面にALD法によりバリアメタル膜を形成するバリアメタル膜形成工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 ボンディング工程、CMP工程、熱応力等による機械的衝撃やウエハの変形によるビアの変位を小さく制御できる半導体装置及びその製造方法を提供する。

【解決手段】 第1配線22と、第1配線22の上に配置された低誘電率絶縁膜310と、低誘電率絶縁膜310の中に第1配線22と接続するように埋め込まれ、第1配線22の長手方向に測った第1長さLx、第1配線22が配置された平面で第1配線22に直交する方向に測った第2長さLy、第1配線22が配置された平面に垂直な高さHに対する第1及び第2長さLx,Lyの少なくとも一方との比が1以上である複数の第1扁平ビア31a,31bと、低誘電率絶縁膜310の上に配置され、複数の第1扁平ビア31a,31bにそれぞれ接続された第2配線32とを備える。

(もっと読む)

半導体装置の製造方法

【目的】 ポーラス状に形成される多孔質低誘電率(p−lowk)膜内へのバリアメタルに用いたメタルの拡散を抑制することを目的とする。

【構成】 p−lowk膜を基体上に形成するp−lowk膜形成工程(S102)と、前記p−lowk膜表面側に形成される空孔が前記p−lowk膜内部側の空孔へ連結する連結位置における開口サイズより大きい分子(Ta−R1)を前記p−lowk膜表面に吸着させるTa[N(C2H5)2]5供給工程(S106)と、前記分子(Ta−R1)と反応するNH3を供給し、TaN膜を形成するNH3供給工程(110)と、前記開口サイズより小さい分子(Ta−R2)を吸着させるTaCl5供給工程(S114)と、前記分子(Ta−R2)と反応するNH3を供給し、TaN膜をさらに形成するNH3供給工程(120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】下部電極形成工程を別途設けることなく、少ない占有面積で大きな容量を持つMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】MIMキャパシタ形成領域Aの第2の絶縁膜6には、Ta/TaNのようなバリア膜からなる下部電極12とAl2O3のような金属酸化膜からなる容量絶縁膜13とTiNのようなバリア膜からなる上部電極14とを有するMIMキャパシタ15が形成されている。一方、配線形成領域Bの第2の絶縁膜6には、上部に設けられた第2配線部W2と下部に設けられた第2プラグ部P2が一体化形成されたバリア膜8bと導電膜9bからなる第2層配線10bが形成されている。そして、MIMキャパシタ15の下部電極12と第2層配線10bのバリア膜8bは共通のバリア膜を用いて同時に形成されたものである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダマシン配線に含まれる不純物の濃度を低下させて、配線中の欠陥を低減させる事が可能な半導体装置の製造方法を提供する。

【解決手段】ウェハW上の層間絶縁膜1に幅が0.3μm以下の細幅配線溝1a及び幅が0.3μmを超える太幅配線溝1bを形成する。層間絶縁膜1上にバリアメタル膜2及びシード膜3を形成する。その後、細幅配線溝1a全体に埋め込まれ、かつ太幅配線溝1bの一部に埋め込まれるように膜4を電解めっき法により形成する。太幅配線溝1bの他の部分に埋め込まれるように膜4よりも不純物濃度が低い膜5をスパッタ法により形成する。熱処理により膜4中の不純物を膜5中に拡散して、配線膜6を形成する。最後に層間絶縁膜1上の不要なバリアメタル膜2及び配線膜6を除去し、細幅配線と太幅配線を形成する。

(もっと読む)

半導体装置

【課題】 ボンディングパッドの下面にも電子部品を配置することができる構造を備えた半導体装置を提供する。

【解決手段】 外部接続端子を構成するボンディングパッド24と、ボンディングパッド24の下面に、少なくとも二層の銅膜44,16と、前記隣接する銅膜44,16同士を接続するように設けられる接続ビア18から形成されるボンディングパッド下部領域48と、ボンディングパッド下部領域48を取り囲むように銅膜および隣接する銅膜同士を接続する環状導体より構成されるシールリング42と、シールリング42の外側においてボンディングパッド24に接続される配線26と、を含む。

(もっと読む)

半導体装置

【課題】 ダマシン配線構造体を有する半導体装置において、シールリングと配線あるいは電極パッドとの短絡発生を無くする。

【解決手段】 半導体装置の層間絶縁膜の溝側壁に形成され導電性のバリア材料膜から成る上層バリア層4、溝内に埋め込まれ配線材料膜から成るたとえば10μm幅の上層シールリング配線5が設けられ、上層シールリング配線5内に混在して複数の島状の絶縁体6が形成されている。この島状の絶縁体6は、上記ダマシン配線が形成される層間絶縁膜により形成される。そして、素子形成領域に第1上層溝配線7、第2上層溝配線8等が配設され、上層バリア層4がその周囲に設けてある。ここで、上層シールリング配線5および両上層配線は共に(デュアル)ダマシン配線構造になる。

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

半導体装置

【課題】 銅を主構成材料とする配線構造において、ストレスマイグレーションによるボイドの発生を抑制し、信頼性の高い半導体装置を提供する

【解決手段】 半導体基板上の絶縁膜上に形成される多層配線構造において、主構成材料が銅からなる第1の配線の上面に接するように、下から順にバリア性が高く、かつ圧縮応力を有する第1の絶縁膜、引張応力を有する第2の絶縁膜、前記第1の絶縁膜と前記第2の絶縁膜よりも誘電率の低い第3の絶縁膜が少なくとも積層されており、前記第1の絶縁膜、前記第2の絶縁膜、および前記第3の絶縁膜を貫通し前記第1の配線に接するようにビアホールが設けられている配線構造とする。

(もっと読む)

761 - 780 / 801

[ Back to top ]