Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

641 - 660 / 801

成膜方法及び半導体装置の製造方法

【課題】 2.7より低い比誘電率を有する低誘電率絶縁膜及び4より低い比誘電率を有するバリア絶縁膜を化学気相成長法により成膜する方法を提供するものである。

【解決手段】 シリコン原子による5員環以上の環状構造を有し、かつ該シリコン原子によるシロキサン結合を有する第1のシリコン含有有機化合物と、シリコン原子による4員環以下の環状構造又は4以下のシリコン原子の鎖状構造を有し、かつ該シリコン原子によるシロキサン結合を有する第2のシリコン含有有機化合物とを含む成膜ガスのプラズマを生成し、反応させて基板31上に絶縁膜32を形成する。

(もっと読む)

半導体装置及びその製造方法

層間絶縁膜(1)及びCMPストッパ膜を形成した後、配線溝を形成する。次に、配線溝内にバリアメタル膜(4)及びCu膜(5)を埋め込んだ後、CMPストッパ膜が露出するまで、CMP等によってCu膜(5)及びバリアメタル膜(4)を平坦化することにより、下層配線(17)を形成する。次いで、ドライエッチングによってCMPストッパを除去することにより、相対的に下層配線(17)の表面を周囲から突出させる。続いて、全面にエッチングストッパ膜(6)を形成する。その後、ビアプラグ(18)を形成し、更に、下層配線(17)と同様にして、上層配線(19)を形成する。  (もっと読む)

(もっと読む)

容量素子、半導体装置及び半導体装置のパッド電極の端子容量設定方法

【課題】 実効入力抵抗を増大させず良好なスペース効率を保ち、かつ、きめ細かい端子容量の調整を実現可能なパッド電極構造を有する半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体基板上に形成されたパッド電極10と、パッド電極10の近傍に配置されパッド電極10と絶縁されつつ外部固定電位と接続された周囲配線部11と、パッド電極10における外縁付近の開口部に導電材料を埋め込んで下方に延伸形成されパッド電極と電気的に接続された第1のビア12と、周囲配線部11の開口部に導電材料を埋め込んで下方に延伸形成され周囲配線部と電気的に接続された第2のビア13とを備え、第1のビア12と第2のビア13は、互いの側面間に容量を形成するように対向配置されて構成されている。

(もっと読む)

半導体装置の製造方法

【課題】 水素によるキャパシタ誘電体膜の劣化を防止することが可能な半導体装置の製造方法を提供すること。

【解決手段】 シリコン(半導体)基板1の上に下地絶縁膜10を形成する工程と、下地絶縁膜10の上に、下部電極11a、キャパシタ誘電体膜12a、及び上部電極13aを順に形成してなるキャパシタQを形成する工程と、キャパシタQを覆う第1層間絶縁膜15を形成する工程と、第1層間絶縁膜15の上に、シリコン基板1にバイアス電圧を印加しないプラズマCVD法により第1保護絶縁膜16を形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】エレクトロマイグレーション耐性およびストレスマイグレーション耐性に優れた配線構造およびこの配線構造を少ない工程数で形成する形成方法を提供する。

【解決手段】第1絶縁層102が有する下層溝の内面に第1拡散防止膜104を介して埋め込み形成された下層配線105と、下層配線105上に形成された高融点金属または高融点金属化合物からなる層間拡散防止膜106と、第2絶縁層108および層間拡散防止膜106を貫通して下層配線105に達するビアホール109の内面に形成された導電性の第2拡散防止膜112と、この第2拡散防止膜112を介してビアホール内に埋め込み形成された導電体114とを備え、ビアホール底部における下層配線105の上面から第2絶縁層108の側面にわたって層間拡散防止膜106の構成材料からなる付着膜106aが形成されたことを特徴とする配線構造。

(もっと読む)

半導体装置及びその製造方法

【課題】低誘電率層間絶縁膜に導入されたダメージに起因する配線の性能の劣化を抑制した半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置は、配線溝若しくは接続孔の少なくとも一方が形成され、配線溝若しくは接続孔表面近傍の炭素濃度若しくは膜密度が内部の炭素濃度若しくは膜密度と同等若しくはそれより高い低誘電率絶縁膜と、前記配線溝若しくは接続孔内に形成された導電体層と、前記低誘電率絶縁膜と前記導電体層との間に設けられたバリアメタルと、前記バリアメタルと前記低誘電率絶縁膜との間に設けられた第2の絶縁膜とを具備する配線構造を具備する。

(もっと読む)

半導体装置の製造方法

【課題】 膜厚の異なるゲート絶縁膜を備えた構成の半導体装置で、ゲート絶縁膜剥離の工程の短縮を図りながら優れた特性を有する半導体装置の製造方法を提供する。

【解決手段】 NANDフラッシュメモリで、周辺回路の高電圧駆動トランジスタHV−P、HV−Nと低電圧駆動PチャンネルトランジスタLV−Pについて、ゲート電極7の形成後に、不純物のイオン注入時に、リソグラフィ処理で同時にゲート絶縁膜6、8を除去し、イオン注入を行う。これにより、低電圧駆動トランジスタLV−Pのシリコン基板1表面がシリコンガウジングを発生するが、特性に悪影響を与えることなくリソグラフィ工程を統合できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 低誘電率膜の機械的、熱的ストレス耐性を向上しつつ、プロセスチャージングダメージ耐性の向上を実現する。

【解決手段】 基板1上に下方より順に形成された第1から第5の絶縁膜2,4,5,13,14と、第3の絶縁膜5内に設けられた、第1の導電性材料からなる第1のダミービア11と、第5の絶縁膜14内に設けられた、第2の導電性材料からなる第2のダミービア16とを備え、平面的に見て、第2のダミービア16は第1のダミービア11の直上上方に形成され、第1のダミービア11と第2のダミービア16は、第4の絶縁膜13によって電気的に絶縁されている。

(もっと読む)

半導体装置およびその製造方法

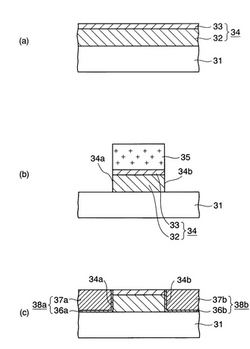

【課題】 MIM(Metal Insulator Metal)構造を有するキャパシタの信頼性、製造歩留まりを向上させる。

【解決手段】 キャパシタ(C)は、層間絶縁膜28の電極溝29内に形成された下部電極33と、下部電極33上に形成された誘電膜35と、誘電膜35上に形成された上部電極36とからなるMIM構造を有している。さらに、上部電極36および誘電膜35は、下部電極33よりも大きい面積で形成され、下部電極33の全体が上部電極36および誘電膜35の内側に配置されるようになっている。

(もっと読む)

半導体装置およびその製造方法

【課題】 製造工程における機械的強度を強くするとともに、配線間絶縁膜を低誘電率化する。

【解決手段】 本発明の半導体装置の製造方法は、以下の手順を含む。まず高密度絶縁膜を形成する(S102)。つづいて、高密度絶縁膜にビアホールおよび配線溝を形成する(S104)。次いで、ビアホールおよび配線溝を埋め込むように、配線およびビア金属膜を形成する(S106)。その後、CMPにより、配線溝外部に露出した金属膜を除去する(S108)。つづいて、Heプラズマ照射またはエネルギー線照射により、高密度絶縁膜表面を低密度化する(S110)。その後、低密度化された絶縁膜上にエッチングストッパ膜(またはキャップ膜)を形成する(S112)。

(もっと読む)

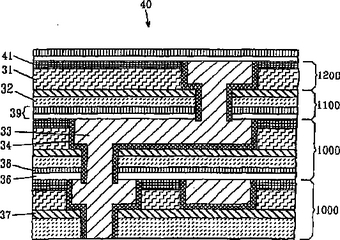

半導体ダイオードを含む低温で製作された高密度不揮発性メモリアレイ

高密度のモノリシックな三次元メモリアレイにおける使用に適したメモリセルを説明する。メモリセルの好ましい実施形態において、比較的低い温度で結晶化させることができるゲルマニウムまたはゲルマニウム合金で形成された半導体接合ダイオードが、導体間に配置されて形成される。低温度材料の使用により、導体を銅またはアルミニウムで形成することが可能になり、銅およびアルミニウムは両方とも、非常に小さいフィーチャサイズで十分な電流を提供する、非常に密なスタックアレイを見越した、低抵抗率材料である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 良好な特性を有するMIM型キャパシタを半導体基板上に形成し、特別な製造工程を追加せずに製造する半導体装置及びその製造方法を提供する。

【解決手段】

下層層間絶縁膜3上に形成されたMIM型キャパシタ11(下部電極膜8a、キャパシタ絶縁膜9a、上部電極膜10aからなる)は、下層配線6と上層配線14cを接続するプラグ14aと同じ高さに形成することにより、上部電極用接続孔を必要としない。

(もっと読む)

半導体装置およびその製造方法

【課題】 同じ導電型のチャンネルを形成する閾値の異なる低電圧駆動トランジスタで、閾値調整のためのイオン注入を個別に対応させて行う必要のない半導体装置およびその製造方法を提供する。

【解決手段】 低閾値型の低電圧駆動NチャンネルトランジスタLV−N−LVtをウェルを形成せず、直接P型のシリコン基板1に形成するようにし、閾値調整のためのイオン注入工程を他のトランジスタの閾値調整のためのイオン注入工程と統合させることで工程の短縮を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタの信頼性を向上させた半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に第1の絶縁膜を介して形成された第1の配線と、前記第1の絶縁膜上に形成されたMIMキャパシタと、前記MIMキャパシタを覆って形成された第2の絶縁膜と、前記第2の絶縁膜表面に形成された第2の配線と、前記MIMキャパシタを取り囲むように前記第2の絶縁膜に埋設されたガードリングと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ビアプラグやコンタクトプラグの径が微細になっても、ホールパターンを高密度で形成することのできる半導体装置およびその製造方法を提供する。

【解決手段】 絶縁膜上に所定間隔に形成された少なくとも1つの配線に垂直方向から連通するビアホールを備えた半導体装置において、一端が配線11に重なるように第1回リソグラフィ位置13Aで楕円形の第1のホールパターンを露光し、一端が第1のホールパターンの前記一端に重なるように楕円形の第2のホールパターンを第2回リソグラフィ位置13Bにおいて露光したリソグラフィ技術により、2つのホールパターンの重なり部分にビアホール12を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線間容量およびRC遅延量の増加を招くことなく、ビア埋め込みの不良に基づくビア導通の不良による信頼性劣化を改善することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 SiO2等による第1の層間絶縁膜1上の所定位置に下層配線3が埋め込まれ、この下層配線3はバリアメタル2で被覆されている。下層配線3とウェハ1の上面には、Cを主成分とするPAEによる有機膜5が設けられ、有機膜5の全面にSiO2、SiOC、SiC、SiCN等による第2の層間絶縁膜6が形成され、この第2の層間絶縁膜6に上層配線8及びビア9が設けられている。

(もっと読む)

超小型電子相互接続構造の多層キャップ障壁

【課題】超小型電子相互接続構造の多層キャップ障壁を提供すること。

【解決手段】本明細書には、少なくとも1つの低kサブレイヤと少なくとも1つの空気障壁サブレイヤとを有する低k多層誘電拡散障壁層を有する構造が記載される。多層誘電拡散障壁層は金属の拡散に対する障壁であり、かつ空気の透過に対する障壁である。この構造の生成に関連した方法および組成物も記載される。これらの低k多層誘電拡散障壁層を利用する利点は、導電性金属フィーチャ間のキャパシタンスの低下によるチップ性能の増大、および多層誘電拡散障壁層が空気を通さず金属拡散を防ぐことによる信頼性の増大である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置及びその製造方法における信頼性の向上を図る。

【解決手段】本発明の半導体装置は、半導体基板1上に第1の絶縁層2を介して形成されたパッド電極3と、前記半導体基板1の裏面から前記パッド電極3の表面に到達するように形成されたビアホール8とを有するものにおいて、前記ビアホール8が、前記半導体基板1の裏面に近い部分よりも前記パッド電極3に近い部分の開口径が広くなるように形成された第1の開口部7Aと、前記第1の開口部7Aに連なり、前記半導体基板1の表面に近い部分よりも前記パッド電極3の表面に近い部分の開口径が狭くなるように前記第1の絶縁層2に形成された第2の開口部7Bとから成ることを特徴とする。

(もっと読む)

埋込配線の形成方法

【課題】 埋込配線の形成方法に関し、比誘電率の増加をもたらすことなくエッチング残渣を除去するとともに、金属の浸食をもたらすことなく配線露出表面の清浄化を行う。

【解決手段】 下層の配線1を露出させるための開口を伴う配線溝孔エッチング後に、プラズマ励起により配線上の残渣5を剥離処理したのち、大気中に晒すことなく、気体状態の有機系ガス6により配線の露出部表面の清浄化処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】 強誘電体キャパシタのダメージを防止しながら、安定した特性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】 配線より厚いAl2O3膜41を保護膜として形成した後、CMPにより、導電性バリア膜18が露出するまでAl2O3膜41を研磨する。つまり、Al2O3膜41に対して、導電性バリア膜18をストッパ膜としてCMPを行う。次に、例えば高密度プラズマ法によりシリコン酸化膜19を全面に形成し、その表面を平坦化する。次いで、シリコン酸化膜19上に、水素及び水分の侵入を防止する保護膜としてAl2O3膜20を形成する。更に、Al2O3膜20上に、例えば高密度プラズマ法によりシリコン酸化膜23を形成する。その後、シリコン酸化膜23、Al2O3膜20及びシリコン酸化膜19に、導電性バリア膜18まで到達するビアホールを形成し、その内部にWプラグ24を埋め込む。

(もっと読む)

641 - 660 / 801

[ Back to top ]