Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

701 - 720 / 801

半導体装置の製造方法

【課題】機械的強度が十分に強く、しかも、比誘電率が極めて低い絶縁膜を有する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に多孔質の第1の絶縁膜38を形成する工程と、第1の絶縁膜上に、第1の絶縁膜より密度の高い第2の絶縁膜40を形成する工程と、第1の絶縁膜上に第2の絶縁膜が存在している状態で、電子線、紫外線又はプラズマを照射し、第1の絶縁膜を硬化させる工程とを有している。緻密性の高い第2の絶縁膜を介して第1の絶縁膜に電子線等を照射するため、第1の絶縁膜に大きなダメージが加わるのを防止しつつ、第1の絶縁膜を硬化させることができる。第1の絶縁膜にダメージが加わるのを防止することができるため、吸湿性の増大や密度の増大を防止することができ、ひいては、比誘電率の増大を防止することができる。従って、比誘電率が低く、しかも機械的強度の高い絶縁膜を有する半導体装置を提供することができる。

(もっと読む)

配線構造およびその製造方法

半導体素子が形成された基板上に金属配線を積層し、半導体素子の接続を得る多層配線構造において、多孔質絶縁膜内に微細な金属配線を形成する場合に、リーク電流が発生し隣接する配線間の絶縁性が損なわれたり、隣接する配線間の絶縁耐性が劣化することのない配線構造およびその製造方法を提供する。半導体素子が形成された基板上の金属配線構造において、層間絶縁膜と金属配線との間に、有機物を含む絶縁性バリア層413を形成する。この絶縁性バリア層は隣接する配線間のリーク電流を低減し、絶縁信頼性を向上させることができる。  (もっと読む)

(もっと読む)

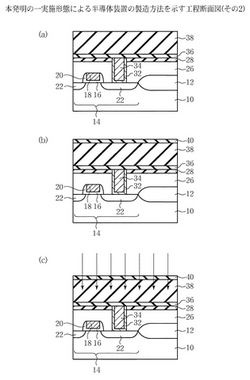

半導体装置の製造方法

【課題】配線間の寄生容量を十分に低減し得る半導体装置の製造方法を提供することにある。

【解決手段】半導体基板10上に多孔質絶縁膜54を形成する工程と、多孔質絶縁膜の表層部を緻密化する緻密化処理を行うことにより、多孔質絶縁膜54の表層部に、多孔質絶縁膜より密度の高い緻密層56を形成する工程とを有している。多孔質絶縁膜の表層部を緻密化する緻密化処理を行うことにより緻密層を形成するため、エッチングストッパ膜や保護膜として機能しうる良質な緻密層を極めて薄く形成することができる。従って、配線間の寄生容量を十分に低減することができる。

(もっと読む)

半導体装置の製造方法とそのような方法により得られる半導体装置

この発明は、半導体本体(1)と基板(2)とを備えた半導体装置(10)であって、少なくとも一つの半導体素子(3)を備え、そして、少なくとも一つの接続領域(4)と、接続領域(4)に接続された上部に横たわる帯状接続導体(5)とが設けられ、帯状接続導体と接続領域とが共に誘電体材料内に窪んでおり、続いて、第一の誘電体層(6)と、第一のハードマスク層(7)と、そして、第二の誘電体層(8)とが半導体本体(1)上に堆積され、接続領域(4)が形成される部位において、炭素とフッ素との化合物を含むプラズマを用いたプラズマエッチングにより第一の誘電体層(6)内にバイア(44)が形成され、そして、この構造の上部に堆積されたパターンニングされたフォトレジスト層が存在している状態で、接続導体(6)が形成される部位において、プラズマエッチングにより第二の誘電体層(8)内にトレンチ(55)が形成され、接続領域(4)と接続導体(5)とをそれぞれ形成するために、バイア(44)及びトレンチ(55)が導電材料で満たされ、そして、トレンチ(55)が形成される前に、既に形成されたバイア(44)が有機材料(2)で満たされる半導体装置の製造方法に関する。この発明では、バイア(44)のエッチング中にバイア(44)が同時にほぼ完全に有機材料(20)で満たされるように、第一の誘電体層(6)の材料と、プラズマエッチングによる第一の誘電体層(6)内のバイア(44)の形成中のエッチング条件とが選ばれ、この構造及びプラズマ内に既に存在する有機材料から有機材料(20)が形成される。エッチングの間にレジスト層が存在することと、そこで炭素とフッ素との化合物を用いること以外に、関わる条件は、第一(そして第二)の誘電体層(6,8)とこれら層(6,8)のエッチングの間の電力の選択に関する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 低誘電率絶縁体からなる層間絶縁膜を用いた半導体装置において、機械的及び熱的な耐性を向上できるようにする。

【解決手段】 半導体装置は、半導体基板10に形成された半導体素子と、半導体基板10の上方に形成され、半導体素子と電気的に接続された第1の配線41Aと、該第1の配線41Aの上方に誘電率が酸化シリコンよりも低い絶縁体からなる第3の層間絶縁膜23を介在させて形成された第2の配線42Aとを有している。さらに、半導体装置は、半導体基板10上における第1の配線41A又は第2の配線42Aの近傍領域に形成された第1のダミー配線41Bを有している。

(もっと読む)

半導体装置の製造方法

半導体装置は第1の層間絶縁膜と、前記第1の層間絶縁膜上に形成された、前記第1の層間絶縁膜よりも大きな硬度および弾性率を有する第2の層間絶縁膜とを備えた多層配線構造を有し、前記第2の層間絶縁膜上に、反射防止膜を介してレジスト膜を形成する工程と、前記レジスト膜を露光および現像してレジストパターンを形成する工程と、前記レジストパターンをマスクに、前記反射防止膜および前記多層配線構造をパターニングする工程とにより製造され、その際、前記反射防止膜として、無応力あるいは圧縮応力を蓄積する膜を使う。  (もっと読む)

(もっと読む)

半導体装置

【課題】 銅などの導電膜を用いた埋め込み配線を有した半導体装置に関し、ヴィアホール底部のボイドを抑制することができ、配線の信頼性の高い半導体装置を提供することができる。

【解決手段】 第1絶縁膜11内に形成された第1配線層13と、第1絶縁膜11上に形成された第2絶縁膜16内に形成された第2配線層と、第2絶縁膜16内に形成され第1配線層13と第2配線層とを接続するヴィアプラグ18とを備え、第1配線層13は幅1μm以上であり、ヴィアプラグ18と第1配線層13の接続部から0.5μm以内において第1配線層13内に絶縁性のダミー領域14を形成したものである。

(もっと読む)

薄膜抵抗及びタングステンプラグコネクタを利用した半導体構造並びにその作成方法

【課題】熱サイクルによってほとんど劣化しない薄膜抵抗を用いて形成される半導体構造およびその製造方法を提供する。

【解決手段】半導体構造を製造する方法は、相互接続スタックの第1の導電層の上に重なる、ほぼ平坦な表面を有する第1の絶縁層を形成することを含む。薄膜抵抗が第1の絶縁層の上に重ねて形成され、第2の絶縁層が第1の絶縁層及び抵抗の上に重ねて堆積される。第2の絶縁層の一部が除去されてほぼ平坦な表面が形成される。第2の絶縁層が異方性エッチングされて第1の導電層までの第1のバイアが形成され、タングステンを含む充填材がこの第1のバイア内に堆積される。第2の絶縁層がウェットエッチングされて薄膜抵抗までの第2のバイアが形成され、第2の導電層が、第2の絶縁層の上に重ねて、且つ第2のバイア内に堆積される。

(もっと読む)

半導体装置

銅配線におけるボイドの成長を抑制することのできる半導体装置を提供する。 半導体装置は、半導体基板と、前記半導体基板の上方に形成された絶縁層と、前記絶縁層に埋め込まれた第1ダマシン配線であって、底面および側面を画定し、内側に第1中空部を画定するバリアメタル層と、該第1中空部内に配置され、内側に第2中空部を画定する、銅配線層と、該第2中空部内に配置され、前記バリアメタル層とは分離されている補助バリアメタル層とを含む第1ダマシン配線と、前記第1ダマシン配線と絶縁層との上に配置された絶縁性銅拡散防止膜と、を有するを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】銅を主導体膜とする配線間の絶縁破壊耐性を向上させる。

【解決手段】複数の配線層N1〜Nxのうち、ウエハの主面に相対的に近い配線層N1の配線形成工程においては、埋込配線Lnの上面と絶縁膜12bの上面との間に段差が形成されるようにし、複数の配線層N1〜Nxのうち、ウエハの主面から相対的に遠い配線層Nxの配線形成工程においては、上記段差を形成する工程を経ずに、主導体膜18aの上面が絶縁膜12bの上面とほぼ一致した状態で絶縁膜15bを堆積する。これにより、TDDB寿命を向上させることができ、また、プロセス上の制約を満たすことができるので、全体的に信頼性の高い半導体装置を提供することが可能となる。

(もっと読む)

電子デバイス及びその製造方法

ビアホールが設けられた低誘電率膜の低誘電率膜の上側または下側に窒素非含有絶縁膜を挟んで窒素含有絶縁膜が形成されている電子デバイス、および、ビアホールが設けられた低誘電率膜の上側に、膜密度1.3g/cm3以下の低密度絶縁膜が設けられている電子デバイスである。

また、低誘電率膜の上側または下側に窒素非含有絶縁膜を挟んで窒素含有絶縁膜が形成されており、ホールが形成された低誘電率膜の上側に化学増幅型レジストを形成し、当該レジストを用いて前記ホールと接続する凹部を形成する工程を備えている電子デバイスの製造方法および、低誘電率膜の上側に膜密度1.3g/cm3以下の低密度絶縁膜を形成し、ホールが形成された低誘電率膜の上側に化学増幅型レジストを形成し、当該レジストを用いて前記ホールと接続する凹部を形成する工程を備えている電子デバイスの製造方法である。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の高速化を図り、また、エレクトロマイグレーションやストレスマイグレーションの発生を抑え、配線寿命を長くする技術を提供する。

【解決手段】半導体基板1上に形成された酸化シリコン膜23および窒化シリコン膜22中の配線溝内を含む酸化シリコン膜23上にバリア層26aおよび銅膜26bを順次形成後、前記配線溝外部のバリア層26aおよび銅膜26bを除去することによって配線26を形成し、配線26上にタングステンを選択成長もしくは優先成長させることにより、配線26上にタングステン膜26cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】銅を主導体層とする配線間の絶縁破壊耐性を向上させる。

【解決手段】埋込第2層配線L2に対して還元性プラズマ処理する際に、ウエハを保持する第1電極に印加する電力を、ウエハに対向する第2電極よりも低くするか零にする。これにより、埋込第2層配線L2の導電性バリア膜17aの露出面が窒化されるので、その後の配線キャップ用の絶縁膜15bの成膜時に導電性バリア膜17aの露出部が酸化されてしまうのを抑制または防止することができる。また、酸化バリア用の絶縁膜15b1を、酸素を用いないガス条件、特に酸化性の高いN2Oガスを用いない条件でのプラズマCVD法等によって堆積する。これにより、導電性バリア膜17aの酸化を抑制または防止できる。

(もっと読む)

半導体装置の製造方法

【課題】 多層配線工程において、低誘電率膜の表面に形成される変質層に起因した埋め込み不良や、リソグラフィの解像不良を抑制する。

【解決手段】 シリコン基板1上の低誘電率膜2に下層バリアメタル膜4aおよび下層金属膜5aを埋め込んだ下層配線6を形成した後、プラズマ処理により低誘電率膜2の表面に所定厚さのダメージ層7を形成する。

次に、ダメージ層7を除去して低誘電率膜2の表面に形成された変質層8の改質処理をした後に、ビアホールのエッチングストッパー膜として、第一ライナー膜を形成する。

このように形成することにより、下層配線6の上にビアホールを形成するとき、合わせずれによりビアホールの底部に低誘電率膜2が露出しても、変質層に起因した埋め込み不良や、その後に行うリソグラフィの解像不良を抑制することができる。

(もっと読む)

表示装置用配線、該配線を有する薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗特性及び信頼性を同時に確保する。

【解決手段】導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する表示装置用配線と、基板110、該基板110上に形成されているゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜140上に形成されているソース電極173を含むデータ線171及びソース電極173と対向しているドレイン電極175、及びドレイン電極175と接続されている画素電極190を有している。ゲート線とデータ線171及びドレイン電極175の少なくとも一方とは、導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する。これにより、配線の密着性が向上するので剥離を防止することができ、信頼性が向上する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗性及び信頼性を同時に確保する。

【解決手段】基板110、該基板上に形成されゲート電極124を備えるゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173を備えるデータ線及びソース電極と対向しているドレイン電極175、データ線及びドレイン電極上に形成されている保護膜180、及びドレイン電極と接続されている画素電極190を備える。ゲート絶縁膜及び保護膜の少なくとも一方の下部にケイ素を含むカバー層801、803を備えている。これにより、接着性が向上し、配線抵抗を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細・高集積化した半導体装置の多層配線に関し、従来のプロセスに大きな変更を加えずに、配線近傍でのボイド発生による断線などの障害発生を低減する。

【解決手段】多層配線の上下隣り合う上層配線と下層配線と、これらを電気的に接続するビアとの配置構造に関し、半導体基板面の垂直方向からみて、下層配線の幅とビアの断面径を同じにしたとき、ビアの断面径の中心線と下層配線の配線幅の中心線とが互いにずれるような配置構造とする。さらにそのときビアが下層配線の側壁に接するようにする。

(もっと読む)

パターン発生方法、半導体装置の製造方法、半導体装置及びプログラム

【課題】 孤立パターン周辺の領域のパターン被覆率を増加させることができるパターン発生方法を提供する。

【解決手段】 層間絶縁膜に設けられる配線パターン、及び層間絶縁膜に埋め込まれるホールパターンの配線レイアウト及びホールレイアウトを取得して、同一配線層内で配線パターンを配置するパターン処理領域においてホールレイアウトの中から配線パターンに接続されるホールパターンを抽出する。ホールパターンを含むように第1の処理領域を抽出して、第1の処理領域に含まれる配線パターンのパターン被覆率を算出する。そして、第1の処理領域にパターン被覆率に基づいて追加パターンを発生させる。

(もっと読む)

トランジスタおよびその作製方法、並びに半導体装置

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】 絶縁膜中に形成されている配線用の溝に埋め込まれている配線層の上部に選択的に金属拡散防止膜を形成する半導体装置において、部分的選択破れ等に起因する配線間リーク電流を抑制する半導体装置の製造方法を提供する。

【解決手段】 ダマシン法により配線15を第1の絶縁膜11中に形成する。そして、電解メッキ法等により、配線15上のみに選択的に金属拡散防止膜16を形成する。その後、第2の絶縁膜19形成前に、第1の絶縁膜11上に存在する部分的選択破れにより意図せず生じた金属拡散防止膜16や、残留金属イオン17等を除去するCMP工程をする。

(もっと読む)

701 - 720 / 801

[ Back to top ]