Fターム[5F033LL01]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142)

Fターム[5F033LL01]の下位に属するFターム

Fターム[5F033LL01]に分類される特許

61 - 80 / 167

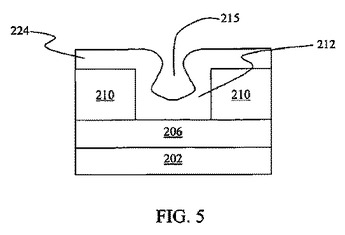

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

密着性に優れた銅合金複合膜の成膜方法およびこの成膜方法で使用するCa含有銅合金ターゲット

【課題】密着性に優れた銅合金複合膜の成膜方法を提供する。

【解決手段】Ca:0.06〜14モル%を含有し、残部がCuおよび不可避不純物からなる成分組成を有するCa含有銅合金ターゲットを用い、酸素:1〜20体積%を含む不活性ガス雰囲気中でスパッタすることによりCa:0.01〜2モル%、酸素:1〜20モル%を含有し、残部がCuおよび不可避不純物からなる成分組成を有する酸素−Ca含有銅合金下地膜を成膜し、引き続いて酸素の供給を停止してスパッタ雰囲気を不活性ガス雰囲気とし、この不活性ガス雰囲気中でスパッタすることによりCa:0.01〜2モル%を含有し、残部がCuおよび不可避不純物からなる成分組成を有するCa含有銅合金導電膜を成膜することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】デュアルストレスライナを介して開口部を形成する際に、オーバーエッチングよるダメージの影響を少なくして製造歩留まりを向上させる。

【解決手段】基板100にNFET101、PFET103、及び配線102を形成し、全面に伸張応力誘起層105を形成し、NFET101上に伸張応力誘起層105が残るようにエッチングし、全面に圧縮応力誘起層301を形成し、PFET103上及び配線上102の圧縮応力誘起層301の厚さを部分的に減少させ、全面に絶縁膜502を形成し、絶縁膜502、伸張応力誘起層105、及び圧縮応力誘起層301をエッチングして、NFET101、PFET103、及び配線102に通じる開口部501を形成する。

(もっと読む)

密着性に優れた銅合金薄膜並びにこの銅合金薄膜からなる液晶表示装置用配線および電極

【課題】液晶表示装置の配線および電極を形成するための銅合金薄膜を提供する。

【解決手段】フッ素:0.01〜5原子%を含有し、さらにCa、MgおよびZnの内の1種または2種以上を合計で0.01〜2.5原子%含有し、残部がCuおよび不可避不純物からなる成分組成を有する密着性に優れた銅合金薄膜。

(もっと読む)

半導体装置およびその作製方法

【課題】工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を提供することを課題とする。

【解決手段】多階調マスクを用いることで1つのフォトレジスト層を1枚のマザーガラス基板から遠ざかる方向に向かって断面積が連続的に減少するテーパ形状を有するフォトレジスト層を形成する。1本の配線を形成する際、1枚のフォトマスクを用い、金属膜を選択的にエッチングすることで、場所によって側面形状(具体的には基板主平面に対する角度)が異なる1本の配線を得る。

(もっと読む)

表示装置の作製方法

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、信頼性のある表示装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する表示装置の作製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたマスク層を用いてエッチング工程を行う。さらに、基板上にゲート配線層とソース配線層を同工程で形成し、ゲート配線層とソース配線層の交差部においてはソース配線層を分断(切断)した形状とする。分断されたソース配線層は開口(コンタクトホール)を介してゲート絶縁層上にソース電極層及びドレイン電極層と同工程で形成された導電層を介して電気的に接続する。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

半導体装置及びその製造方法

【課題】誘電体メモリの微細化が進むと、上部電極の電位を拡散層へ引き出す構造におけるアスペクト比が大きくなるため、上部電極のカバレッジが悪化し、誘電体を結晶化させる熱処理時に上部電極が断線してしまう。

【解決手段】半導体装置は、半導体基板の上方に形成された第1の導電膜及び第2の導電膜と、第1の導電膜を覆うように形成された第1の絶縁膜と、第2の導電膜を覆うように形成された第2の絶縁膜と、第1の絶縁膜に形成され、第1の導電膜に達する第1の開口部と、第1の開口部の壁部及び底部に沿って形成された第3の導電膜と、第3の導電膜、第1の絶縁膜、及び第2の絶縁膜上に形成された誘電体膜と、第2の絶縁膜及び誘電体膜の積層膜に形成され、第2の導電膜に達する第2の開口部と、誘電体膜の上並びに第2の開口部の壁部及び底部に沿って形成された第4の導電膜とを備える。第2の絶縁膜の膜厚が、第1の絶縁膜の膜厚よりも薄い。

(もっと読む)

集積回路チップ上の電気めっき相互接続構造

【解決課題】集積回路用のサブミクロン相互接続構造を製作する方法を提供する。

【解決手段】添加剤を含み、平坦で光沢があり延性があり低応力のCu金属を付着させるのに通常用いられる浴からCuを電気めっきすることによって、ボイドのないシームレスな導体が得られる。ボイドまたはシームを残すことなくフィーチャを超充填できるこの方法の能力は独特であり、他の付着方法より優れている。この方法で電気めっきされたCuを利用する構造のエレクトロマイグレーションの抵抗は、AlCu構造または電気めっき以外の方法で付着されたCuを用いて製作された構造のエレクトロマイグレーションの抵抗より優れている。

(もっと読む)

半導体装置およびその製造方法

【課題】微小なコンタクトを形成する場合でも、コンタクト抵抗の上昇を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に狭い間隔で配置された複数のゲート電極12と、当該ゲート電極12を被覆する層間絶縁膜20とを備える。層間絶縁膜20は、互いに隣接するゲート電極12間を充填するとともに、ゲート電極12上での膜厚が、半導体基板10の平坦面上での膜厚よりも薄い吸湿性絶縁膜15と、吸湿性絶縁膜15上に形成された非吸湿性絶縁膜16とを備える。この構造によれば、ゲート電極12間に微小なコンタクトを形成する場合でも、吸湿性絶縁膜15から放出されるH2Oに起因するコンタクト抵抗の増大を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】耐湿性をさらに向上させる。

【解決手段】半導体基板20には、中央領域24と、中央領域の周囲に周辺領域26が設定されている。半導体基板の一方の主表面である第1主面20a側の中央領域に、素子40が形成されている。半導体基板の中央領域に、第1主面から、第1主面の反対側の主表面である第2主面20bに渡って貫通分離部34が形成されている。貫通分離部内に、第1主面から第2主面にわたって貫通電極54aが形成されている。半導体基板の第1主面上に、配線絶縁膜100が形成されている。配線絶縁膜は、中央領域に素子及び貫通電極と電気的に接続された導電プラグ、及び、周辺領域に、中央領域を取り囲む周辺プラグを有している。配線絶縁膜上に、配線パターンと、配線パターンを覆う上層絶縁膜とを備えている。配線パターンは、導電プラグ間を接続する層配線、及び、周辺プラグを覆い、かつ中央領域を取り囲む周辺配線を有している。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれもCu−O−AEM(アルカリ土類金属)銅合金膜15の下地層を有するCu−AEM(アルカリ土類金属)銅合金からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Cu−Si−O−AEM(アルカリ土類金属)銅合金膜19で構成されていることを特徴とする。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれもCu−O−Zn銅合金膜15の下地層を有するCu−Zn銅合金からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Cu−Si−O−Zn銅合金膜19で構成されていることを特徴とする。

(もっと読む)

半導体装置のテスト構造物及び半導体装置

【課題】半導体装置のテスト構造物及び半導体装置を提供する。

【解決手段】半導体装置のテスト構造物は、トランジスタ150、ダミートランジスタ160、及びパッドユニットを具備する。トランジスタ150は、基板の第1アクティブ領域120上に形成される。ダミートランジスタ160は、基板の第2アクティブ領域130上に形成され、トランジスタ150に接続される。パッドユニットは、トランジスタ150に接続される。ダミートランジスタ160により、トランジスタ150が受けるプラズマダメージが減少する。

(もっと読む)

コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法

【課題】コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法を提供する。

【解決手段】本発明のコンタクト構造体の形成方法は、半導体基板上に層間絶縁膜を形成する工程と、層間絶縁膜をパターニングして半導体基板の所定領域を露出させるコンタクトホールを形成する工程と、半導体基板の主表面に対して傾斜した蒸着方向を有する蒸着法を用いてコンタクトホールの側壁にコンタクトスペーサを形成する工程と、を有する。このとき、蒸着方向は主表面と主表面に対する法線との間に位置する。それと共に、このコンタクト構造体の形成方法を用いた半導体素子の製造方法も提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

半導体装置および金属薄膜の形成方法

【課題】アルミニウム膜の流動性の低下を抑制しつつ、耐熱性を向上させる。

【解決手段】イオンビームデポジションなどの方法にて高純度アルミニウム膜15を絶縁層13上に形成した後、イオンビームデポジション法にて、添加元素17を含む添加元素膜16を高純度アルミニウム膜15上に形成し、添加元素膜16の熱処理を行うことで、添加元素膜16に含まれる添加元素17を高純度アルミニウム膜15に拡散させ、高純度アルミニウム膜15に添加元素17を添加する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体素子及びその製造方法

【課題】コンタクトプラグと配線ラインとの正確なアラインを確保しうる半導体素子及びその製造方法を提供する。

【解決手段】配線ライン168を基板10に接続するためのコンタクトホールが形成されている絶縁膜120に、ラウンド形状コーナー部Aと垂直側壁とが形成されている半導体素子。複数のコンタクトプラグが絶縁膜内のコンタクトホールを貫通して導電領域に連結されており、絶縁膜120のラウンド形状のコーナー部Aによりその幅が基板からの距離によって変化する。複数の配線ライン168がコンタクトプラグ162の上部から延びて一体型構造となる。コンタクトプラグ162と配線ライン168とを一体型に形成するためにダブルパターニング工程を用いる。

(もっと読む)

半導体素子及びその製造方法

【課題】高い信頼性を有するDRAMの半導体素子、及びその製造方法を提供する。

【解決手段】半導体素子は、基板100上のワードラインとなるゲート電極115と、ゲート電極115の側壁スペーサ118と、側壁スペーサ118によってゲート電極115から分離され、基板の不純物領域120と電気的に連結されたコンタクト160と、コンタクト160に電気的に連結されたコンタクトパッド165と、コンタクトパッド165の側面と接し、コンタクトパッド165の間に配置された保護パターン145と、コンタクトパッド165上のストレージノード170と、を含む。コンタクトパッド165は、対向するストレージノード170の底表面170bsより広い面積を有する上部表面165tsを有するように形成できるので、コンタクトパッド165の上部表面165tsは、ストレージノード170に対して十分なアライメントマージン。

(もっと読む)

61 - 80 / 167

[ Back to top ]