Fターム[5F033LL01]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142)

Fターム[5F033LL01]の下位に属するFターム

Fターム[5F033LL01]に分類される特許

121 - 140 / 167

半導体装置及び半導体装置の製造方法

【課題】製造プロセスにおけるプラズマ電流により破壊されることを防止でき、且つダイオードの耐圧が上昇してしまうことを回避した半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置10は、支持基板であるシリコン基板101aと、シリコン基板101a上の酸化膜101bと、酸化膜101b上のシリコン薄膜101cとを有するSOI基板101を用い、これのシリコン薄膜101c上に形成された入力端子IN(第2上層配線134)と、シリコン薄膜101c上に形成されたVss端子Tvss(第1上層配線139)と、シリコン薄膜101cに形成され、入力端子INとVss端子Tvssとに接続された半導体素子(例えばインバータ11)と、シリコン薄膜101cに形成され、Vss端子Tvssから入力端子INへ順方向に接続された保護ダイオード12とを有する。

(もっと読む)

電気光学装置、及び、その製造方法

【課題】 ゲート電極の膜厚を厚く形成することなく、ゲート電極の十分な遮光性と低抵抗化とを両立することができる電気光学装置を提供する。

【解決手段】 多結晶シリコン層5aと、多結晶シリコン層5aに積層する高融点金属の硅化物層5bと、硅化物層5bに積層する高融点金属層5cとを具備する多層構造の薄膜でTFT30のゲート電極3aを形成することにより、ゲート電極3aの膜厚を厚く形成することなく、十分な遮光性と低抵抗化とを両立する。すなわち、多結晶シリコン層5aの上層に積層された高融点金属の硅化物層5b及び高融点金属層5cを積層によって、ゲート電極3aの低抵抗化が実現され、同時に、硅化物層5bの上層に積層されたシリコン成分を含まない高融点金属層5cによって、TFT基板10にアニール処理が行われた場合等にも、薄い膜厚でゲート電極3aの遮光性が十分に確保される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 密着性を高める機能を併せ持つバリア層が形成されるまでの期間に、配線部材の十分な密着性を確保し、配線部材の剥離を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、凹部が設けられた層間絶縁膜を形成する。(b)凹部の内面及び層間絶縁膜の上面に密着層を形成する。(c)密着層の表面を、第1の金属元素を含むCu合金からなる補助膜で被覆する。(d)凹部内に、第1の金属元素以外の第2の金属元素を含む導電部材を充填すると共に、補助膜の上に導電部材を堆積させる。(e)熱処理を行うことにより、補助膜内の第1の金属元素の原子を、凹部の内面に偏析させる。この密着層は、層間絶縁膜の表面上に補助膜を直接堆積させた場合に比べて、補助膜の密着性を高める元素を含む。

(もっと読む)

トランジスタの製造方法およびメモリデバイスの製造方法

【課題】DRAM用アクセストランジスタの表面領域を小さくするメモリデバイスの製造方法を提供する。

【解決手段】トランジスタの製造方法の一実施形態は、基板内のゲート用溝部を規定することによってゲート電極を形成することを含む。上記ゲート用溝部に隣り合う位置での素子分離用トレンチ毎にてプレート状部がそれぞれ規定される。上記ゲート用溝部を挟む上記2つの各プレート状部が互いに連結される。上記一実施形態では、上記2つの各プレート状部は、上記半導体基板の材料に対して、上記素子分離用トレンチの絶縁材料を選択的にエッチングするエッチングプロセスによって規定される。ゲート絶縁体は、能動領域と上記ゲート用溝部との間の界面部、および、上記能動領域と上記の各プレート状部との間の界面部において設けられる。ゲート電極の材料は、上記ゲート用溝部と上記各プレート状部とを充填するように堆積形成される。

(もっと読む)

半導体装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製した半導体装置を提供することを目的とする。また配線等のパターンを所望の形状で制御性よく形成できる技術を提供することを目的とする。

【解決手段】連続した波状形状有する形状のパターンを、均一な間隔をもって隣接して備えた半導体装置である。隣接するパターンにおいて、吐出する液滴の中心の位置が線幅方向に一致しないように、配線の長さ方向にずらして吐出する。液滴の中心がずれているので、パターン同士の線幅の最大個所(節の最大値)同士が隣接することがなく、より狭い間隔に隣接したパターンを設けることができる。

(もっと読む)

半導体装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製した半導体装置を提供することを目的とする。また配線等のパターンを所望の形状で制御性よく形成できる技術を提供することを目的とする。

【解決手段】パターン材料を含む組成物からなる複数の第1の液滴を第1の線上に中心を有するように吐出し、第1の液滴の間に複数の第2の液滴を第2の線上に中心を有するように吐出して形成されたパターンを有する半導体装置である。第1の線と第2の線とが一定の距離を有するため、パターンの側端部が波状形状となる。

(もっと読む)

半導体素子の製造方法

【課題】コンタクトホールから露出する導電層間を連結するコンタクトパッドの形成の際、金属シリサイド層を用いて電気的な抵抗を低減する半導体素子の製造方法を提供する。

【解決手段】半導体基板上に第1導電層、第1層間絶縁膜、第2導電層、及び第2層間絶縁膜を順次形成し、マスク膜を食刻マスクとして用いて第2層間絶縁膜、第2導電層、及び第1層間絶縁膜を順次除去して第1導電層が露出するコンタクトホールを形成する段階と、コンタクトホールの側壁に露出した第2導電層を選択的に食刻してコンタクトホールの側壁に露出する第1層間絶縁膜と第2層間絶縁膜との間にリセスを形成する段階と、コンタクトホールの底部または側壁の少なくともいずれか一方に所定厚さの第3導電層を形成するとともに、リセスを埋める金属シリサイド層を形成する段階と、金属シリサイド層が形成された後、コンタクトホールを埋める第4導電層を形成する段階と、を含む。

(もっと読む)

薄膜トランジスター基板及びその製造方法

【課題】フレキシブル基板を用いた液晶表示装置の製造工程に際し、基板の膨張及び収縮による誤整列に備えることを可能にする。

【解決手段】ベース基板110上に形成されたゲートライン120と、ゲートラインと絶縁されて形成されたデータライン、及びゲートラインとデータラインとが交差する領域に形成され、ゲートラインの線幅は少なくとも前記データラインの線幅よりも大きく形成される薄膜トランジスターと、を備え、データラインは、前記ゲートラインと絶縁されて交差する第1のデータライン160a、160cと、第1のデータラインと交差し、その一端が第1のデータラインと電気的に接続される第2のデータライン160bと、を備え、薄膜トランジスターのドレイン電極170は、データラインと所定の間隔だけ離して配置されることを特徴とする。

(もっと読む)

エッチング液及びこれを用いた液晶表示装置の製造方法

【課題】透明導電性酸化膜用エッチング液を提供すること。透明導電性酸化膜の種類によって適用の制限が少ないエッチング液を提供すること。透明導電性酸化膜のエッチング性能を向上するエッチング液を提供すること。透明導電性酸化膜の下部に位置した膜に対する損傷が少ないエッチング液を提供すること。透明導電性酸化膜用エッチング液を用いた液晶表示装置の製造方法を提供すること。

【解決手段】本発明によると、透明導電性酸化膜のパターニングに用いられるエッチング液及びこれを用いた液晶表示装置の製造方法を提供される。透明導電性酸化膜用エッチング液は、硫酸2ないし15重量%、アルカリ金属硫酸水素塩0.02ないし10重量%及び超純水を含む。

(もっと読む)

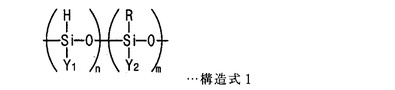

スピンオンガラス組成物、その製造方法、及びそれを用いた多孔性シリコン酸化膜の製造方法

【課題】接着特性が優秀な低誘電膜を形成するためのスピンオンガラス組成物、その製造方法、及びそれを用いた多孔性シリコン酸化膜の形成方法を提供する。

【解決手段】構造式1を有する3〜20質量%のシルセスキオキサンオリゴマー、3〜20質量%の気孔生成剤、及び残余の溶媒を含むスピンオンガラス組成物。そして、前記多孔性シリコン酸化膜を形成するために、前記スピンオンガラス組成物を基板上に塗布してスピンオンガラス薄膜を形成した後、前記薄膜を硬化して多孔性シリコン酸化膜を形成する。したがって、前記多孔性シリコン酸化膜は、接着特性が優秀であるのみならず、後続工程で過剰エッチングを招かない。 (もっと読む)

(もっと読む)

有機膜の化学的機械的研磨方法、半導体装置の製造方法、およびプログラム

【課題】 短時間で安定してレジスト膜等の有機膜を化学的機械的に研磨する方法を提供する。

【解決手段】 半導体基板上に堆積された有機膜を化学的機械的に研磨する方法である。研磨布上にスラリーを供給する工程と、研磨ヘッドに保持され、有機膜を有する半導体基板を前記研磨布に当接させる工程と、研磨布および研磨ヘッドを回転させる工程と、研磨布および研磨ヘッドを停止させる工程とを含み、前記研磨布および研磨ヘッドの回転および停止を繰り返して前記有機膜を化学的機械的に研磨することを特徴とする。

(もっと読む)

コンタクト絶縁層および異なる特性を有するシリサイド領域を形成するための技法

NチャネルトランジスタおよびPチャネルトランジスタのための金属シリサイドを別個に形成できるようにする技法が提供され、同時に、トランジスタタイプ毎に歪み誘発機構も別個に設けられる。このようにして、NMOSトランジスタ(120、220)のチャネル領域まで短い距離を有するコバルトシリサイド(130、230)を設けることができ、その一方で、Pチャネルトランジスタ(140、240)は、Nチャネルトランジスタ(120、220)の特性に過度に影響を及ぼすか、またはその特性を劣化させることなく、高導電性のニッケルシリサイド(150、250)を収容することができる。  (もっと読む)

(もっと読む)

少なくとも1つの開口部を有する最上部金属層を備える半導体素子及びその製造方法

【課題】少なくとも1つの開口部を有する最上部金属層を具備する半導体素子を提供する。

【解決手段】前記半導体素子はセルアレイ領域を有する半導体基板及び前記セルアレイ領域を有する基板を覆う層間絶縁膜を具備する。前記セルアレイ領域内の前記層間絶縁膜上部に最上部金属層が配置される。前記最上部金属層は少なくとも1つの開口部を有する。前記半導体素子の製造方法も提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置が仮に大電力用半導体のように大型のものであっても、基板上へのシリコン析出を適切に果たすことができる半導体装置及びその製造方法を提供する。

【解決手段】 拡散層2が形成されたシリコン基板3上に、開口部4が形成された絶縁膜5を設け、絶縁膜5上に、シリコン含有量が半導体装置1の金属配線層形成以降の製造工程で印加される最高温度で(450℃程度)での固溶限以上とされたアルミニウム合金膜からなる第1の電極層6が、開口部4を通して拡散層2に接続されるように形成され、第1の電極層6上に、純シリコン膜からなる第2の電極層7が形成され、第2の電極層7上に、純アルミニウム膜からなる第3の電極層8が形成されて、半導体装置1が構成されている。拡散層2のシリコンが第1の電極層6に固溶していくことがなく、かつ、第1の電極層6中の過剰のシリコンが第2の電極層7の界面に析出することから、拡散層2上へのシリコンの析出を大きく抑制できる。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

表示装置、その製造方法、及びその製造方法で使用されるマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体素子の製造方法

【課題】半導体素子の製造方法を提供する。

【解決手段】(a)リセスゲート118の突出部120とディープトレンチキャパシタ素子102の上部104とが露出した状態で、リセスゲートとディープトレンチキャパシタ素子とを有する基板100を準備する工程と、(b)ディープトレンチキャパシタ素子の上部とリセスゲートの突出部の側壁を取り囲むスペーサ124を形成する工程と、(c)スペーサの間隙126に埋込部130を形成する工程と、(d)パターンニングにより、平行なシャロートレンチを形成して活性領域を規定する工程と、(e)シャロートレンチ中に誘電材料の層を形成し、埋込部のいくつかを埋込ビット線コンタクトとする工程と、(f)リセスゲートと重なり合う部分を含むと共に、前記重なり合う部分が少なくとも1つのリセスゲートの幅よりも狭くなるように、ワード線をリセスゲートに交差させて形成する工程とを含む半導体素子の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 水素によるキャパシタ誘電体膜の劣化を防止することが可能な半導体装置の製造方法を提供すること。

【解決手段】 シリコン(半導体)基板1の上に下地絶縁膜10を形成する工程と、下地絶縁膜10の上に、下部電極11a、キャパシタ誘電体膜12a、及び上部電極13aを順に形成してなるキャパシタQを形成する工程と、キャパシタQを覆う第1層間絶縁膜15を形成する工程と、第1層間絶縁膜15の上に、シリコン基板1にバイアス電圧を印加しないプラズマCVD法により第1保護絶縁膜16を形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】より高性能、高信頼性の記憶装置、及びその記憶装置を備えた半導体装置を低コストで、歩留まりよく作製できる技術を提供することも目的とする。

【解決手段】半導体装置に含まれる記憶素子を構成する有機化合物層と、有機化合物層を挟んで形成される一対の導電層において少なくとも一方の導電層との間に複数の絶縁物が存在するように、一対の導電層において少なくとも一方の導電層が複数の絶縁物を含むように形成する。本発明の記憶装置の一は、複数の絶縁物を含む第1の導電層と、複数の絶縁物を含む第1の導電層上に有機化合物層と、有機化合物層上に第2の導電層とを有する。

(もっと読む)

小さく、スペースの狭い構成物の配列を形成する方法

集積回路に用いるための、小さく高密度に間隔をあけた孔もしくは支柱の配列を形成するための方法を開示する。高密度に充填された構成物を形成するために、様々なパターン転写ステップ、および、エッチングステップを、ピッチ減少化技術と組み合わせて用いることができる。一つの層に統合することができる、交差し引き伸ばされた構成物のピッチが減少しているパターンの重ね合わせたものを形成するために、従来のフォトリソグラフィーステップをピッチ減少化技術と組み合わせて用いることができる。 (もっと読む)

121 - 140 / 167

[ Back to top ]