Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

2,001 - 2,020 / 2,960

接合用の隣接収納部を有する半導体相互接続、及び形成方法

半導体デバイス(10)及び方法に関するものであり、半導体デバイス(10)は隣接する収納開口部(44,46,48)を持つ相互接続(38,40,42)を有する。誘電体層(20)は一つ以上の相互接続層(18)の内の最上部相互接続層の一部分として形成される。開口部(30)を誘電体層に形成することにより、誘電体層の改質部分(32)が開口部の側壁の一部分に沿って形成される。開口部には金属のような導電材料が充填される。誘電体層(20)の露出部分(22)を除去して、誘電体層よりも上に延びる導電材料の突出パッド(38,40,42)を形成する。収納開口部は、誘電体層の改質部分を除去することにより突出パッドに隣接して形成される。半導体デバイスを別の半導体デバイス(100)に、すなわちウェハまたはチップに接合する場合、横方向に流動する金属は収納開口部に集められるので、確実に、信頼性の高い電気接続が半導体デバイスと他のデバイスとの間で行なわれる。  (もっと読む)

(もっと読む)

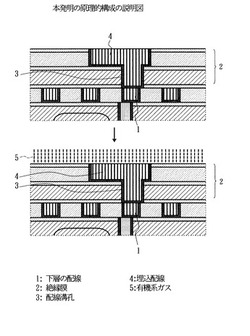

埋込配線の形成方法

【課題】 埋込配線の形成方法に関し、信頼性が高く且つ抵抗上昇が発生しない歩留りの高い埋込多層配線を提供する。

【解決手段】 配線溝孔3に埋め込んだ導電体層を研磨して埋込配線4を研磨したのち、気体状態の有機系ガス5により前記埋込配線4の露出部表面の清浄化・熱処理を行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線からのCuの拡散を防止する。

【解決手段】例えば、UDC拡散バリア膜22、ポーラスシリカ膜23、UDCミドルストッパ膜24、ポーラスシリカ膜25およびUDC拡散バリア膜26の積層構造にビア溝27aと配線溝27bを形成したときに、内部に露出するUDC拡散バリア膜22、UDCミドルストッパ膜24、UDC拡散バリア膜26の表面に対し、水素プラズマを照射する。これにより、各SiC膜の露出表面をSiリッチにする。そして、プラズマ照射後のビア溝27aと配線溝27bにTa膜28を形成し、Cuで埋め込む。Ta膜28と接触することとなるSiC膜の表面をあらかじめSiリッチな状態にしておくことにより、Ta膜28をCuの突き抜けが抑えられるような結晶構造に制御することが可能になる。これにより、配線からのCuの拡散を防止することが可能になる。

(もっと読む)

半導体装置

【課題】Cu配線などの金属配線について、金属配線と金属拡散防止膜との密着性が向上し、金属配線のエレクトロマイグレーション耐性向上により金属配線寿命の長い半導体装置を提供する。

【解決手段】半導体基板上に形成された第1の絶縁膜中の溝部内に設けられ、銅および銅の合金のうち少なくとも1つを含有する第1の金属配線と、第1の金属配線および第1の絶縁膜の露出面を覆う第1の金属拡散防止膜を有する半導体装置において、第1の金属配線は金属シリサイド層を含有しないシリコン含有金属配線であり、第1の金属配線全体にシリコンを含む構成である。

(もっと読む)

絶縁膜形成用組成物、半導体装置用絶縁膜、その製造方法および半導体装置

【課題】低誘電率で、かつ、優れた耐ストレス性と優れた耐クラック性とを有する半導体装置用絶縁膜を得ることができる絶縁膜形成用組成物、その絶縁膜形成用組成物から得られる半導体装置用絶縁膜および、その半導体装置用絶縁膜を利用して得られる高品質で信頼性の高い半導体装置を歩留まりよく提供する。

【解決手段】 本絶縁膜形成用組成物は、実質的に炭素とケイ素と水素とのみからなる鎖部分を主鎖とし、かつ、主鎖以外の部分に窒素を含有するポリマーを含んでなる。ポリマー中に、窒素が、式1で表される構造要素として存在することが好ましい。

【化17】 (もっと読む)

(もっと読む)

電子部品の製造方法

【目的】シード膜の溶解を抑制し、電解めっき後のめっき膜の未析や欠陥の発生を低減する方法を提供することを目的とする。

【構成】本発明の一態様の電子部品の製造方法は、基板上にシード膜を形成するシード膜形成工程(S110)と、前記シード膜を冷却する冷却工程(S112)と、冷却された前記シード膜をめっき液に浸漬させ、前記シード膜をカソードとして電解めっきを行なうめっき工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】デュアルダマシン法により形成された埋め込み配線を有する半導体集積回路装置の製造工程において、銅配線の接続部分での接続特性の信頼性の向上した埋め込み配線を形成する。

【解決手段】接続孔25Aおよび配線溝28を形成し、接続孔25Aおよび配線溝28の側壁および底部にバリア導電性膜31Aを成膜した後、接続孔25Aの底部のバリア導電性膜31Aを除去し、さらに接続孔25A下の埋め込み配線15の一部を掘り込む。その後、接続孔25Aおよび配線溝28の深さ方向におけるスパッタリング粒子の指向性を向上させた条件下で、スパッタリング法にて配線溝28および接続孔25A内を含む層間絶縁膜19上にタンタル膜を堆積し、配線溝28の底部のバリア導電性膜31Aの膜厚を増加し、接続孔25Aの底部を再びバリア導電性膜31Aで覆う。

(もっと読む)

半導体装置の製造方法

【課題】バリア層を介して高融点金属シリサイド層に接続するタングステンからなるプラグを有する半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】半導体ウエハSWの主面上に形成されたコバルトシリサイド層を覆う層間絶縁膜を形成し、コバルトシリサイド層に達する接続孔を層間絶縁膜に形成した後、実質的に窒素を含まない雰囲気のチャンバ22で、接続孔の内部を含む層間絶縁膜上にチタン膜をスパッタリング法により形成し、続いてチャンバ23で、接続孔の内部を含むチタン膜上に窒化チタン膜をスパッタリング法により形成する。その後、チャンバ24で半導体ウエハSWにアニール処理を施し、続いて接続孔の内部にタングステンを主導電材料とするプラグを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッド部のパッド剥がれを抑制した半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、層間絶縁膜8上にバリアメタル層14を形成する工程と、パッド開孔部の下に位置する前記バリアメタル層の少なくとも一部を除去する工程と、前記除去する工程により露出した層間絶縁膜8及び前記バリアメタル層14の上に第2のAl合金膜15を形成する工程と、第2のAl合金膜及び前記バリアメタル層をパターニングすることにより、前記層間絶縁膜上にボンディングパッド部17aを形成する工程と、前記ボンディングパッド部及び前記層間絶縁膜の上にパッシベーション膜18を形成する工程と、前記パッシベーション膜に、前記ボンディングパッド部上に位置するパッド開孔部を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】 二重露光を用いて微細化を図れる半導体装置の製造方法を提供すること。

【解決手段】 第1のパターンを含むメモリセル領域と、第2のパターンを含む周辺回路領域を備えた半導体装置を製造する際に、メモリセル領域と周辺回路領域を含む基板の領域上にレジスト膜を形成し、メモリセル領域上のレジスト膜中に第1のパターンに対応した潜像を形成するための第1の露光と、周辺回路領域上のレジスト膜中に第2のパターンに対応した潜像を形成するための第2の露光を含む多重露光により、レジスト膜を露光する際に、レジスト膜上における第1の露光と第2の露光の境界領域12を、ガードリング5,7間の素子分離領域10’上に設定し、レジスト膜を現像してレジストパターンを形成し、レジストパターンをマスクにして被加工基板をエッチングする。

(もっと読む)

低減された誘電率を有する誘電体の製造方法、および半導体デバイス構成要素、および基板

【課題】低減された誘電率を有する誘電体、およびその製造方法を提供する。

【解決手段】第1の態様では、低減された誘電率を有する誘電体を製造する第1の方法を提供する。第1の方法は、(1)基板上のトレンチを含む誘電体層を形成するステップと、(2)誘電体の実効誘電率を減少させるために、トレンチの側壁および底部のうちの少なくとも一方に沿って、誘電体層内に複数の空隙を形成することにより、誘電体層内にクラッディング領域を形成するステップとを含む。他の多数の態様を提供する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】 Cu膜と絶縁膜との間に所定幅の空気層が設けられた配線構造で信頼性が高い半導体装置を提供することである。

【解決手段】 配線膜4の側部に空気層5および固体絶縁層1が構成された配線構造の半導体装置であって、

配線膜4と固体絶縁層1との間に空気層5が配線膜4に隣接して設けられてなり、

配線膜4と固体絶縁層1との間に設けられた空気層5は幅が5〜100nmであり、

配線膜4と配線膜4との間の固体絶縁層1は幅が10〜500nmである。

(もっと読む)

半導体装置及びその製造方法

【課題】積層された導電性バリア層の酸素バリア性を向上させると共に、積層された導電性バリア層に生じる浮きや剥離を防止してコンタクト抵抗の安定化を図る。

【解決手段】半導体装置は、容量素子21とトランジスタのソース領域又はドレイン領域13とを電気的に接続するコンタクトプラグ15と、該コンタクトプラグ15の上に形成された高融点金属のみの窒化物である窒化チタンからなる導電層16Aと、窒化チタンアルミニウム膜、イリジウム膜及び酸化イリジウム膜の積層膜からなる酸素の拡散を防止する多結晶状の導電性酸素バリア層17とを有している。結晶配向性が低い窒化チタンからなる導電層16Aを導電性酸素バリア膜17の下側に設けたことにより、導電層16Aの直上に形成される導電性酸素バリア膜である窒化チタンアルミニウム膜は緻密な膜構造となるため、酸素の侵入を効果的に防止することができる。

(もっと読む)

埋込配線の形成方法

【課題】 埋込配線の形成方法に関し、信頼性が高く且つ抵抗上昇が発生しない歩留りの高い埋込多層配線を提供する。

【解決手段】 配線溝孔3をエッチングした後に、バリア膜及びメッキシード層を成膜し、次いで、配線溝孔3をメッキ法により導電体層4で埋め込んだのち、気体状態の有機系ガス5により導電体層4の熱処理を行う。

(もっと読む)

半導体装置の相互接続構造およびその方法

【課題】本発明は、ILDの異なる密度の区域間において、不純物の均等な分布を実現できるようにする。

【解決手段】たとえば、不必要な不純物を吸収できるキャップ絶縁体201をILD100上に付着する。複数のトレンチを、前記ILD100の高密度部分101aおよび低密度部分101bと前記キャップ絶縁体201とに形成する。そして、前記部分101a,101b中のトレンチの集中度の比較にもとづいて、前記高密度部分101a上の前記キャップ絶縁体201を除去し、前記キャップ絶縁体201を前記低密度部分101b上にのみ残留させる。

(もっと読む)

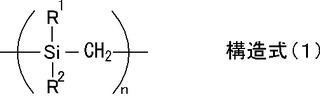

露光光遮蔽膜形成用材料、多層配線及びその製造方法、並びに半導体装置

【課題】多層配線、半導体装置等に好適に用いられ、露光光、例えば紫外線の吸収性が高い露光光遮蔽膜形成用材料等の提供。

【解決手段】露光光遮蔽膜形成用材料は、構造式(1)で表されるシリコン化合物及び構造式(2)で表されるシリコン化合物のいずれかを含んでなり、R1及びR2のいずれかが露光光を吸収可能な置換基で置換されている。

(R1、R2及びR3は水素原子並びにアルキル基、アルケニル基、シクロアルキル基及びアリール基のいずれかを表す。nは2以上の整数を表す。)

(もっと読む)

半導体装置の製造方法

【課題】化学増幅型レジストの反応阻害物質によるレジストポイゾニングの発生を抑え、信頼性が高い配線構造を有する半導体装置を実現できるようにする。

【解決手段】半導体装置の製造方法は、基板の上に第1の絶縁膜21を堆積する工程と、第1の絶縁膜21に溝部を形成した後、形成した溝部に導電性材料を埋め込むことにより第1の配線22を形成する工程と、第1の絶縁膜21の上に第2の絶縁膜23を形成する工程と、第2の絶縁膜23に対して加熱状態で紫外線を照射する工程と、第2の絶縁膜23の上に第3の絶縁膜25を形成する工程と、第3の絶縁膜25の上にレジストパターン31を形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】エアギャップ構造において酸化に起因する配線信頼性劣化を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、基板1上に形成された第1配線5と、第1配線5の上層に形成され、第1配線5との間にエアギャップ20を介在させて配置された第2配線16と、エアギャップ20内に形成され、第1配線5と第2配線16とを接続するカーボンナノチューブ11とを有する。

(もっと読む)

配線構造とその製造方法及び半導体装置

【課題】 Cu拡散性が良好で、耐熱性、電気特性、特に誘電率、接着性等に優れた多層配線構造、及びこれを具備した、電気特性に優れる半導体装置を提供する事を目的としてなされたものである。

【解決手段】 (1)絶縁膜に形成した溝に銅層又は銅を含む合金層を形成する工程、及びバリアメタル層を形成する工程、

(2)前記銅層又は銅を含む合金層の表面を、Co又はNi又はWを含む金属層で構成されるキャップ層を形成する工程、(3)銅拡散防止能を有する有機系絶縁材料層を形成する工程、を有することを特徴とする配線構造の製造方法。前記製造方法を用いて作製した銅層又は銅を含む合金層を有する配線構造。前記配線構造を具備する半導体装置。

(もっと読む)

半導体デバイスで用いられるキャパシタとその製造方法

【課題】従来技術にかかる構造、および製造プロセスの欠点を回避するキャパシタ構造と、その製造方法を提供する。

【解決手段】半導体ウェハの基板上に形成された食刻相互接続構造(damascene)を有する半導体デバイスで使用される本発明のキャパシタは、食刻相互接続構造の一部を含む第1キャパシタ電極164と、食刻相互接続構造の上に形成され、パッシベーション層として機能する絶縁層166と、絶縁層の少なくとも一部の上に形成された導電層を含む第2キャパシタ電極168とを有する。

(もっと読む)

2,001 - 2,020 / 2,960

[ Back to top ]