Fターム[5F033MM30]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 基板内部や裏面に配線が有るもの (1,122)

Fターム[5F033MM30]に分類される特許

201 - 220 / 1,122

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置、及びその製造方法、並びに電子情報機器

【課題】シールリング構造を有し、半導体基板の一部を除去した半導体チップにおいて、シールリング構造を構成するプラグが、半導体基板を除去した部分で露出することによる耐湿性の劣化を回避する。

【解決手段】半導体ウエハを分割して得られる半導体チップ100において、半導体基板101上に形成された機能回路を含む回路形成領域Crと、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造Shとを備え、該シールリング構造Shは、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグ104c及び105cを有し、該シールリング構造を構成する最下層の導電性プラグ104cは、該半導体基板に代わる耐湿材料層102c上に配置されている。

(もっと読む)

貫通電極基板

【課題】 貫通電極を細くすると、基板に形成した貫通孔を金属材料で埋め込むことが困難になる。また、体積の大きな金属部材が基板内に埋め込まれると、熱膨張係数の差に起因して、機械的な破壊が生じやすくなる。

【解決手段】 基板の第1の表面に、第1の導電膜を含む積層膜が形成されている。基板の、第1の表面とは反対側の第2の表面から内部に向かって、第1の表面までは達しない凹部が形成されている。凹部の底面から第1の表面まで達する貫通孔が形成されている。この貫通孔は、凹部よりも細い。貫通孔内に第2の導電膜が埋め込まれている。第2の導電膜は、第1の導電膜に接続され、凹部の側面及び底面を覆うが、凹部を完全には埋め尽くしていない。

(もっと読む)

半導体装置

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

貫通配線基板の製造方法

【課題】貫通配線基板の両面に実装するデバイスの電極配置が多様で且つ高密度である小型のデバイスであっても、実装するデバイス間の電極を自由度高く電気的に接続することが可能な貫通配線基板及びその製造方法の提供。

【解決手段】第1面1と第2面2とを有する基板と;第1面及び第2面の間を貫通する貫通孔内に、導電性物質を充填又は成膜して形成された複数の貫通配線12a,12bと;を備え、貫通配線同士は、互いに離間し、且つ基板の平面視において、重なり部分を少なくとも1つ備え、基板の第1面側又は第2面側からレーザー照射して、貫通孔を形成する領域を改質する工程Aと;前記改質された領域を除去して、貫通孔を形成する工程Bと;を含み、工程Aにおいて、複数の貫通孔形成領域のうち、レーザーの入射面から遠い方の重なり部分をレーザー照射した後に、レーザーの入射面から近い方の重なり部分をレーザー照射する貫通配線基板の製造方法。

(もっと読む)

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

ビアホールの加工方法およびレーザー加工装置

【課題】ボンディングパッドに穴を開けることなくウエーハの基板にボンディングパッドに達するビアホールを形成することができるビアホールの加工方法およびレーザー加工装置を提供する。

【解決手段】基板の表面に複数のデバイスが形成されているとともにデバイスにボンディングパッドが形成されているウエーハに、基板の裏面側からパルスレーザー光線を照射してボンディングパッドに達するビアホールを形成するビアホールの加工方法であって、基板のボンディングパッドが形成された領域の厚みを計測する厚み計測工程と、ウエーハの基板の裏面側からパルスレーザー光線を照射して基板にレーザー加工孔を形成するレーザー加工孔形成工程とを含み、レーザー加工孔形成工程は厚み計測工程によって計測された基板の厚みと、パルスレーザー光線の1パルス当たりのエネルギーに基づいて、パルスレーザー光線のショット数を決定する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

固体撮像装置及び電子機器

【課題】隣接カップリング容量を抑制した固体撮像装置及びこの固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】半導体チップ部が貼り合わされ、第1の半導体チップ部に画素アレイと第1多層配線層が形成され、第2の半導体チップ部にロジック回路と第2多層配線層が形成された積層半導体チップを有する。半導体チップ間を接続する複数の接続配線67と、一方向に隣り合う接続配線67間をシールドする第1シールド配線113とを有する。各接続配線67は、第1多層配線層内の所要の第1配線に繋がる第1の接続パッドに接続された接続導体68と、第1の半導体チップ部を貫通して第2多層配線層内の所要の第2配線に繋がる第2の接続パッドに接続された貫通接続導体69を有する。接続配線67は、接続導体68と貫通接続導体とを連結する連結導体とを有して形成される。固体撮像装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置およびその製造方法

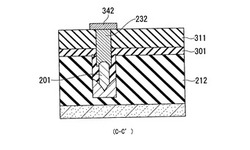

【課題】センシング部を複数の基板で封止した半導体装置において、基板の平面方向に配線を設けたとしても、配線のレイアウトを簡略化することができる構造、およびその製造方法を提供する。

【解決手段】キャップ部300は、センサ部100に設けられた第1固定部と第2固定部とを電気的に接続したクロス配線部323を備え、クロス配線部323はキャップ部300の一面301に配置されたクロス配線322を備えている。また、キャップ部300は、キャップ部300を貫通し、一端がクロス配線322に電気的に接続され、他端がキャップ部300の他面302に配置された貫通電極344を備えている。これにより、貫通電極344を介してクロス配線322の電位、すなわち、センサ部100の第1固定部および第2固定部の電位をキャップ部300の他面302に取り出すことができる。

(もっと読む)

半導体装置、およびその製造方法、ならびにデータ処理装置

【課題】テーパー部を有する溝を備えた半導体装置を容易に形成する。溝内に空洞が形成されるのを防止すると共に、製造歩留まりの低下を抑制する。

【解決手段】半導体装置は、第1の面を有する材料層と、材料層内に設けられ、第1の面に開口部を有する溝を備える。溝は、開口部に接し1以上のスキャロップ形成溝を有するテーパー部と、おおむね垂直な側壁を有する垂直部を有する。スキャロップ形成溝の幅は、垂直部の溝幅よりも大きくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】更なる微細化に対応した高集積度のDRAMを得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2の表層に、第1の方向Yに延在する第1の溝部3と、第2の方向Xに延在し且つ第1の溝部3よりも深くなる第2の溝部5と、第1の溝部3と第2の溝部5との交差部分において第2の溝部5よりも深くなる第3の溝部7と、第1の溝部3と第2の溝部5との間から突出されたピラー部8と、ピラー部8に形成された下部拡散層9、チャネル領域10及び上部拡散層11と、第2の溝部5の内側において第2の方向Xに延在するビット配線層と、第1の溝部3の内側においてピラー部8の側面を覆うゲート絶縁膜と、第1の溝部3の内側においてゲート絶縁膜を介してピラー部8の側面を横切るように第1の方向Yに延在するワード配線層とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

半導体装置の製造方法

【課題】深さが深く幅が狭い溝の深さを把握できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に平面視環状の複数の環状溝2を形成する環状溝形成工程と、環状溝2の下端よりも下層に配置された半導体基板1を介して、複数の環状溝2から選ばれた第1環状溝2aの平面視内側表面と、第1環状溝2aとは別の環状溝2である第2環状溝2bの平面視内側表面との間の抵抗を測定し、実測抵抗値を得る抵抗測定工程と、実測抵抗値を用いて環状溝2の深さを算出する算出工程とを備える半導体装置の製造方法とする。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

201 - 220 / 1,122

[ Back to top ]