Fターム[5F033NN11]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクト部の配線構造の特徴 (690)

Fターム[5F033NN11]の下位に属するFターム

接触構造 (642)

Fターム[5F033NN11]に分類される特許

1 - 20 / 48

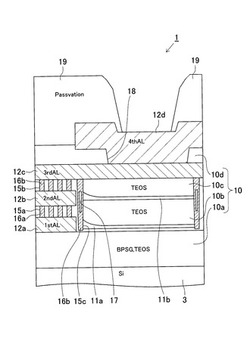

半導体装置及び半導体装置の製造方法

【課題】クラックの発生を抑制できるとともに、SOG膜の剥離を抑えることが可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された半導体基板3上に、SOG膜を含む層間絶縁膜10が形成されており、この層間絶縁膜10を介して、配線層12a〜12dが半導体素子と電気的に接続されている。さらに、一方面側がボンディング接続されるパッド部12d(第4配線層12d)と、層間絶縁膜10に配置されると共に配線層12a〜12cを接続するビアホール15a〜15cと、ビアホール15a〜15c内に埋め込まれる導電層16a、16bとを有している。そして、ビアホール15a〜15cは、パッド部12dよりも下方に設けられており、導電層16a、16bの少なくとも一部は、内部に空洞部17を有している。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】

支持基板上に形成された第1導電層と、層間絶縁層上に形成された第2導電層とをコンタクトホールによって電気的に接続した半導体装置において、安価に、前記第1導電層と第2導電層とのコンタクト不良を抑制した半導体装置及びその製造方法を提供する。

【解決手段】

開口部内における第1導電層102の状態は、開口部端部付近102bよりも中心部付近102cにおいて表面粗さがより大きい、もしくは導電性は薄膜の粒径がより大きくなるように形成されている。従って、コンタクトホール104における第1導電層102と第2導電層105との電気的接続が良好となってコンタクト不良の発生を抑制可能としている。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の信頼性の高い半導体装置を提供する。

【解決手段】半導体基板42上に台形状の凸部領域と台形状の凹部領域を設け、凹部領域のシリコン表面にはゲート酸化膜45が設けられ、ゲート酸化膜上にはゲート電極46が形成されている。凹部領域に設けられたゲート電極46の両側の凸部領域にはソース・ドレイン高濃度領域48が位置し、ソース・ドレイン高濃度領域48とゲート電極46の間にはソース・ドレイン低濃度領域47が形成されている。ソース・ドレイン高濃度領域48の上表面には第1層目の金属配線49と第2層目の金属配線50と第3層目の金属配線52が積層され、ソース・ドレイン高濃度領域48から第3金属配線までの接続にコンタクトホールやビアホールなどを利用していない。このように本発明の半導体装置は、コンタクトホールやビアホールなどの接続孔を形成しないで素子と配線との接続や配線間接続を行なうことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

回路基板の製造方法および回路基板

【課題】配線構造が積層化された回路基板において、回路特性の劣化を防止できる製造方法を提供する。

【解決手段】基板1上に下層配線パターン3を形成し、下層配線パターン3を覆う状態で絶縁膜5を形成し、この絶縁膜5に下層配線パターン3を露出する開口部5aを形成する。絶縁膜5上に上層配線パターン7を形成し、その後下層配線パターン3と上層配線パターン7とを接続する接続材料パターン9を絶縁膜5の開口部5aの側壁に形成する。接続材料パターン9は、例えば有機半導体材料を用いて形成する。これにより、有機半導体材料からなる接続材料パターン9の劣化を防止した回路基板11-1が得られる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】階段状に加工された複数層の電極層とコンタクト電極との接触抵抗を低減する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、電極層WL1〜WL4と絶縁層25とを交互に複数積層する工程と、その積層体の一部を階段状に加工すると共に各段の表面に電極層WL1〜WL4を露出させる工程と、露出された電極層WL1〜WL4に接する金属膜43を形成する工程と、電極層WL1〜WL4における少なくとも金属膜43と接する部分に金属化合物44を形成する工程と、金属膜43の未反応部を除去した後層間絶縁層46を形成する工程と、層間絶縁層46を貫通しそれぞれが対応する各段の電極層WL1〜WL4の金属化合物44に達する複数のコンタクトホール47を形成する工程と、コンタクトホール47内にコンタクト電極50を設ける工程とを備えた。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

多層配線基板及びそれを備えた半導体装置

【課題】遮光領域を抑制することにより、開口率の低下を防止するとともに、製造工程を簡素化することができる多層配線基板及びそれを備えた半導体装置を提供することを目的とする。

【解決手段】TFT基板1は、第1コンタクトホール11が形成された第1絶縁膜8と、第1絶縁膜8の表面及び第1コンタクトホール11の表面に形成された第1配線層14と、第2コンタクトホール15が形成された第2絶縁膜9と、第2絶縁膜9上に積層されるとともに、第2絶縁膜9の表面及び第2コンタクトホール15の表面に形成され、第1配線層14と導通された第2配線層16とを備えている。そして、第1及び第2コンタクトホール11,15が、TFT基板1の上下方向Xにおいて重なった状態で直線的に配置され、第1コンタクトホール11において、第1配線層14上に絶縁性樹脂25が充填されている。

(もっと読む)

自己整合ローカル・インターコネクト・プロセスにおけるゲートへの選択的なローカル・インターコネクト

【解決手段】

半導体デバイス生産プロセスは、ハードマスク(112)を用いて半導体基板上にトランジスタのゲート(102)を形成することを含む。ハードマスクは、ゲート上の1つ以上の選択された領域で選択的に除去される。選択された領域でのハードマスクの除去によって、実質的にトランジスタ上にある少なくとも1つの絶縁層を通してゲートが上部金属層に接続できる。導電性材料が、少なくとも1つの絶縁層を通して形成された1つ以上のトレンチ内に堆積される。導電性材料は、少なくとも1つの選択された領域内でゲートへのローカル・インターコネクトを形成する。

(もっと読む)

半導体装置

【課題】異なる配線層内に設けられた配線同士をコンタクト部を介して接続する際に、コンタクト部の特定の部分への電流集中を回避しうる構造を提供する。

【解決手段】半導体装置は、下層配線2と、配線部分32、及び配線部分32より配線幅の広い第1の幅広部22を有する上層配線1と、下層配線2と第1の幅広部22とを接続するコンタクト部3が配置されたコンタクト形成部26とを備えている。コンタクト形成部26は、第1の幅広部22の配線幅方向に平行な方向の長さL1が第1の幅広部22の配線長方向に平行な方向の長さL2よりも長い平面形状を有する。

(もっと読む)

三次元積層型半導体集積回路及びその製造方法

【課題】スルーシリコンビアの高密度化、製造歩留りの向上及び製造コストの低減を同時に実現する。

【解決手段】本発明の例に係る三次元積層型半導体集積回路は、同一方向を向いて互いに積み重ねられる第一及び第二チップC1,C2と、第一チップC1を構成する第一半導体基板21及び第二チップC2を構成する第二半導体基板21を貫通し、かつ、第一チップC1内に設けられる半導体素子に繋がる第一電極14を貫通するスルーシリコンビア13とを備える。第一及び第二チップC1,C2は、面で結合する。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

1 - 20 / 48

[ Back to top ]