Fターム[5F033NN31]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | 断面が長方形以外 (728) | 上部を拡大、コンタクトパッド (511)

Fターム[5F033NN31]の下位に属するFターム

順テーパー部を有する (393)

Fターム[5F033NN31]に分類される特許

61 - 80 / 118

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタのコンタクト抵抗を低減する。

【解決手段】半導体装置70には、半導体基板1上に複数の絶縁ゲート型電界効果トランジスタが設けられる。絶縁ゲート型電界効果トランジスタのゲートの間に形成され、側面が側壁絶縁膜8及び絶縁膜9により絶縁ゲート型電界効果トランジスタのゲートと分離された自己整合コンタクト開口部の底部には凹部形状のポリシリコンプラグ11が設けられる。ポリシリコンプラグ11上にはバリアメタル膜12が設けられる。バリアメタル膜12上には、自己整合コンタクト開口部を覆うように金属プラグ13が埋設される。

(もっと読む)

半導体基板接続ビア

第1導電層(104)とシリケートガラス層(106)の縁部を互いに隣接させて、半導体基板(41)まで延在するビア(164)に沿って延在させる。導電体(114/116)は、ビア(164)を通り延在して、半導体基板(41)と接触する。 (もっと読む)

半導体パッケージおよびその製造方法

【課題】半導体素子の性能劣化を引き起こすことなく、小型化が可能かつ高信頼性を有する安価なウエハレベルCSPの半導体パッケージを提供する。

【解決手段】半導体パッケージ100であって、半導体基板の第1の面に配置された電極パッド106と、前記半導体基板の第2の面から該電極パッドが露出するように、該電極パッド直下の該半導体基板内に開けられた貫通孔と、前記半導体基板の第2の面と該貫通孔の内側面とを覆い、前記電極パッドが露出するように配置された電気絶縁膜と、該電気絶縁膜を介して、前記貫通孔の内側面及び前記電極パッドの露出部を覆うように配置され、該電極パッドと電気的に接続された金属薄膜からなる貫通電極108と、該貫通電極と前記半導体基板の第2の面101bに設けられた外部配線領域とを接続するために貫通電極から延長された外部配線109と、該外部配線領域に外部端子と接続するための接続部111と、を有する。

(もっと読む)

半導体集積回路装置

【課題】良好に接続できるようにする。

【解決手段】層間絶縁膜22,29に形成された1つのコンタクトホール51、53につき複数のボトムゲートライン41の配線端子がそのコンタクトホール51,53内にあり、1つのボトムゲートライン41につき1つの中継パッド52,54が被覆し、1つのコンタクトホール56につき1つの中継パッド54がそのコンタクトホール56内にあり、1つの中継パッド54につき1つの表面パッド56がコンタクトホール56内で接している。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留りが高く且つ配線間容量を十分に低減でき、且つ機械的強度を十分に得られるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の配線105と、第1の層間絶縁膜101に複数の配線105の少なくとも1つと接続するように形成されたビア113及びダミービア106とを有している。第1の層間絶縁膜101における互いに隣り合う配線105同士の間には空隙部109が選択的に形成されており、ダミービア106は、空隙部109と接する配線105Aの下側に該配線105Aと接続して形成され、ビア113及びダミービア106は、空隙部109を介することなく第1の層間絶縁膜101により周囲を覆われている。

(もっと読む)

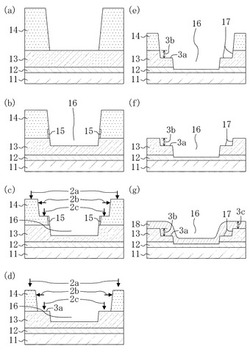

半導体装置の製造方法

【課題】レジストマスクを用いたフォトリソ工程を追加することなく、微細な容量コンタクトプラグ上部の面積を拡大させることが可能なCOB型DRAMの製造方法を提供する。

【解決手段】製造方法は、層間膜8にコンタクトホールを形成後、コンタクトホールに第一の導電材料を埋め込みエッチバックして、第一のコンタクトプラグ10を形成する工程、層間膜8をエッチングして第一のコンタクトプラグ10上部を露出させる工程、及び、層間膜8及び第一のコンタクトプラグ10上に第二の導電材料を成膜しエッチバックして、自己整合的に第一のコンタクトプラグ10上部周囲に第二の導電材料11を残すことで、プラグ10上部を拡大した第二のコンタクトプラグを形成する工程、とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線コンタクトの接続不良や高抵抗不良等の発生を防止する。

【解決手段】本発明の半導体装置は、半導体基板1上に不揮発性のメモリセルを行列状に配置したメモリセルアレイを備え、各メモリセルにおけるビット線コンタクトCBを1つおきにビット線方向にずらして2列に配置するように構成し、ビット線コンタクトCBを、活性領域3に下端を接続する下部コンタクトプラグ7と、下部コンタクトプラグ7に縦積みされビット線BLに上端を接続する上部コンタクトプラグ5とから構成し、更に、上部コンタクトプラグ5を、ビット線BLに接続される第1のプラグ部5aと、この第1のプラグ部5aの上端の内径寸法より内径寸法が大きな大径部を有し、下部コンタクトプラグ7に接続された第2のプラグ部5bとから構成した。

(もっと読む)

寄生容量が減らされた半導体デバイス

【課題】高速ショットキーデバイス及びpn接合デバイスにおける寄生容量を低減すると共にボンディング強度を改善する。

【解決手段】基板303と、基板303の上に配置される半導体デバイス300、302、及び半導体デバイス300、302との電気的接触を行うボンディング用パッド307を有し、ベンゾシクロブテンの層304が半導体デバイスの周辺に設けられ、ボンディング用パッド307がベンゾシクロブテンの層304の頂面に設けられる。

(もっと読む)

半導体装置の製造方法

【課題】アルミニウム膜のウェットエッチングは、等方性のエッチング特性が知られているが、ウエハを高速回転させているため、回転に伴う異方性が現れるため、ウエハ外周部の配線形状を管理することが困難であった。

【解決手段】アルミニウム膜のウエット・エッチングにおいて、フルコーンノズルを2本搭載し、1本のノズルをウエハ全面へ薬液が塗布可能な位置に設置し、もう1本のノズルを薬液濃度が薄くなるウエハ中心部(ウエハ直近の位置)に設置し同時に薬液を塗布することにより、回転数依存が少なくエッチングレート均一性を向上することが可能とするものである。

(もっと読む)

半導体チップおよび半導体チップの製造方法

【課題】SiONx膜系のパッシベーション膜21とポリイミド膜22の2層構造からなる保護膜20を有する半導体チップにおいて、アセンブリ時にアセンブリ冶工具が保護膜20と干渉せず、耐湿信頼性の低下を起こさない半導体チップを得ること。

【解決手段】半導体基板上にトランジスタを含む電子部品が形成された半導体基材10の最上層の層間絶縁膜11に形成された電極パッド12と、層間絶縁膜11上の全面と電極パッド12の周縁部を覆い、電極パッド12の中心部が開口した第1の開口領域31を有するパッシベーション膜21と、パッシベーション膜21上の全面に形成されるポリイミド膜22と、を備え、ポリイミド膜22は、電極パッド12の形成位置に対応する位置に第2の開口領域32を有し、第2の開口領域32は、ポリイミド膜22の上面から所定の深さまでの領域では、第1の開口領域31よりも広い。

(もっと読む)

半導体装置の作製方法

【課題】材料や形成されたパターンが異なる複数の層が積層された構造の半導体装置において、CMP法による研磨処理やSOG膜成膜による平坦化処理を行わなくても平坦化でき、さらに基板材料を選ばず、簡便に平坦化を行う方法を提供することを課題とする

【解決手段】異なる層が複数積層されて形成された半導体装置において、絶縁膜に開口部を形成し、その開口部内に配線(電極)または半導体層を形成することにより、絶縁膜および配線(電極)または半導体層上に形成される絶縁膜に対してCMP法による研磨処理またはSOG膜の成膜による平坦化を行わなくても表面の平坦化を行うことができる。

(もっと読む)

アレイ基板

【課題】 Cuメッキ層におけるボイドの発生を抑制することにより、額縁領域が狭小化され、且つ配線の信頼性に優れたアレイ基板を提供する。

【解決手段】 表示部Hに薄膜トランジスタが形成されてなるアレイ基板である。薄膜トランジスタのソース領域13A及びドレイン領域13Bにコンタクトホール18を介してCuメッキ層17bが電極として接続されている。コンタクトホール18のアスペクト比は1以上である。コンタクトホール18において、底部近傍にのみCuシード層17aが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】リソグラフィ処理のマージンを向上し、ゲート電極の特性劣化の虞を極力なくすことを可能とする。

【解決手段】一対の選択ゲート電極SG−SG間のほぼ中央のスペースに多結晶シリコン層4cをポリプラグとして選択ゲート電極SGと同じ幅で設けている。このため、多結晶シリコン層4a〜4cを形成するときに周期的に構成することができる。周期性の崩れを緩和することができリソグラフィ処理のマージンを向上することができる。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの応力による構成要素の破損を防止する。

【解決手段】半導体装置10は、基板20と、複数の電極パッド24と、複数の第1開口部26aを有する表面保護膜26と、第2開口部30bを有する絶縁膜30と、電極パッド24から絶縁膜上に導出されている、柱状電極接続領域44aを有する配線44であって、柱状電極接続領域が第1開口部の真上に位置しており、かつ配線の柱状電極接続領域側の端縁が第1開口部の輪郭内に位置している配線を含む再配線層40と、柱状電極接続領域に底面50bの一部分である第1部分領域50baが接続されていて、電極パッドの真上に少なくとも底面の第1部分領域を位置させており、かつ第2部分領域50bbを絶縁膜とは非接触として設けられている柱状電極50とを具えている。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶配向が揃った良好な半導体装置とその製造方法を提供する。

【解決手段】本発明の半導体装置1は、第1の層間絶縁膜4の貫通孔43に形成された第1プラグ導電層44と、この第1プラグ導電層44上に設けられた導電部材61とを備えた半導体装置であって、第1の層間絶縁膜4上には、第1プラグ導電層44に通じる孔部54を有したスペーサ絶縁膜51が形成され、この孔部54内には、第1プラグ導電層44に接続し、かつ、導電部材61に接続するスペーサ導電部52が埋め込まれて形成されている。スペーサ導電部52は自己配向性を有する導電材料からなり、スペーサ絶縁膜51上とスペーサ導電部52上とは、平坦化処理されていることを特徴とする。スペーサ導電部52を所定の厚さにすることで、第1プラグ導電層43に確実に蓋することができ、結晶配向のずれが導電部材61に伝わることが防止される。

(もっと読む)

光電変換装置及び光電変換装置を用いた撮像システム

【課題】 配線層に銅を用いた場合にも、配線レイアウトの自由度を低下させることなく、光電変換素子への光の入射効率を向上させる。

【解決手段】 光電変換装置は、半導体基板に配された光電変換素子およびMOSトランジスタと、多層配線構造と、を有し、半導体基板上に配された第1の層間絶縁膜を有する。更に、半導体基板に配された複数の活性領域どうし、複数のMOSトランジスタのゲート電極どうしあるいは、活性領域とMOSトランジスタのゲート電極とを電気的に接続する、第1の層間絶縁膜に配された単一のホールに配された第1のプラグと、第1の層間絶縁膜に配されたホールに配され、活性領域と電気的に接続された第2のプラグと、を有する。そして、第2のプラグと第2のプラグよりも上部に配された配線層とが電気的に接続されており、その配線層はデュアルダマシン構造の一部である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対して有利であり、コンタクト電極の抵抗を低くすることが可能な半導体装置及びその製造法を提供する。

【解決手段】選択ゲートトランジスタSTの選択ゲート電極SG、及び周辺トランジスタTRの周辺ゲート電極TGを有し、ゲート電極SG、TG間の不純物拡散層28上及びゲート電極側面に第1絶縁膜30、第1バリア膜31を有し、第1バリア膜31上にゲート電極SG、TG間を埋める第2絶縁膜32を有する。ゲート電極SG、TG間の不純物拡散層28上の第1絶縁膜30及び第1バリア膜31に第1幅A1で第1方向に伸びるコンタクトホール下部35aが、第2絶縁膜32を貫通して底部がコンタクトホール下部35aと連接し、第1方向に第1幅A1よりも大きい第2幅A2を有するコンタクトホール上部35bが設けられ、コンタクトホール下部35a及びコンタクトホール上部35b内にコンタクト電極36が設けられている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタの上部電極とメモリセルトランジスタの1セル毎の接続を簡略化する。

【解決手段】強誘電体メモリ30では、左右のメモリセルトランジスタのソース/ドレイン領域2の一部を露出するようにビア(プラグ電極)V1が設けられている。ビア(プラグ電極)V1上には、キャパシタ下部電極CD1、強誘電体膜5、及びキャパシタ上部電極CU1から構成される強誘電キャパシタが積層形成されている。2つのゲート電極G1の間に形成されている絶縁膜4には、コンタクトホールCH1が中央部のソース/ドレイン領域2を露出するように設けられている。コンタクトホールCH1上には、キャパシタ上部電極CU1の一部を露出し、且つコンタクトホールCH1よりも大きなコンタクトホールCH2が設けられている。露出された中央部のソース/ドレイン領域2上のコンタクト部分には、配線層MH1が絶縁膜4と同じ高さに埋め込まれている。

(もっと読む)

61 - 80 / 118

[ Back to top ]