Fターム[5F033NN31]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | 断面が長方形以外 (728) | 上部を拡大、コンタクトパッド (511)

Fターム[5F033NN31]の下位に属するFターム

順テーパー部を有する (393)

Fターム[5F033NN31]に分類される特許

41 - 60 / 118

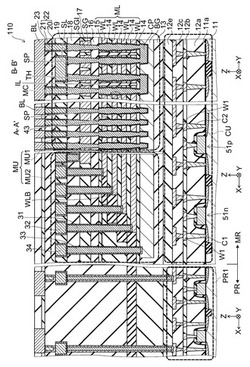

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

貫通電極の形成方法、及び半導体基板

【課題】高温雰囲気を維持した状態で溶融金属をハンドリングする必要をなくして工程及び装置を簡略化することができ、また導電ペーストを用いる場合と比較して高密度に金属を貫通孔内に充填することができる貫通電極の形成方法を提供する。

【解決手段】Si基板10の表面に開口を有する第1の非貫通孔21と、第1の非貫通孔21の底部に第1の非貫通孔21よりも小さな開口を有する第2の非貫通孔22とを形成し、第1の非貫通孔21の底部に固体金属50を載置する。Si基板10を減圧雰囲気下に置き、固体金属50の軟化点近傍まで加熱する。加熱状態を維持して減圧雰囲気から加圧雰囲気に移行し、軟化或いは溶融した金属50を第2の非貫通孔22に充填する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線間の容量の増加が抑制された半導体装置およびその製造方法を実現する。

【解決手段】本実施形態における半導体装置10は、半導体基板100と、半導体基板100上に形成された層間絶縁膜110(第一の層間絶縁膜)と、層間絶縁膜110上に形成された、層間絶縁膜110よりも誘電率が低い層間絶縁膜120(第二の層間絶縁膜)と、層間絶縁膜120を貫通し、底部が層間絶縁膜110に入り込んでいるCu配線141と、を備えている。Cu配線141は、下方に向かって幅が狭くなる形状を有しており、層間絶縁膜120におけるCu配線141の側面の傾斜よりも、層間絶縁膜110におけるCu配線141の側面の傾斜が大きくなっている。

(もっと読む)

半導体装置およびそれを用いた電子機器ならびに半導体装置の製造方法

【課題】本発明は、半導体基板の凹部内に形成される構成要素を有する半導体装置において歩留の低下およびデバイスの信頼性の低下を防止することが可能な半導体装置およびそれを用いた電子機器ならびに半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明の半導体装置は、絶縁膜8および貫通電極6が形成される貫通孔7が形成された半導体基板1を備え、半導体基板1の貫通孔7は、深さ方向に徐々に開口径が小さくなる形状を有し、貫通孔7の内壁には、貫通孔7の開口端よりも開口径が小さい段が形成されている。

(もっと読む)

半導体素子の製造方法

【課題】静電気防止素子のノーマルコンタクトと半導体素子のブランケットコンタクトを同時に形成する。

【解決手段】本発明の半導体素子の製造方法は、基板上に静電気防止素子に対するアクティブ領域と、第1ポリゲート及び半導体素子に対するアクティブ領域と、ブランケットトレンチ形態の第2ポリゲートとを形成する段階と、前記基板上に第1絶縁膜と第2絶縁膜を含む層間絶縁層を形成する段階と、前記層間絶縁層に平坦化工程を行う段階と、前記第1ポリゲート上に形成された層間絶縁層の一部を開口させたコンタクトパターンを形成する段階と、前記コンタクトパターンの下の第2絶縁膜を第1エッチングして第1ポリゲート上のトレンチを形成する段階と、第2エッチングを行って前記第1ポリゲート上のトレンチ内部の第1絶縁膜を除去し、前記第2ポリゲートを除いた前記半導体素子のアクティブ領域上の第1絶縁膜を除去する段階とを含む。

(もっと読む)

エッチング方法およびエッチング方法を用いた半導体装置の製造方法

【課題】本発明は、メタルマスクを用いて、簡易な方法により半導体基板に先細状ビア孔を形成するエッチング方法を提供することを目的とする。

【解決手段】半導体基板上に金属導電層を形成する工程と、該金属導電層上に第1の開口を有する第1メッキ層を形成する工程と、該第1メッキ層の側壁に該第1の開口より幅の狭い第2の開口を有する第2メッキ層を形成する工程と、該第2メッキ層をマスクとして第1のドライエッチングを行い該半導体基板をエッチングする工程と、該第1のドライエッチングの後に該第1メッキ層を残す選択的ウェットエッチングを行い該第2メッキ層をエッチングする工程と、該第2メッキ層をエッチングした後に該第1メッキ層をマスクとして第2のドライエッチングを行い該半導体基板をさらにエッチングする工程とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】従来の透過型液晶パネル向け半導体装置を小型化し、マイクロディスプレイを実現しようとするとき、半導体装置と透明電極とを接続するビアホールの径が縮小するため、接触抵抗が高くなるという問題があった。また、接触抵抗低減のために、半導体装置と透明電極との間に中間金属層を設けると、画素の開口率が低下し、画面が暗くなるという課題があった。

【解決手段】本発明の半導体装置は、半導体装置と透明電極との間に設ける中間金属層に切欠部を有する。この切欠部により、中間金属層の側面の面積を拡大し、透明電極との接触面積を従来よりも大きくすることができる。また、中間金属層の側面部面積を利用するため、画素表面に対する投影面積を小さく設定でき、画素の開口率を大きくすることができる。このため、十分な明るさをもつ、超小型のマイクロディスプレイを提供できる。

(もっと読む)

半導体装置

【課題】開口部の底部に電極パッドとして露出させた外部接続電極に接続ツールを用いて導電体を接続する場合に、電極パッドの面積を拡大することなく、接続ツールの先端が開口部の縁に接触することを回避可能な仕組みを提供する。

【解決手段】半導体素子層7と、半導体素子層7の一方の面側に、複数の配線層13,15,17と複数の層間絶縁膜12,14,16,18により形成された積層配線部11と、複数の配線層のうちの一つに形成された外部接続電極17aと、外部接続電極17aの表面を露出させる状態で半導体素子層7から積層配線部11にかけて凹状に形成された開口部22とを備える固体撮像装置の構成として、外部接続電極17aから遠い方の開口径d1が、外部接続電極17aに近い方の開口径d2より大きくなるように、開口部22を形成した。

(もっと読む)

表示装置及びその製造方法

【課題】CVD装置への出し入れ回数を減らした表示装置の製造方法および表示装置を提供すること。

【解決手段】本発明にかかる表示装置の製造方法は、絶縁基板上に第1の電極膜と第2の電極膜とを含む導電層、第1の絶縁層、半導体膜、第2の絶縁層および保護層を形成する工程と、半導体膜の上方の第1の領域に配置される所定の厚さの第1のレジスト膜と、第2の電極膜の上方の第2の領域に配置される開口部と、それら以外の領域に配置される厚い第2のレジスト膜と、を保護層上に形成する工程と、第2の領域下をエッチングする工程と、第1のレジスト膜をアッシングにより除去する工程と、第1の領域下に半導体膜に達する第1の孔を形成し、かつ第2の領域下に第2の電極膜に達する第2の孔を形成する工程と、第2のレジスト膜を除去する工程と、半導体膜および第2の電極膜と接続される配線を形成する工程と、を含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

空洞を有する導体配線上のソースコンタクト電極のコンタクトオープンを防止すると共に、ソース配線の抵抗を低くする。

【解決手段】本発明に係るNOR型フラッシュメモリのメモリセルアレイは、ソースコンタクト電極23及びダミーコンタクト電極24を形成する工程においてU字構造のソース配線21に形成された空洞22にソースコンタクト用のホールに加えてダミーソースコンタクト用のホールからも導電体が供給される。その結果、ソース配線21が延伸する方向に複数の素子領域及び素子分離絶縁膜上に亘って形成された下部導体配線53によってソース配線21の空洞22が埋まる。この下部導体配線53上にソースコンタクト電極23が形成されることによって、ソースコンタクト電極23がこの空洞22に落ちることなくコンタクトオープンを防止することが可能となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグの配列ピッチが狭くなっても、隣接するコンタクトプラグ同士の短絡を防止し、コンタクトプラグ及びそれに接続する配線パターンを容易に形成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極11、ソース領域及びドレイン領域12を有するトランジスタと、トランジスタを覆う層間絶縁膜14と、層間絶縁膜14を貫通して設けられ、ソース領域及びドレイン領域12の一方に接続されたコンタクトプラグ15と、コンタクトプラグ15を覆う層間絶縁膜26と、層間絶縁膜26にゲート電極11の延在方向と同一方向に延在し、底部にコンタクトプラグ15の上面を露出する溝27と、コンタクトプラグ15に接続され溝27内に設けられたコンタクトプラグ28cと、コンタクトプラグ28cと一体化して層間絶縁膜26上に溝27を横切るように延在する配線パターン28wとを備える。

(もっと読む)

集積回路構造、そのスタック構造及びこれらの製造方法

【課題】導電性電極の連結信頼性を高めることができる集積回路構造、スタック構造及びこれらの製造方法を提供する。

【解決手段】第1面106上の少なくとも一つの導電性パッド120と、少なくとも一つの導電性パッド及び集積回路基板105を貫通する貫通ホールとを持つ集積回路基板である。少なくとも一つの導電性電極150は、貫通ホール内に前記導電性パッドを貫通して前記導電性パッド上に延び、その内部に該第2面107から露出されたボイド160aを備える。

(もっと読む)

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通電極で接続するにあたって、貫通孔底部の角部におけるリーク電流の発生や絶縁膜のクラック等を抑制する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。貫通孔3は半導体基板2の第1の面2aに開口された第1の開口3aの開口径が第2の面2bに開口された第2の開口3bに近い側の内径より大きくなるように、第1の面2aの近傍を拡張させる拡張部4を備える。半導体基板2の第1の面2aには第1の絶縁層5と第1の配線層6とが設けられている。貫通孔3には拡張部4を充填しつつ内壁面を覆う第2の絶縁層7が設けられており、さらに第1および第2の絶縁層5、7の開口を介して第1の配線層6と接続された第2の配線層8が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板と、ホトダイオードの出力を半導体基板の一方の主面側から他方の主面側に導く導電性部材との間の電気絶縁性を確保することが可能な半導体装置及びその製造方法を提供すること。

【解決手段】n型半導体基板105には、隣接するp型不純物拡散領域109間に、一方の主面側から他方の主面側に貫通する貫通孔105cが形成されている。貫通孔105cは、p型不純物拡散領域109それぞれに対応して設けられている。貫通孔105cを画成するn型半導体基板105の壁面上には、熱酸化膜113が形成されている。貫通孔105c内には、熱酸化膜113の内側に導電性部材としての貫通配線115が設けられている。貫通配線115の一端側の部分は、電極配線117の一端側の部分に電気的に接続されている。電極配線117は、熱酸化膜107上に形成されており、その他端側の部分がp型不純物拡散領域109に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】後工程の熱によるクラックの発生を抑制し、製造歩留り及び製品品質を向上する。

【解決手段】GaAs基板10(基板)の表面上にソース電極12(表面電極)が形成されている。GaAs基板10の裏面からソース電極12に達するようにビアホール18が形成されている。GaAs基板10の裏面上及びビアホール18内にストレス緩和層20が形成されている。GaAs基板10の裏面上及びビアホール18内に、ストレス緩和層20を介して、Auメッキ22が形成されている。ストレス緩和層20は、線膨張係数が6×10−6〜14×10−6/Kの金属材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト歩留を向上させる、スタックドコンタクト構造を有する半導体装置を提供する。

【解決手段】NAND型フラッシュメモリのビット線コンタクトには、スタックドコンタクトを構成する第1のコンタクト開口部CH1、第2のコンタクト開口部CH2a、及び第3のコンタクト開口部CH2bが設けられる。下層の第1のコンタクト開口部CH1はビット線コンタクトの中央部に配置され、上層の第2のコンタクト開口部CH2aはビット線コンタクトの左部に配置され、その中心位置がビット線コンタクトの中心位置に対して第2のコンタクト開口部CH2aのズレ量だけ左方向に配置され、上層の第3のコンタクト開口部CH2bはビット線コンタクトの右部に配置され、その中心位置がビット線コンタクトの中心位置に対して第3のコンタクト開口部CH2bのズレ量だけ右方向に配置される。

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】互いに隣接するビットライン間に形成される寄生キャパシタの容量を減少させてフラッシュメモリ素子の動作速度を改善すると共にコンタクトプラグにボイドが発生する現象を改善する半導体メモリ素子及びその製造方法を提供する。

【解決手段】半導体メモリ素子は、ゲートパターン210間の半導体基板200上に形成されたコンタクトプラグ214a、214b,コンタクトプラグとそれぞれ連結され、一方の方向と他方の方向に延びた第1及び第2の導電性パッド220,320、第1及び第2の導電性パッドの延びた縁部の上部に互いに異なる高さでそれぞれ形成された第1及び第2のパッドコンタクトプラグ228,328、第1のパッドコンタクトプラグ228とそれぞれ連結される第1のビットラインBL1、及び第2のパッドコンタクトプラグ328とそれぞれ連結される第2のビットラインBL2を含む。

(もっと読む)

41 - 60 / 118

[ Back to top ]