Fターム[5F033NN33]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | コンタクトホールの平面形状 (560)

Fターム[5F033NN33]の下位に属するFターム

コンタクトホールの大きさ、数 (291)

Fターム[5F033NN33]に分類される特許

201 - 220 / 269

配線基板及びその製造方法

【課題】貫通配線と電気的に接触させるための導電部に、プローバテストによりプローバ針跡が発生しても、物理的な断線や接触不良の発生を抑制できる、配線基板を提供する。

【解決手段】本発明に係る配線基板10は、基材12の一方の面側に第一絶縁部13が配され、その厚さ方向に延びる貫通孔αを備えた基体11、前記貫通孔を塞ぐように前記基体の第一絶縁部側に配された導電部14、及び、前記導電部を少なくとも覆い、その一部には該導電部を露呈させる開口部15aを備えた第二絶縁部15、から構成されている。さらに、前記導電部のうち前記開口部により露呈された領域FD10が、前記貫通孔αと重なる位置に配され、かつ、前記導電部14が少なくとも多層構造をなしている。特に、この多層構造は、その重なり方向において、面状をなす第一層14sと第二層14uが島状をなす中間層14tを挟んでなる構造体を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】装置の信頼性を向上させる。

【解決手段】ゲート電極11gが形成された第1領域A1と、配線層21が形成された第2領域A2との間にて延在するように、層間絶縁膜20にコンタクト31を形成することによって、ゲート電極11gと配線層21とを接続させる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の実装時の熱応力による配線層や導電層の剥がれを抑制し、電気的な断線を防止した、高性能かつ信頼性の高い半導体装置及びその効率的な製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板(例えばシリコンウェハー10)と、該半導体基板10上に形成された配線層14と、該配線層上に形成された第一の導電層15と、該第一の導電層上に形成された層間絶縁膜16と、前記第一の導電層15と導通可能に、前記層間絶縁膜16上に形成された第二の導電層17とを有する。第二の導電層上にはバンプが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】埋め込み性がよくアスペクト比が高いコンタクトビアを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体層と、前記半導体層上に設けられ、前記半導体層に電気的に接続する第1コンタクトビアを有する第1絶縁層と、前記第1絶縁層上に設けられ、第2コンタクトビアを有する第2絶縁層とを備え、前記第1絶縁層から前記半導体層の方向に形成されたトレンチの底面近傍において、前記第1コンタクトビアと第2コンタクトビアとが電気的に接続されてなることを特徴とする半導体装置を提供する。

(もっと読む)

半導体担体用の低抵抗貫通基板相互接続

半導体基板(600)上に形成される電子チップ用の、低抵抗貫通ウェハ相互接続部(TWI)について示した。TWIは、基板(600)の前表面と後表面の間に延在する第1の接続部(610)を有する。第1の接続部(610)は、貫通孔を有し、この貫通孔には、ポリシリコンよりも小さな比抵抗を有する低抵抗材料が充填される。さらに、TWIは、第2の接続部(615)を有し、これも、前表面と後表面の間に延在している。第2の接続部(615)は、半導体基板(600)の少なくとも一部によって、第1の接続部(610)と空間的に分離される。前表面には、集積回路配置(620)が提供され、前記第1の接続部(610)は、前記集積回路配置(620)に進入せずに、前記集積回路配置(620)の少なくとも一つのノードと電気的に結合される。TWIの処理に応じて、貫通孔には、非金属材料の充填材料、例えばポロシリコンが充填される。前表面の上部に集積部材(620)を形成した後、基板(600)は、薄膜化処理され、非金属材料は、特に金属材料のような低抵抗材料と置換される。

(もっと読む)

(もっと読む)

回路基板及び表示装置

【課題】レイアウトの効率化が図れ、デバイス面積を縮小することができる回路基板及び液晶表示装置を提供する。

【解決手段】第1半導体層、絶縁膜及び第1ソース電極がこの順に積層された第1薄膜トランジスタと、第1ソース電極に接続された第2ゲート電極を有する第2薄膜トランジスタとを基板上に有する回路基板であって、上記回路基板は、第1半導体層と第1ソース電極とを接続する第1導電部と、第1ソース電極と第2ゲート電極とを接続する第2導電部とが、絶縁膜の共通の開口部に設けられた回路基板である。

(もっと読む)

半導体装置の製造方法

【課題】従来の構成では、接続プラグ上の絶縁層に設けられた開口部内に導電膜を堆積させる際、接続プラグの表面と開口部の内表面とに導電膜が連続して形成されない可能性があり、接続プラグと導電膜との電気的接続信頼性が低減してしまう可能性があった。

【解決手段】本願発明では、接続プラグが配置される接続プラグ領域は第1の長さ方向と第1の幅方向とから成る長尺形状を備え、接続プラグ上の絶縁層に設けられた開口部により露出する開口領域は第2の長さ方向と第2の幅方向とから成る長尺形状を備え、開口部を設ける際のエッチング工程において、接続プラグ領域の第1の長さ方向と開口領域の第2の長さ方向とが所定の角度を成すように交差して配置される。これにより、接続プラグと開口部内に堆積される導電膜との電気的接続信頼性を向上させることが可能となる。

(もっと読む)

相変化メモリ装置およびその製造方法

【課題】相変化メモリ装置のメモリセル部における、相変化領域の上側ならびに下側の金属からの放熱を共に抑制し、熱効率の低下を最小限化して、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】相変化層の下側のコンタクトプラグからの放熱は、異種材料コンタクトプラグ104を採用して抑制する。すなわち、第2の導電材料に比べて比抵抗が大きい(逆に、熱伝導率は小さい)第1の導電材料からなる第1の導電材料プラグ106にヒータ電極110を接続することによって、放熱を抑制する。相変化層の上側の電極からの放熱は、引き出し電極116を用いた、相変化領域(ヒータ電極110の上面112の近傍)の直上に電極を設けない電極構造の採用によって抑制する。

(もっと読む)

半導体装置

【目的】パッド電極へのボンディングに対するパッド電極部の強度を向上し、素子形成領域へ水分などが進入するのを防止して高い信頼性を確保できる半導体装置を提供すること。

【解決手段】コンタクトホール6,10,14をパッド電極18を取り囲むように帯状でリング状に形成し、このコンタクトホール6を充填する接続導体7、11およびメタル配線層8,12および第3コンタクトホール14を充填した第3メタル配線層15の一部をパッド電極18を取り囲むように帯状でリング状に形成することで、パッド電極18直下の層間絶縁膜5,9,13をメタル配線層8,12,15と接続導体7、11で取り囲みこの層間絶縁膜5,9,13にクラックが発生した場合でも、このクラックを介して進入する水分をパッド電極18外に形成される素子領域へ進入することを防止して高い信頼性を確保できる半導体装置とすることができる。

(もっと読む)

半導体素子及びその製造方法

【課題】電気的な短絡を防止するコンタクトを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板100上に形成された下部導電層124、下部導電層124を覆う層間絶縁膜150、層間絶縁膜150内に形成されるコンタクトホール160〜164、及びコンタクトホール160〜164を埋めるコンタクトプラグ170〜174を備える。コンタクトホール160〜164は、下部導電層124の上面を露出させるとともに、上断面が楕円形である。そして、コンタクトホール160〜164は、上断面の短軸方向に比べて長軸方向を近接して配列される。これにより、ボーイングによるコンタクトホール160〜164間の電気的な短絡を防止でき、素子の誤動作を減少させて性能を向上させて信頼性を高めることができる。

(もっと読む)

半導体装置

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題とする。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を備えた半導体装置を積層した3次元半導体装置において、貫通電極の抵抗と容量が大きく、高速データ転送ができないという問題がある。

【解決手段】貫通電極をゲート電極の第1導電膜をマスクとして形成する。第1導電膜の上に成膜されたゲート電極の第2導電膜を、貫通電極の配線電極とする。ゲート電極形成工程において貫通電極を形成することで高融点金属およびその化合物が使用でき、低抵抗化が図れる。さらに貫通電極からの配線工程をゲート電極からの配線工程と共有化する等、半導体標準プロセスに適合させることで工程を短縮することができる。

(もっと読む)

相変化メモリ装置および相変化メモリ装置の製造方法

【課題】相変化メモリ装置における良好な電気特性と良好な熱特性を両立させ、電極や配線の材料選択の自由度も高めて、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】ヒータ電極110と相変化層114の接触界面112の近傍で発生するジュール熱が、ヒータ電極110を介して下方に伝達され、下地の良導電性の金属コンタクトプラグから放熱されることを抑制するために、異種材料コンタクトプラグ104(108,106)を採用する。ヒータ電極110に接触する第1の導電材料プラグ108は、ヒータ電極110の構成材料と同種または同じ金属材料からなり、第2の導電材料プラグ106は、接地配線102と同種あるいは同じ金属材料からなる。第1および第2の導電材料プラグ108,106は、少なくとも側面同士が接触する。

(もっと読む)

半導体装置およびその製造方法

【課題】FUSIゲート電極に達するコンタクト部と、ソース・ドレイン層に達するコンタクト部とで深さが異なることに起因する不具合を解消した半導体装置およびその製造方法を提供する。

【解決手段】層間絶縁膜4を厚さ方向に貫通して2つのソース・ドレイン層34上層部のシリサイド層35およびFUSIゲート電極32にそれぞれ達する2つのFUSIコンタクト部41が設けられている。FUSIコンタクト部41は、層間絶縁膜4を貫通するコンタクト開口部CH1内に、完全にシリサイド化されたFUSIコンタクト層411を充填して構成されており、FUSIゲート電極32と同じ高さを有している。

(もっと読む)

一時的なキャップ層を用いる、覆われた、基板を貫通するビアの製造

本発明は、第1の基板の面を反対側の第2の基板の面と電気的に、好ましくは熱的にも接続する少なくとも1つの覆われたビアを有する基板を製造する方法に関する。加工は、第1の基板の面上にトレンチを形成することと、熱処理工程において分解される一時的な犠牲キャップ層上の永久的な層でトレンチを覆うこととを含む。本発明の方法は、永久的な層の存在下であっても痕跡又は汚染を残すことなく犠牲キャップ層の分解生成物を除去する代わりの方法を提供する。このことは、本発明の第1の態様に従って、基板のトレンチにホールを有するオーバーコート層を施すことによって達成される。オーバーコート層におけるホールはキャップ層材料の分解生成物の除去のための空間を残す。本発明の第2の態様において、第2の基板の面から覆われたトレンチを開け、開口部を通じてキャップ層材料を除去することによって解決がもたらされる。本発明の両方の方法は、基板の開口部が一時的なキャップ層の除去の前に永久に覆われている状況においても一時的なキャップ層を使用するという共通の発想に基づくものである。  (もっと読む)

(もっと読む)

密集コンタクトホールを有する半導体デバイス

【課題】特別なエッチング工程を必要とせずに、短軸側のボーイングした個所で隣接するホールとショートするおそれのない楕円断面の密集コンタクトを有する半導体デバイスを提供する。

【解決手段】なるべく長軸21側の側面に近い方に最小分離幅26が配置され、短軸22側の側面が最小分離幅とならず、短軸22側の側面と短軸22側の側面が重ならないように、2種類の傾斜角度のホール20が4つのホール20が1セットとなった繰り返しパターンで構成されており、ボーイングの大きい短軸22側の分離間隔が大きく取られている。

(もっと読む)

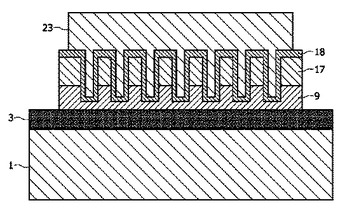

改良された接触パッドを有する半導体デバイスとその製造方法

半導体デバイスおよびその製造方法が開示される。このデバイスは、1以上の導電性ゲート(11)を具えた活性半導体領域(1A)と、前記活性半導体領域(1A)の周辺に位置し主としてフィールド酸化領域(3)よりなるコンタクト領域(1B)とを具える。周辺コンタクト領域(1B)上、および、少なくとも一部の活性半導体領域(1A)上に、導電性ゲート(11)の間にコンタクト窓(19a)が形成された絶縁層(17)が積層される。絶縁層(17)上に積層された金属コンタクトパッド(23)が、前記コンタクト領域(1B)に設けられる。この金属コンタクトパッド(23)は、導電性のパターンを介して、絶縁層(17)の下に埋設されているコンタクトストリップ(15)に接触し、この導電性のパターンは、コンタクト窓(19b)充填物の複数個で構成されており、コンタクトパッド(23)の実質的な領域を横切って延びている。このパターンは平行な一連のトレンチに充填されたもので構成されているのが好ましい。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 ビアホール5の上方に形成される異常構造部による金属配線間のショート不良の発生を抑制できる半導体装置の製造方法を提供する。

【解決手段】 ビアホール5を形成する工程において、1つのビアホール5の開口幅を、0.4μmとし、ビアホール5の数を、第1金属配線の体積/ビアホール個数<5という関係式を満たすように設定して、複数のビアホール5を第2層間絶縁膜4に形成する。これにより、ビアホール5を形成した後のビアプラグ6を形成する工程で、半導体基板1が加熱された場合に、第1金属配線3の1つのビアホール5底部に位置する部位にかかる応力を緩和することができ、ビアホール5内での第1金属配線3の柱状部12の発生を抑制できる。この結果、異常構造部の形成を抑制でき、第2金属配線7と第3金属配線9との間のショート不良の発生を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】裏面のグランド層を容易に形成するとともに、ビアホールを位置合わせが容易に形成する。

【解決手段】ウェハ1の半導体集積回路が形成されている側の表面11に形成された第1のホール2と、ウェハ1の裏面12に形成された第2のホール3とを有し、1個の第2のホール3と複数個の第1のホール2とがつながってウェハ1を貫通するビアホール4が構成され、ビアホール4には埋め込み金属層5が埋め込まれ、ウェハ1の裏面12の全体にはグランド層6が形成されている。

(もっと読む)

半導体装置

【課題】空孔率の高い層間絶縁膜を用いた信頼性の高い多層配線構造を有する半導体装置を提供する。

【解決手段】空孔率が50%以上の層間膜を有する下層配線層と、空孔率の低い上層配線層を備える多層配線構造において、配線層間を接続するビアを配線層を介して基板表面に垂直方向に連続して形成したスタックドビア70とチップ外周部に設けた外周リング80により、空孔率が低く厚い層間膜を有する上層配線層を支える構造とする。

(もっと読む)

201 - 220 / 269

[ Back to top ]