Fターム[5F033NN40]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | 配線層が3層以上に跨がるコンタクトホール (478) | 中間層を電気的に絶縁 (227)

Fターム[5F033NN40]に分類される特許

221 - 227 / 227

半導体装置およびその製造方法

【課題】 コンタクトホール側壁に形成するスペーサ用絶縁膜がシリコン基板と接触しない構成とし、且つRIE加工工数を低減する。

【解決手段】 NANDフラッシュメモリで、メモリセル領域2のゲート電極5、5間のコンタクトホール8と周辺回路領域3の高耐圧トランジスタ6のコンタクトホール9とに、層間絶縁膜20の側壁にスペーサとしてのシリコン窒化膜21を形成する構成である。シリコン窒化膜21の下端部は、シリコン基板1との間に、シリコン酸化膜17もしくは18を介在させている。シリコン基板1へのストレスを緩和してゲート酸化膜の電子トラップを低減する。また、シリコン窒化膜のRIE加工回数を減らすことができる。

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

基板をエッチングするための方法及び装置

本方法及び装置は、化学式CaFbを有する第1のガス及び化学式CxHyFzを有する第2のガスの混合物(ただし、a/b≧2/3、x/z≧1/2である)に基づくプラズマの使用を通して半導体及び誘電体基板をエッチングするために提供される。この混合物は、磁気的に増強された反応性イオンチャンバ内に維持された低または中密度プラズマにおいて用いられ、優れたコーナー層の選択性、ホトレジストの選択性、下層の選択性及びプロファイルと底部のCD制御を示すプロセスを提供する。第1と第2のガスのパーセンテージは、ドープされない酸化物膜をエッチングするプラズマまたはこのような膜上でエッチング停止を与えるために、エッチング中に変えることができる。  (もっと読む)

(もっと読む)

半導体素子の製造方法

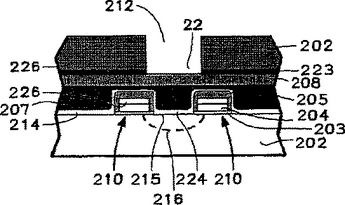

【課題】 シリコンを含むN型の導電領域と直接接続される導電パターンの形成時に、N型の導電領域と接続される部分のコンタクト抵抗の増大を防止し、バリア膜の厚さ増大に伴う導電パターンの寄生容量の増大を防止できる半導体素子の製造方法を提供すること。

【解決手段】 シリコンを含むN型の導電領域(207)にN型の不純物をドープして、N型の高濃度不純物拡散領域(212)を形成する工程と、CVD法を用いて高濃度不純物拡散領域(212)上にバリア用第1金属膜を蒸着し、高濃度不純物拡散領域(212)のシリコンと前記第1金属膜の金属とを反応させて、高濃度不純物拡散領域(212)と前記第1金属膜との間の界面に金属シリサイドを形成する工程、前記第1金属膜上に導電膜を形成する工程、及び、前記導電膜と前記第1金属膜とを選択的にエッチングして、導電パターンを形成する工程を含む。

(もっと読む)

貫通孔形成方法、半導体装置及びその製造方法

【課題】 {100}シリコン基板からなる半導体基板の表裏面を電気的に接続する、半導体基板に対して垂直な貫通孔を、非常に容易な方法で形成する。

【解決手段】 表面に保護膜が形成された{100}シリコン基板に、保護膜を取り除くことにより所定の領域以上の大きさの半導体表面開口部を形成し、開口部にレーザ加工により、所定の領域よりも小さい内径の貫通孔を形成した後、貫通孔を異方性エッチングによって内径を拡大し、内径が該所定の大きさになった時に該エッチングを終了する。これにより基板表面より貫通孔内面に向かって逆テーパ形状の{111}結晶面を析出する事なく所定の大きさの貫通孔を形成することができるとともに、レーザ加工によって加工孔周囲および内部に発生するドロスやデブリス等を消滅させ、かつ貫通孔内面が非常に滑らかな結晶面で形成された、高品位の貫通孔を実現する事が可能である。

(もっと読む)

半導体装置

本発明は、ボンディングパッドで発生する応力に対する強度を向上させることが可能な半導体装置を提供することを目的とする。本発明に係る半導体装置においては、半導体チップ上にボンディングパッド(1)が複数個設けられる。それぞれのボンディングパッド(1)においては、最上層の配線層を用いて形成された第1メタル(11)の下に、ライン状の第2メタル(12)が複数個設けられる。そして、上記目的を達成するために、ボンディングパッド(1)は、第2メタル(12)の長手方向に並べて配設される。つまり、第2メタル(12)の長手方向(L1)と、ボンディングパッド(1)の配列方向(L2)とが同じ方向になるように、ボンディングパッド(1)を並べて配設する。 (もっと読む)

電子デバイス、アセンブリ、電子デバイスの製造方法

半導体基板は、共通の誘電層を有する垂直相互接続部および垂直キャパシタの両方を備えている。基板は、アセンブリを形成するために更なるデバイスと適切に組み合わせることができる。基板は、一方の面を第1のステップを含むエッチング処理で形成した後、基板の他方の面を第2のステップを含む処理で形成することができる。  (もっと読む)

(もっと読む)

221 - 227 / 227

[ Back to top ]