Fターム[5F033NN40]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | 配線層が3層以上に跨がるコンタクトホール (478) | 中間層を電気的に絶縁 (227)

Fターム[5F033NN40]に分類される特許

201 - 220 / 227

半導体装置及びその製造方法

【課題】 キャパシタ形成後のコンタクトプラグ形成時又は配線層形成時等に容量絶縁膜に加わるプラズマダメージを低減することにより、容量絶縁膜の劣化を抑制してキャパシタリーク電流の増大を防止する。

【解決手段】 半導体基板100上の第1の層間絶縁膜106の上に形成され第2の層間絶縁膜109に、キャパシタ領域となる凹部110が形成されている。凹部110内に下部電極(第2のポリシリコン膜412及びHSG膜413)が形成されていると共に該下部電極上に容量絶縁膜となる酸化タンタル膜115及び上部電極となる第1の窒化チタン膜が形成されている。当該上部電極及び上層配線124のそれぞれと接続するプレートコンタクト120が、第1の層間絶縁膜106中に形成されたプラグ107Cを介して、半導体基板100の表面部のN型不純物拡散層105と電気的に接続されている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高速動作が可能なLDD型MISFETと、かつ高電圧駆動が可能なLDD型MISFETとを内蔵する半導体集積回路装置を低コストで実現する。

【解決手段】高速動作が可能なMISFETは、ゲートサイドウオール層に自己整合された高濃度領域に金属シリサイド層を有し、高電圧駆動が可能なMISFETは、上記ゲートサイドウオール層の幅よりも大きい幅を有するLDD部を有し、そのLDD部に接して高濃度領域を有し、そしてその高濃度領域に金属シリサイド層を有する。

(もっと読む)

半導体素子及びその形成方法

【課題】MIMキャパシタを形成した後に金属配線を形成することにより無駄なマスク工程を省略し、キャパシタ形成時のエッチングでの金属配線の損傷を防止できる半導体素子及びその形成方法を提供すること。

【解決手段】層間絶縁膜100を貫通するコンタクトプラグ110を形成するステップと、層間絶縁膜100上にキャパシタを形成するための下部電極用導電層130、誘電層140、上部電極用導電層150を順次形成するステップと、上部電極用導電層150をパターニングして上部電極150を形成するステップと、誘電層140及び下部電極層130をパターニングして下部電極130を形成してキャパシタを形成するステップと、コンタクトプラグ110、キャパシタの上部電極150及び下部電極130に接続される第1金属配線120を形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

強誘電体キャパシタ(23)を形成した後、表面の傾斜が緩やかな絶縁膜(24)を、高密度プラズマCVD法又は常圧CVD法等により形成する。その後、アルミナ膜(25)を絶縁膜(24)上に形成する。このような方法によれば、アルミナ膜(25)のカバレッジの低さが問題となることはなく、強誘電体キャパシタ(23)が確実に保護される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

キャパシタ誘電体膜の原料膜としてPLZT膜(30)を形成した後、PLZT膜(30)上に上部電極膜31を形成する。上部電極膜(31)は互いに組成の異なる2層のIrOx膜から構成する。続いて、半導体基板(11)の背面の洗浄を行う。そして、上部電極膜(31)上にIr密着膜(32)を形成する。このとき基板温度を400℃以上とする。次に、ハードマスクとしてTiN膜及びTEOS膜を順次形成する。このような方法では、Ir密着膜(32)を形成するに当たって半導体基板(11)の温度を400℃以上に保持している間に、背面の洗浄後に上部電極膜(31)上に残留していた炭素がチャンバ内に放出される。このため、その後に形成されるTiN膜とIr密着膜(32)との間の密着性が高くなり、TiN膜の剥がれが生じにくくなる。  (もっと読む)

(もっと読む)

薄膜デバイス、薄膜デバイスの製造方法、集積回路、マトリクス装置、電子機器

【課題】複数の薄膜素子層の相互間の良好な接合状態を確保し、かつ各層の相互間の電気的接続を容易にすること。

【解決手段】薄膜デバイスは、第1の薄膜素子層(13)と、第1の電極端子(16)と、第1の非導通端子(17)と、第2の薄膜素子層(23)と、第2の電極端子(26)と、第2の非導通端子(27)と、を含む。第2の電極端子と第2の非導通端子は、それぞれ、第2の薄膜素子層を貫通する貫通部と、第2の薄膜素子層の上面、下面にそれぞれ露出する上側露出部及び下側露出部と、を備える。第1の電極端子及び第1の非導通端子のそれぞれと、第2の電極端子及び第2の非導通端子のそれぞれの下側露出部とを接合することにより、第1及び第2の薄膜素子層の相互間の電気的接合及び物理的接合が図られる。

(もっと読む)

半導体装置およびその製造方法

【課題】光近接効果に起因するトランジスタのゲート長ばらつきを抑制しうる半導体装置を提供する。

【解決手段】ゲート電極5A〜5Fを同一形状であり、ゲート電極5A〜5Fの突き出し部は、素子分離領域を越えて基板コンタクト用の拡散領域上まで延びている。ゲート電極5BおよびP型拡散領域と1層目配線M1Hとはシェアードコンタクト9A1で接続され、ゲート電極5EおよびN型拡散領域7A6と1層目配線M1Iとはシェアードコンタクト9A2で接続される。これにより、ゲート電極5A〜5Fのうちコンタクトパッド部をMOSトランジスタの活性領域から離すことができる。その結果、ハンマヘッドによるゲート長太り及びゲートフレアリングによるゲート長太りの効果が抑制され、TrA〜TrFの仕上がりゲート長をほぼ一定値にすることが可能となる。

(もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

非対称パターンを形成するためのフォト工程の実行方法及びそれを用いた半導体装置の形成方法

【課題】非対称パターンを形成するためのフォト工程の実行方法及びそれを用いた半導体装置の形成方法を提供する。

【解決手段】準備した半導体基板の素子分離膜は複数の活性領域を孤立形成する。半導体基板全面上に平坦化層間絶縁膜及びフォトレジスト膜を順に形成する。フォトレジスト膜にフォトマスクによる半導体パターンを転写させその膜にフォトレジストパターンを形成する。それは、活性領域及び素子分離膜の上部位置の平坦化層間絶縁膜上の所定領域に配置される。フォトレジスト膜に他のフォトマスクを有する他の半導体パターンを引き続いて転写させてその膜に他のフォトレジストパターンを形成する。それは素子分離膜上部に位置した平坦化層間絶縁膜上の異なる所定の領域にそれぞれ配置される。フォトレジストパターン及び他のフォトレジストパターンをエッチングマスクとして用いて平坦化層間絶縁膜にエッチング工程を実行して半導体基板を露出する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

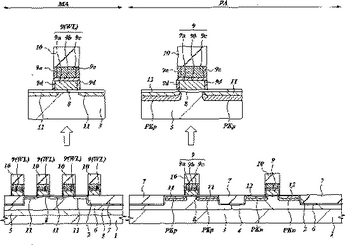

半導体メモリ素子の金属配線形成方法

【課題】ドレインコンタクトプラグに電気的に接続される金属配線とソースコンタクトプラグ間のブリッジによる短絡が発生することを防止する。

【解決手段】第1層間絶縁膜をパターニングし、ドレインコンタクトプラグを形成する段階と、第1エッチング工程によって前記第1層間絶縁膜をリセスさせて前記ドレインコンタクトプラグを突出させる段階と、前記ドレインコンタクトプラグを含む全体構造上の段差に沿って窒化膜を蒸着する段階と、前記窒化物上に第2層間絶縁膜を形成する段階と、前記ドレインコンタクトプラグの突出部位に形成された前記窒化膜が露出するように前記第2層間絶縁膜をパターニングしてトレンチを形成する段階と、第2エッチング工程によって、前記トレンチを介して露出する前記窒化膜を除去して前記ドレインコンタクトプラグを露出させる段階と、前記トレンチが埋め立てられるように金属配線を形成する段階とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有した半導体装置において、保護膜や絶縁膜の剥離を防止し、半導体装置の信頼性を向上する。

【解決手段】半導体装置100のコーナー部に、絶縁膜17、保護層23の剥離を防止するための剥離防止層30を形成する。剥離防止層30はコーナー部以外の半導体装置10の空きスペース、例えば、ボール状の導電端子24の間に配置することでさらに剥離防止効果を高めることができる。その断面構造は、半導体基板10の裏面に形成された絶縁膜17上に剥離防止層30が形成され、この絶縁膜17及び剥離防止層30を被覆するようにソルダーレジスト等から成る保護層23が形成される。剥離防止層30は、電解メッキ法により形成する場合には、バリアシード層20と上層の銅層25からなる積層構造を有する。

(もっと読む)

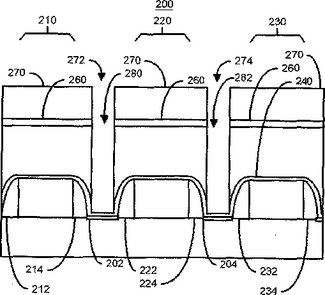

半導体セルの接触不良(contactdefect)を減らす方法とシステム

本発明は、半導体デバイス中に少なくとも1つのコンタクトを提供する方法およびシステムを提供する。半導体デバイスは、基板(201)、エッチング停止層(240)、このエッチング停止層(240)上にある層間絶縁膜(250)、層間絶縁膜(250)上にある反射防止(ARC)層(260)、およびエッチング停止層(240)より下にある少なくとも1つの構造を含んでいる。少なくとも1つのアパーチャを有しているとともに、このARC層(260)上にあるレジストマスクを提供する。このアパーチャは、ARC層(260)の露出した部分上方にある。この方法およびシステムは、エッチング停止層(240)を貫通してエッチングすることなく、露出したARC層(260)およびその下にある層間絶縁膜(250)をエッチングすることを含む。これにより、少なくとも1つのコンタクトホールの一部を提供する。この方法とシステムはまた、原位置でレジストマスクを除去し、少なくとも1つのコンタクトホールを原位置に提供すべく、コンタクトホールの一部において露出したエッチング停止層(240)の一部を除去し、コンタクトホールを導電材料で充てんすることを含む。  (もっと読む)

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

半導体基板内の分離溝に隣接するコンタクト用開口の形成方法

【課題】フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法を提供する。

【解決手段】トレンチ形成・埋め込み法によって半導体基板の中にフィールド分離マスを形成し、該フィールド分離マスに隣接した基板上に基板マスキング層を形成する工程であって、前記フィールド分離マスの上面はエッチングストップキャップによって覆われ、その側壁は前記マスキング層によって覆われる工程と、前記分離マス側壁の少なくとも一部を露出するために、分離マスから分けて前記基板マスキング層を除去する工程と、露出した分離マス側壁上にエッチングストップカバーを形成する工程と、前記分離マス及び該分離マスに隣接する基板領域上に絶縁層を形成する工程と、前記分離マスエッチングストップキャップ及びカバーに対して選択的に、前記分離マスに隣接する前記絶縁層を貫通するコンタクト用開口をエッチング開口する工程とからなる、フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】一列配置されるビット線コンタクトCBの形成予定領域におけるボイドの発生を回避する。

【解決手段】半導体チップ100上に搭載され、ビット線BLと、ビット線に直交するソース線SL及びワード線WLを備える半導体記憶装置において、ビット線方向に配列されたワード線の両端部に隣接して、ワード線に平行に配列されるビット線側選択ゲート線SGD及びソース線側選択ゲート線SGSと、ビット線とワード線の交差部に配置されるメモリセルトランジスタMT及びビット線と選択ゲート線の交差部に配置される選択ゲートトランジスタSTと、ビット線側選択ゲート線間においてワード線方向に配置されるビット線コンタクトCBと、ソース線側選択ゲート線間においてワード線方向に配置されるソース線コンタクトCSとを備え、ビット線側選択ゲート線間の間隔L1が、ソース線側選択ゲート線間の間隔L2よりも大きい半導体記憶装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線の狭ピッチ化に対応可能な半導体装置およびその製造方法を得る。

【解決手段】半導体基板上に複数の第1配線層を形成する工程と、第1配線層を覆うように第1層間絶縁膜層9を形成する工程と、第1層間絶縁膜層に、表面からその厚み方向に貫いて第1配線層に接続する複数の第1プラグ14を形成する工程と、第1層間絶縁層上であって、第1プラグのうち一部の第1プラグの直上部に第2配線層40を形成する工程と、第1層間絶縁膜層上に第2配線層を覆うように第2層間絶縁膜層19を形成する工程と、第2層間絶縁膜層に、表面からその厚み方向に貫いて第2配線層に接続する第2プラグ24’と、表面からその厚み方向に貫いて第1プラグに直接接続する第3プラグ24と、を同時に形成する工程と、第2層間絶縁膜層上であって、第2プラグおよび第3プラグの直上部に第3配線層50を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】 信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置は、複数のパッド12を有する半導体基板10と、半導体基板10を貫通する貫通穴20と、いずれかのパッド12と電気的に接続されて貫通穴20の内側を通り半導体基板10を貫通するように形成された第1の導電体30と、半導体基板10及び第1の導電体30と電気的に絶縁されて、貫通穴20の内側で第1の導電体30の側面を囲むように形成された第2の導電体40とを有する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 半導体集積回路チップに基板貫通孔を短時間に効率よく形成する。

【解決手段】 チップ表面に拡散層15を形成して配線14と接続させ、貫通孔底部の中心が拡散層15と配線14との接続部分の中心にくるようにし、且つ貫通孔底部径が配線14と拡散層15との接合部分の径と同一かそれよりもやや大きな径になるように径を制御しながら、半導体集積回路チップ裏面13よりドライエッチングを開始して、貫通孔16を形成する。本発明の半導体チップ構造では、ドライエッチングの際に使用するエッチングガスはシリコンを選択的にエッチングするガスだけでよい。従ってエッチング工程の途中でエッチングガスを他の種類のエッチングガスに交換する必要がなく、基板貫通孔を短時間に効率よく形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクトホール側壁に形成するスペーサ用絶縁膜がシリコン基板と接触しない構成とし、且つRIE加工工数を低減する。

【解決手段】 NANDフラッシュメモリで、メモリセル領域2のゲート電極5、5間のコンタクトホール8と周辺回路領域3の高耐圧トランジスタ6のコンタクトホール9とに、層間絶縁膜20の側壁にスペーサとしてのシリコン窒化膜21を形成する構成である。シリコン窒化膜21の下端部は、シリコン基板1との間に、シリコン酸化膜17もしくは18を介在させている。シリコン基板1へのストレスを緩和してゲート酸化膜の電子トラップを低減する。また、シリコン窒化膜のRIE加工回数を減らすことができる。

(もっと読む)

201 - 220 / 227

[ Back to top ]