Fターム[5F033NN40]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | 配線層が3層以上に跨がるコンタクトホール (478) | 中間層を電気的に絶縁 (227)

Fターム[5F033NN40]に分類される特許

61 - 80 / 227

半導体装置及びその製造方法

【課題】ゲート電極同士の間隔が狭い場合においても、基板に損傷を与えることなく微細なコンタクトホールを安定して形成することが可能な半導体装置及びその製造方法を実現できるようにする。

【解決手段】半導体装置は、基板11の上に互いに間隔をおいて形成されたゲート電極13と、基板11の上に、ゲート電極13同士の間の領域を埋め且つゲート電極13を覆うように形成された第1の絶縁膜16と、第1の絶縁膜16の上に下側から順次形成された第2の絶縁膜17及び第3の絶縁膜18と、第1の絶縁膜16、第2の絶縁膜17及び第3の絶縁膜18を貫通し、ソース・ドレイン領域15と電気的に接続されたコンタクトプラグ22とを備えている。第1の絶縁膜16は、水素原子を含み且つフッ素原子を含まないガスによりドライエッチング可能な材料からなる。

(もっと読む)

不揮発性半導体メモリ

【課題】信頼性の高い不揮発性半導体メモリを提供できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、複数のメモリセルが配置されるメモリセルアレイ領域100と、メモリセルアレイ領域100の周囲を取り囲む周辺回路領域と、周辺回路領域とメモリセルアレイ領域100との境界部分であるセルアレイ隣接領域105と、メモリセルアレイ領域100内に層間絶縁膜を介して設けられる複数の第1導電線SLと、セルアレイ隣接領域105内に層間絶縁膜を介して設けられる複数の第2導電線M2とを具備し、複数の第2導電線M2はその配線内にスリット50が形成されていることを備える。

(もっと読む)

半導体装置とその製造方法

【課題】高温かつ長時間の熱工程を経ても、酸化されないコンタクトプラグを備えた半導体装置とその製造方法を提供する。

【解決手段】半導体基板上にトランジスタを形成し、前記トランジスタ及び前記半導体基板を覆う層間絶縁膜を形成し、前記層間絶縁膜にこれを貫通する、1つ以上のコンタクトホールを開口し、前記コンタクトホールの側面に、酸化性ガスが拡散するのを防ぐ、絶縁性の酸化性ガス拡散防止膜を成膜し、前記酸化性ガス拡散防止膜の内側に、前記トランジスタの端子とコンタクトするコンタクトプラグ本体を埋め込んで、前記層間絶縁膜から発生する酸化性ガスが前記酸化性ガス拡散防止膜によって前記コンタクトプラグ本体に拡散するのを防止可能な構成を作り、この後、前記層間絶縁膜の上方に、前記コンタクトプラグ本体の1つと電気的に導通する、強誘電体膜を含む強誘電体キャパシタを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクト孔形状の改善することで配線材料のカバレージの向上を計り、配線材料の第1導電型半導体基板への拡散によるリーク電流の防止を図る。

【解決手段】 第1導電型半導体基板に形成されている第2導電型高濃度拡散層と配線材料を接合させるコンタクト孔を具備し、コンタクト孔形成後にバリアメタル膜と配線材料を堆積後パターニングされていることを特徴とする半導体装置において、第2導電型高濃度拡散層と配線材料の接触面近傍において、単層の絶縁膜あるいは熱膨張係数が同程度の複層の絶縁膜を形成させることで、配線材料カバレージ向上、およびバリアメタル膜の劣化を抑制することで、配線材料の第1導電型半導体基板に拡散することを防止しリーク電流を防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】上層側と下層側の導電プラグの接続抵抗が低減された、形成が容易な積層プラグ構造を有する半導体装置を提供する。

【解決手段】不純物含有多結晶シリコンからなる第1の導電プラグと、金属からなる第2の導電プラグと、第1の導電プラグと第2の導電プラグを接続する接続導電層とを有する半導体装置であって、前記接続導電層は、第1の導電プラグの端部に接続する金属シリサイド層と、この金属シリサイド層に積層され、第2の導電プラグの端部に接し且つ第2の導電プラグを構成する金属と同種の金属からなる金属層とを有する。

(もっと読む)

基板処理方法、基板処理装置及び記憶媒体

【課題】 異常な反応を起こる可能性を低減し、半導体集積回路装置の特性並びに歩留りの維持、向上を図ることが可能な基板処理方法を提供すること。

【解決手段】 被処理基板(W)を、弗素を含む処理ガスを含む雰囲気下でガス処理し、被処理基板(W)の表面に弗素を含む反応生成物(312)を形成する第1の工程と、ガス処理後の被処理基板(W)を加熱処理し、弗素と反応する反応ガスを含む雰囲気下でガス処理する第2の工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホールの位置がずれて形成された場合でも、コンタクトプラグと半導体基板との接触を抑制すること。

【解決手段】本発明は、半導体基板10内を延伸して設けられたビットライン12と、半導体基板上に設けられた電荷蓄積層16と、電荷蓄積層上方に設けられ、ビットラインに交差して延伸するワードライン22と、ワードライン下であって、ビットライン間の電荷蓄積層上に設けられたゲート電極34と、ビットライン上に設けられ、ビットライン延伸方向に延伸する第1絶縁膜32と、第1絶縁膜の側面に接して設けられ、第1絶縁膜と異なる材料からなる第2絶縁膜30と、第1絶縁膜および第2絶縁膜上に設けられ、第2絶縁膜と異なる材料からなる層間絶縁膜24と、第1絶縁膜および層間絶縁膜を貫通し、第2絶縁膜に挟まれて設けられ、ビットラインに接続するコンタクトプラグ28と、を具備する半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】 第1の導電体と第2の導電体とのショートを防止することができる半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板上における複数の第1の導電体上に形成された中間絶縁膜と、中間絶縁膜に形成されかつ複数の第1の導電体上に位置する複数のコンタクトホールと、複数のコンタクトホール内にそれぞれに埋め込まれた複数のコンタクトプラグと、中間絶縁膜上の複数のコンタクトプラグそれぞれの上に形成されかつコンタクトプラグを介して複数の第1の導電体に電気的に接続された複数の第2の導電体と、を有する半導体装置であって、半導体基板には、複数の第1の導電体およびコンタクトプラグを第1の密度で有する第1の素子領域と、第1の素子領域の周囲に近接され複数の第1の導電体およびコンタクトプラグを第1の素子領域より低い第2の密度で有する第2の素子領域と、が形成されていること、第1の素子領域は、コンタクトプラグが中間絶縁膜の途中で終端して埋設された第2の素子領域に近接する最外周領域を有する。

(もっと読む)

半導体装置の製造方法

【課題】還元性物質による強誘電体キャパシタの劣化を抑えることが可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板1の上方に第1絶縁膜14を形成する工程と、第1絶縁膜14の上に、下部電極21a、強誘電体材料よりなるキャパシタ誘電体膜22a、及び上部電極23aをこの順に積層してなるキャパシタQを形成する工程と、キャパシタQを覆う酸化シリコンよりなる第2絶縁膜28を形成する工程と、第2絶縁膜28の上面を窒化する工程と、窒化された第2絶縁膜28の上に、酸化シリコンよりなる第3絶縁膜30を形成する工程と、第3絶縁膜30の上面を窒化する工程と、第3絶縁膜30の上面を窒化した後、該第3絶縁膜30上に金属膜を形成する工程と、金属膜をパターニングして配線50を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】内部に貫通電極を容易に形成することができ、製造歩留を向上させることのできる半導体装置を提供する。

【解決手段】半導体シリコン層上に、導電性ポリシリコンから構成される第1コンタクトパッドを有する第1絶縁層、第2コンタクトパッドを有する第2絶縁層を形成する。この後、貫通電極用のビアホールを、少なくとも半導体シリコン層および第1コンタクトパッドを貫通して第2コンタクトパッドに到達するまで形成する。

(もっと読む)

貫通電極形成方法及び半導体チップ

【課題】半導体基板における貫通電極形成を短時間でしかも低温で形成可能とし、また貫通孔への絶縁膜形成工程を削減できる貫通電極形成方法を提案する。

【解決手段】半導体ウェハ1表裏の電気的導通を得るための貫通電極用の貫通孔7を形成する前に、予め該貫通孔7を包含する大きさの表裏貫通部6を形成し、この表裏貫通部6に絶縁材3を充填して硬化させた後、前記絶縁材3に前記貫通孔7をエッチング加工あるいはレーザ加工にて形成し、さらに前記貫通孔7の内部または内壁に導電材料からなる導通経路4を設けることにより貫通電極構造とする。

(もっと読む)

表示装置用基板、表示装置及び表示装置用基板の製造方法

【課題】表示装置用基板において十分な遮光性を有する多層配線構造を提供する。

【解決手段】画素電極と、これを駆動するためにゲート電極、ソース電極及びドレイン電極を備えた薄膜トランジスタと、各電極の層及び各電極を接続する配線の層で構成される多層配線とを形成した表示装置用基板であって、多層配線は、第1配線層6と、その上に配された第2配線層15と、両配線層6,15の間に配され且つ両配線層から層間絶縁膜7,9で絶縁された金属遮光層8とを含む。第1配線層6と第2配線層15は、層間絶縁膜7,9を貫通して形成されたコンタクトホールを介して互いに電気的に接続している。コンタクトホールは、その側壁に露出した金属遮光層8の端面を電気的に絶縁被覆するためにサイドウォール13aが形成されている。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

半導体素子のデュアルダマシンパターン形成方法

【課題】デュアルダマシンパターンを成すコンタクトホールとトレンチとの境界部分に存在するホーン(horn)を効果的に除去方法の提供。

【解決手段】半導体基板上に絶縁膜218を形成し、前記絶縁膜にコンタクトホール221を形成する。前記絶縁膜の上部および前記コンタクトホールの内部に保護膜222を形成する。ハードマスクパターンを前記保護膜上に形成し、ハードマスクパターン224をマスクとした第1エッチング工程によって前記保護膜の一部および前記絶縁膜の一部をエッチングして第1トレンチ225aを形成する。前記ハードマスクパターンをマスクとした第2エッチング工程によって、前記コンタクトホールの内部に充填された前記保護膜をエッチングする。前記ハードマスクパターンをマスクとした第3エッチング工程によって前記絶縁膜の一部をエッチングして第2トレンチ225bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】誘電体メモリの微細化が進むと、上部電極の電位を拡散層へ引き出す構造におけるアスペクト比が大きくなるため、上部電極のカバレッジが悪化し、誘電体を結晶化させる熱処理時に上部電極が断線してしまう。

【解決手段】半導体装置は、半導体基板の上方に形成された第1の導電膜及び第2の導電膜と、第1の導電膜を覆うように形成された第1の絶縁膜と、第2の導電膜を覆うように形成された第2の絶縁膜と、第1の絶縁膜に形成され、第1の導電膜に達する第1の開口部と、第1の開口部の壁部及び底部に沿って形成された第3の導電膜と、第3の導電膜、第1の絶縁膜、及び第2の絶縁膜上に形成された誘電体膜と、第2の絶縁膜及び誘電体膜の積層膜に形成され、第2の導電膜に達する第2の開口部と、誘電体膜の上並びに第2の開口部の壁部及び底部に沿って形成された第4の導電膜とを備える。第2の絶縁膜の膜厚が、第1の絶縁膜の膜厚よりも薄い。

(もっと読む)

半導体素子のコンタクトプラグ形成方法

【課題】セル領域及び周辺回路領域のコンタクトプラグ形成工程の単純化及びコスト削減をする方法を提供する。

【解決手段】セル領域A及び周辺回路領域Bが定義され、上記周辺回路領域Bに第1のコンタクトプラグ110が形成された半導体基板100上に第1の絶縁膜108を形成する段階と、上記第1の絶縁膜をエッチングして上記セル領域Aには接合領域104が露出され、上記周辺回路領域Bでは上記第1のコンタクトプラグが露出される第2のコンタクトホールを形成する段階と、上記第2のコンタクトホール内に第2のコンタクトプラグ116を形成する段階と、上記周辺回路領域Bの上記第2のコンタクトホール内に形成された上記第2のコンタクトプラグを除去する段階と、上記第2のコンタクトホール側壁にスペーサ120を形成する段階と、上記第2のコンタクトホール内に第3のコンタクトプラグ124を形成する段階を含む。

(もっと読む)

半導体素子のコンタクトプラグ製造方法

【課題】ナンドフラッシュメモリ等のソース/ドレインコンタクトプラグを形成する半導体素子のコンタクトプラグ製造方法を提供する。

【解決手段】選択ラインSSLとワードラインWL0,WL1間の露出された半導体基板102に接合領域114a、114bを形成する段階と、選択ラインSSLとワードラインWL0,WL1上に第1の保護膜120を形成する段階と、第1の保護膜120上に絶縁層122を形成する段階と、選択ラインSSL間の第1の保護膜120が露出されるように選択ラインSSL間の絶縁層122にコンタクトホールAを形成する段階と、コンタクトホール側壁に露出された第1の保護膜上に第2の保護膜124を形成する段階と、コンタクトホールA底面の第1の保護膜120を除去する段階、及びコンタクトホールAに導電物質を形成して接合領域114a、114bと連結されるコンタクトプラグを形成する段階とを含む。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】動作信頼性を向上出来る半導体装置及び半導体記憶装置を提供すること。

【解決手段】メモリセルトランジスタMTと、ソースが前記メモリセルトランジスタMTのドレインに接続された選択トランジスタと、それらを被覆する層間絶縁膜51と、層間絶縁膜51よりも誘電率の高い材料を用いた絶縁膜7と、選択トランジスタのドレインに電気的に接続されたコンタクトプラグ3と、コンタクトプラグ3に接するビット線2とを具備した半導体記憶装置であって、ビット線2の底面の一部は、コンタクトプラグ3の上面よりも低く位置し、且つ絶縁膜7の表面と同じ高さに、または絶縁膜7の表面よりも高く位置し、底辺の一部はコンタクトプラグ3の側面に接する。

(もっと読む)

半導体装置およびその製造方法

【課題】微小なコンタクトを形成する場合でも、コンタクト抵抗の上昇を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に狭い間隔で配置された複数のゲート電極12と、当該ゲート電極12を被覆する層間絶縁膜20とを備える。層間絶縁膜20は、互いに隣接するゲート電極12間を充填するとともに、ゲート電極12上での膜厚が、半導体基板10の平坦面上での膜厚よりも薄い吸湿性絶縁膜15と、吸湿性絶縁膜15上に形成された非吸湿性絶縁膜16とを備える。この構造によれば、ゲート電極12間に微小なコンタクトを形成する場合でも、吸湿性絶縁膜15から放出されるH2Oに起因するコンタクト抵抗の増大を抑制することができる。

(もっと読む)

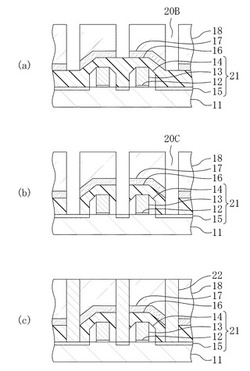

半導体装置およびその製造方法

【課題】選択ゲートトランジスタのゲート電極間のビット線コンタクトのコンタクトホール形成を確実にできるようにする。

【解決手段】シリコン基板1にメモリセルトランジスタおよび選択ゲートトランジスタのゲート電極MG、SGが形成されたもので、金属シリサイド膜8を形成した後、上面にシリコン窒化膜14を形成する。シリコン窒化膜14は、ゲート電極MG、SGの上面の膜厚に比して、ゲート電極SG−SG間の対向する側壁に厚い膜厚のスペーサ状の部分14sを有する形状に形成する。ビット線コンタクトのコンタクトホール16は、パターン幅Aに対して、シリコン窒化膜14の凹部14eで自己整合的に幅Bに狭められホール下部16bが形成され、確実にコンタクトプラグ17を形成できる。

(もっと読む)

61 - 80 / 227

[ Back to top ]