Fターム[5F033NN40]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | 配線層が3層以上に跨がるコンタクトホール (478) | 中間層を電気的に絶縁 (227)

Fターム[5F033NN40]に分類される特許

161 - 180 / 227

半導体装置の製造方法

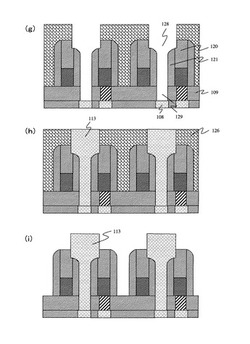

【課題】自己整合コンタクトプラグを形成する層間膜に、窒化シリコン膜のエッチング速度に対するエッチング速度比が100以上となる材料を適用し、コンタクトプラグとビット配線のショートを防止する信頼性の高いコンタクトプラグの形成方法を提供することにある。

【解決手段】上面及び側面が窒化シリコン膜120,121で覆われたビット配線を形成した後、ビット配線を覆って全面に非晶質炭素膜からなる犠牲層間膜126を形成し、犠牲層間膜126および下層層間絶縁膜109を順次にエッチングしてコンタクトホール128,129を形成し、容量コンタクトプラグ113を形成する。その後犠牲層間膜126を除去して容量コンタクトプラグ113の柱を形成し、その上に第3層間絶縁膜を形成し、さらに第3層間絶縁膜を表面から一部除去し、容量コンタクトプラグ113の表面を露出させるようにした。

(もっと読む)

半導体装置、半導体装置の製造方法および実装基板

【課題】本発明の主な目的は、貫通電極の位置が精度良く規制された半導体装置およびその製造方法を提供する。

【解決手段】本形態の半導体装置10Aは、半導体基板11の上面に活性領域20が形成され、この活性領域20は、絶縁物が埋め込まれたトレンチ24により囲まれている。また、半導体基板11を貫通して設けた貫通孔15は、その側面がトレンチ24に接触するように形成されている。貫通孔15の内部には、銅等の導電材料から成る貫通電極16が形成される。半導体基板11の下面に形成された裏面電極19は、この貫通電極16を介して活性領域20と接続されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】裏面に接続する配線構造を低コストな工程で形成することが可能な半導体装置の製造方法およびその半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、シリコン基板100の素子領域101が形成されている表面側からスクライブエリアに対してハーフカットのダイシングを行って、シリコン基板100に溝を形成するハーフカット工程と、溝のカット面に保護膜を形成する保護膜形成工程と、シリコン基板100の表面側に金属膜を形成する金属膜形成工程と、金属膜をパターニングして配線構造を形成する配線構造形成工程と、シリコン基板100の裏面をグランディングして配線構造を裏面に露出させるグランディング工程とを備えている。

(もっと読む)

ゲートに近接したコンタクト・ホールを有する半導体トランジスタ

【課題】 デバイス密度を増加させるために、S/Dコンタクト・ホールが、トランジスタ構造体のゲートに近接して形成されるが、ゲートから電気的に絶縁された、トランジスタ構造体(及びその製造方法)を提供すること。

【解決手段】 構造体、及びその製造方法である。この構造体は、(a)第1のS/D領域と第2のS/D領域との間に配置されたチャネル領域と、(b)チャネル領域上のゲート誘電体領域と、(c)ゲート誘電体領域上にあり、かつ、ゲート誘電体領域によりチャネル領域から電気的に絶縁されたゲート領域と、(d)ゲート領域上の保護アンブレラ領域であって、保護アンブレラ領域は第1の誘電体材料を含み、ゲート領域が完全に保護アンブレラ領域の影の中にある、保護アンブレラ領域と、(e)(i)第2のS/D領域の真上にあり、これと電気的に接続され、かつ、(ii)保護アンブレラ領域のエッジと位置合わせされた充填されたコンタクト・ホールであって、コンタクト・ホールは、第1の誘電体材料とは異なる第2の誘電体材料を含む層間誘電体(ILD)層によってゲート領域から物理的に分離された充填されたコンタクト・ホールと、を含む。

(もっと読む)

半導体素子のコンタクトホール形成方法

【課題】コンタクトホール形成の際に生じる非晶質カーボン膜の損傷を効果的に防止することができる半導体素子のコンタクトホール形成方法を提供すること。

【解決手段】半導体基板31上に導電パターンを形成するステップと、導電パターンを含む半導体基板31の全面に絶縁膜35を形成するステップと、絶縁膜35上に非晶質カーボン膜37及び酸化物膜38を積層するステップと、選択的エッチングによりマスクパターンを形成するステップと、マスクパターンを使用してコンタクトホール形成領域の絶縁膜35をエッチングし、コンタクトホールを形成するステップとを含む。非晶質カーボン膜37上に、従来のSiON膜に代えて、酸化物ハードマスクを用いるので、非晶質カーボンとSiONハードマスクとを自己整合コンタクトマスクとして使用する場合に生じるリフティング現象を防止することができる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】シリコン窒化膜が半導体基板に近接しないようにした半導体集積回路装置と、コンタクトホールの加工を容易にする半導体集積回路装置の製造方法を提供する。

【解決手段】素子分離領域4に囲まれたシリコン基板21上に、シリコン窒化膜をエッチングストッパーとして用いた自己整合コンタクトプロセスによって形成されたコンタクトホールに埋め込まれ、拡散層2,3に電気的に接続されたコンタクトプラグ33を有する半導体集積回路装置であって、前記拡散層2、3の露出面に選択エピタキシャル成長により形成された、各ゲート絶縁膜22の前記拡散層側端部と接するシリコン層28を形成し、各ゲート電極22と前記シリコン層28との間にシリコン酸窒化膜またはシリコン酸化膜からなる絶縁膜27’が前記ゲート絶縁膜22に接して埋め込まれており、シリコン窒化膜26,29’,32が絶縁膜27’によりシリコン基板21と隔離されている。

(もっと読む)

半導体装置の製造方法

【課題】上部の径が大きく、下部の径が小さなコンタクトを形成する際に行う絶縁膜の異方性ドライエッチングを、フォトレジスト膜との選択性が高く且つエッチストップを生ずることなくエッチングする、半導体装置の製造方法を提供する。

【解決手段】カーボンリッチなガスとO2及び希ガスとを含むエッチングガスを用い、層間絶縁膜20の途中までを選択的にエッチングして上部の大径コンタクト孔を形成する第1の異方性エッチング工程と、水素ガスを含むガスを用いて上部コンタクト孔にデポジション膜を堆積するデポジション工程と、O2を含むガスを用いコンタクト孔の底部のデポジション膜を選択的に除去する第2の異方性エッチング工程と、第1の異方性エッチング工程と同じガスを用い、層間絶縁膜20の残りの部分をエッチングして、下部の小径コンタクト孔を形成する第3の異方性エッチング工程とを有する。

(もっと読む)

化学機械的研磨を利用した自己整列コンタクトパッドの形成方法

【課題】化学機械的研磨を利用した自己整列コンタクトパッド形成方法を提供する。

【解決手段】半導体基板上に導電ライン及び絶縁キャッピング層のスタック、スペーサ、及びキャッピング層の上面を露出する絶縁層の構造を形成し、キャッピング層を選択的に部分エッチングしてダマシン溝を形成し、溝を充填する第1エッチングマスクを形成した後、第1エッチングマスク及び絶縁層部分を複数個横切って露出する開口領域を有する第2エッチングマスクを形成し、第2及び第1エッチングマスクに露出された絶縁層部分を選択的にエッチングして複数個の開口孔を共に形成し、第2エッチングマスクを除去した後、開口孔を充填する導電層を形成し、キャッピング層を研磨終了点として利用して導電層をCMPするが、残留する第1エッチングマスクが研磨中に共に除去されるようにして自己整列コンタクトパッドでノード分離する。

(もっと読む)

トランジスタの製造方法およびメモリデバイスの製造方法

【課題】DRAM用アクセストランジスタの表面領域を小さくするメモリデバイスの製造方法を提供する。

【解決手段】トランジスタの製造方法の一実施形態は、基板内のゲート用溝部を規定することによってゲート電極を形成することを含む。上記ゲート用溝部に隣り合う位置での素子分離用トレンチ毎にてプレート状部がそれぞれ規定される。上記ゲート用溝部を挟む上記2つの各プレート状部が互いに連結される。上記一実施形態では、上記2つの各プレート状部は、上記半導体基板の材料に対して、上記素子分離用トレンチの絶縁材料を選択的にエッチングするエッチングプロセスによって規定される。ゲート絶縁体は、能動領域と上記ゲート用溝部との間の界面部、および、上記能動領域と上記の各プレート状部との間の界面部において設けられる。ゲート電極の材料は、上記ゲート用溝部と上記各プレート状部とを充填するように堆積形成される。

(もっと読む)

接続構造に対するアライメント許容範囲を増大させる方法

【課題】 半導体ウェーハの上に形成される導電性突起と電気部品との間のアライメント許容範囲を増大させる。

【解決手段】角領域を画定する上表面と側表面とを有する導電性突起が基板表面領域の上方に形成され、導電性突起の角領域が、アライメント許容範囲を増大させるために傾斜を付けられる。又は、一対の導電性ラインの間の基板ノード位置の上方に、最上表面を有する導電性プラグが形成される。導電性プラグの物質は、少なくともその一部が導電性ラインよりも高さ方向に高く配置される第2最上表面を画定するために不均等に除去される。一例として、導電性プラグ物質は、導電性プラグをファセットエッチングすることにより除去することが可能である。他の例として、導電性プラグ物質がドーパントで不均等にドープされ、高いドーパント濃度を含有する導電性プラグ物質が、低いドーパント濃度を含有するプラグ物質よりも速い速度でエッチングされる。

(もっと読む)

半導体装置およびその製造方法

【課題】ロジック領域におけるトランジスタの上を応力を有する膜で覆って能力を向上させると共に、SRAM領域において、各トランジスタの能力のバランスを保持し、リーク電流の発生を抑制する事ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、N型ロジック領域NLにおけるトランジスタが引っ張り応力を有する膜50により覆われ、P型ロジック領域PLにおけるトランジスタが圧縮応力を有する膜55により覆われている。そして、P型SRAM領域PSにおけるトランジスタおよびN型SRAM領域NSにおけるトランジスタは、引っ張り応力を有する膜50aおよび圧縮応力を有する膜55aからなる積層膜により覆われている。

(もっと読む)

半導体装置の製造方法、半導体装置およびウエハ

【課題】 ウエハの薄型化に際して生じる問題を回避し、積層ウエハ間の電気的接続のための工程を短縮できる方法を提供する。

【解決手段】 基板1SAにその主面から所望の深さまで延びる深い分離溝5aを形成した後、深い分離溝5a内に絶縁膜5bを埋め込み貫通分離部5を形成する。続いて、基板1SAの主面にMOS・FET6を形成した後、基板1SAの主面上に層間絶縁膜8aを堆積する。その後、貫通分離部5で囲まれた領域内に、層間絶縁膜8aの上面から基板1SAの厚さの途中深さまで延びる深い導通溝9aを形成する。続いて、深い導通溝9a内に導体膜9bを埋め込み貫通配線部9を形成する。その後、基板1SAの裏面を、貫通分離部5および貫通配線部9が露出しない程度まで研削および研磨した後、貫通分離部5および貫通配線部9の下部の一部が露出する程度までウエットエッチング処理する。

(もっと読む)

貫通孔配線の製造方法

【課題】貫通孔配線の製造方法において、配線材料の密着力が向上した信頼性の高い配線を容易に実現可能とする。

【解決手段】半導体基板1を厚み方向に加工して半導体基板1の一方の表面1aと他方の表面1bとに開口を有する貫通孔2を形成し、その後、半導体基板1の貫通孔2内壁面を含む表面に絶縁層3を形成し、絶縁層3の形成された貫通孔2内部にめっきによってめっき金属を充填して半導体基板の貫通孔配線を製造する。絶縁層3の形成の後に、シード層となる通電用の金属層4を一方の表面1aに形成すると共に、半導体基板1の他方の表面1bに開口する絶縁層3の形成された貫通孔2の開口近傍内壁面に内壁金属層5aを形成し、半導体基板1の他方の表面1bに対向離間させて配置しためっき用電極Eと通電用金属層4との間に通電してボトムアップ方式のめっきを行う。

(もっと読む)

半導体構造およびその処理方法

【課題】ボーダレス・コンタクトを有するデュアル・ワーク・ファンクション半導体構造およびその製造方法を提供する。

【解決手段】この構造は、実質的に無キャップのゲート108と、無キャップのゲートに隣接する拡散部116への導電コンタクト134,170とを備え、導電コンタクトは、ゲートに対しボーダレスである電界効果トランジスタ(FET)を含むことができる。この構造は、デュアル・ワーク・ファンクション構造であるため、導電コンタクトを、無キャップゲートに電気的に接続することなく、無キャップゲート上に延長させることができる。

(もっと読む)

半導体装置

【課題】 高温・高湿環境下における化合物半導体素子の特性劣化を抑制する。

【解決手段】 p型GaAs層1の上に、下層Ti層2、拡散防止層3、上層Ti層4、金属層(Au)5を積層したオーミック電極6が設けられている。上記拡散防止層3として、タンタル(Ta)またはニオブ(Nb)を用いた構造とする。

上記構造とすることにより、p型GaAs層1のGa、Asと、金属層5のAuの相互拡散を防止するとともに、高温・高湿環境下において、オーミック電極6の抵抗率の変動を小さく抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のより微細化に適し、しかも低コストである半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体シリコン基板表面上に形成されたポリシリコン膜からなるゲート電極構造とこれを覆う層間絶縁膜を有する半導体装置の製造方法において、層間絶縁膜形成後、層間絶縁膜を貫いてコンタクトホールを開口させて所望のコンタクト面を露出させる工程、少なくともコンタクトホール側壁部及びコンタクト面上に絶縁膜を堆積させる工程、絶縁膜をエッチバックすることによりコンタクトホール側壁部にサイドウォール状絶縁膜を形成することを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

ウェハスルーコンタクトを有する半導体構造の製造方法及び対応する半導体構造

【課題】 容易に、かつ安全に実現することのできるウェハスルーコンタクトを有する半導体構造の製造方法を提供する。

【解決手段】 バルク領域(1a)及び活性領域(1b)を有する半導体ウェハ(1)に、活性領域(1b)の上面(0)からバルク領域(1a)に延びる複数のコンタクトトレンチ(5a〜5f)を形成し、コンタクトトレンチ(5a〜5f)の側壁及び底部に第一の誘電体分離層(8)を形成し、複数のコンタクトトレンチ(5a〜5f)に第一の導電性充填材(10)を形成し、半導体ウェハ(1)に配列され、バルク領域(1a)の裏面側(B)から複数のコンタクトトレンチ(5a〜5f)に延び、かつ導電性充填材(10)を露出するビア(V)を形成し、ビア(V)の側壁に第二の誘電体分離層(15)を形成し、露出した導電性充填材(10)と接触するビア(V)内に第二の導電性充填材(20)を提供する。

(もっと読む)

フラッシュメモリ素子およびその製造方法

【課題】安定的な自己整列コンタクトを形成すると同時にプログラム動作の際にしきい値電圧干渉現象(Vt disturbance)を最小化しかつ動作速度を向上させることができる、フラッシュメモリ素子およびその製造方法を提供する。

【解決手段】半導体基板上に形成された多数のソース選択ライン、多数のワードラインおよび多数のドレイン選択ラインと、前記ワードラインの間、前記ワードラインと前記ソース選択ラインとの間、前記ワードラインと前記ドレイン選択ラインとの間の前記半導体基板上に形成された第1絶縁膜と、前記ソース選択ライン間の前記ソース選択ラインの側壁に形成され、第2絶縁膜からなるスペーサとを含み、前記第1絶縁膜の誘電定数値が前記第2絶縁膜の誘電定数値より低いことを特徴とする。

(もっと読む)

SOG膜の形成方法

【課題】MISFETの微細化を推進することのできる絶縁膜形成技術を提供する。

【解決手段】MISFET(Qs、Qn、Qp)のゲート電極9上に形成する平坦化絶縁膜として、HSQ−SOG膜を約800℃の高温で熱処理したSOG膜16を使用する。また、上層の配線(54、55、56、62、63)間の層間絶縁膜として、上記のような高温の熱処理を施さないHSQ−SOG膜57を使用する。

(もっと読む)

半導体装置とその製造方法

【課題】 キャパシタ直下の導電性プラグが埋め込まれるホールの加工精度を高めることが可能な半導体装置とその製造方法を提供すること。

【解決手段】 第1絶縁膜11の第1、第2ホール11a、11b内に第1、第2導電性プラグ32a、32bを形成する工程と、酸化防止絶縁膜14に第1開口14aを形成する工程と、第1開口14a内に補助導電性プラグ36aを形成する工程と、補助導電性プラグ36a上にキャパシタQを形成する工程と、キャパシタQを覆う第2絶縁膜41に第3、第4ホール41a、41bを形成する工程と、第4ホール41bの下の酸化防止絶縁膜14に第2開口14bを形成する工程と、第3ホール41a内に第3導電性プラグ47aを形成する工程と、第3ホール41a内に第4導電性プラグ47bを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

161 - 180 / 227

[ Back to top ]