Fターム[5F033QQ49]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | ストッパー膜、研磨速度調整膜 (245)

Fターム[5F033QQ49]に分類される特許

161 - 180 / 245

化学・機械的研磨(CMP)中における銅のディッシングを防止するための局部領域合金化

【課題】ダマシン法を用いて銅配線を形成するに当たり、化学・機械的研磨(CMP)による銅のディッシングを低減、あるいはなくし、平坦化する方法を提供する。

【解決手段】トレンチ32を有する絶縁膜30の上にバリア層36を形成し、表面34に近い高さまで銅層38を満たす。バリア層と銅層の上に銅合金層40を形成する。この時さらに銅層44を堆積してもよい。この後CMP処理を行い平坦面34を形成する。この時、銅合金層およびバリア層が等しい速度で研磨されるように、銅合金層の合金量を調整する。これにより、銅層のディッシングが低減される。

(もっと読む)

集積回路の形成方法

【課題】

本発明は、隣接した導電体配線間の寄生容量とリーク電流とを低減するための集積回路の形成方法および、隣接した導電体配線間の寄生容量とリーク電流とを低減した集積回路を提供する。

【解決手段】

集積回路であって、半導体基板と、前記半導体基板上の低誘電体層と、前記低誘電体層内の第1の溝と、前記第1の溝内で、前記第1の溝内の前記低誘電体層を覆う第1の拡散バリア層とを含み、前記第1の拡散バリア層は、底の部分が側壁部分に接続し、前記側壁部分が、前記低誘電体層の上側表面に近い上側表面を有することを特徴とする。前記集積回路は、さらに、前記第1の溝が充たされた導電体配線を有し、前記導電体配線が、前記拡散バリア層の前記側壁部分の上側表面よりも低い表面を有し、かつ、金属キャップを、実質的に前記導電体配線上の領域にのみに直接形成することを特徴とする。

(もっと読む)

半導体装置および電気ヒューズの切断方法

【課題】電気ヒューズが中途半端に切断されると、切断動作をリトライできない。

【解決手段】電気ヒューズ200は、半導体基板(不図示)上に形成された第1の配線300および第2の配線302と、半導体基板上に形成されるとともに一端が第1の配線300に接続して設けられ、第2の配線302を第1の配線300から電気的に切断するヒューズリンク304と、半導体基板上に形成され、第1の配線300の一端および他端にそれぞれ設けられたヒューズリンク切断用の電流流入端子306および電流流出端子308と、を含む。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、半導体基板の主表面側の下地領域 350に形成された凹部351内全体にシリコン窒化膜352を形成する工程と、前記シリコン窒化膜352を酸化して該シリコン窒化膜352をシリコン酸化膜353に変換することにより、前記凹部内全体に絶縁領域を形成する工程とを有することを特徴とする。

(もっと読む)

機械的特性が改善された多孔性低k層を有するダマシン相互接続

【課題】集積回路に向けたシングル及びデュアルダマシン相互接続に関する技術を提供する。

【解決手段】ダマシン相互接続を製作する方法。本方法は、基板上に多孔性誘電体層を形成する段階、及び誘電体層内に少孔性誘電体副層を定めるために多孔性誘電体層の上部部分の中にポロゲン材料を与える段階によって開始される。キャップ層が少孔性誘電体副層上に形成され、第1の相互接続開口部を定めるためにキャップ層の上にレジストパターンが形成される。キャップ層及び誘電体層は、レジストパターンを通じてエッチングされ、第1の相互接続開口部を形成する。レジストパターンが除去され、第1の相互接続開口部を導電材料で充填することによって相互接続が形成される。余分な導電材料を除去するために、相互接続が平坦化される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】SACプロセスを用い、ビット線容量(Cb)の増加を抑えるとともに、SAC破れを防止し、且つセルコンタクトのトップ径を十分に広くすることを可能とする。

【解決手段】それぞれ保護絶縁膜105pで覆われたゲート電極104gを形成し、保護絶縁膜105p間及び前記保護絶縁膜105p上を含む全面に第1層間絶縁膜110を形成し、第1層間絶縁膜110を前記保護絶縁膜の上面が露出するまで研磨除去した後、第2層間絶縁膜111を全面に形成し、ゲート電極104g間に形成された第1及び第2層間絶縁膜を自己整合的にエッチングすることにより、コンタクトホール113を形成する。その後、コンタクトホール113を埋め込むように全面にプラグ用導電膜を形成し、そのプラグ用導電膜を第2層間絶縁膜の上面が露出するまで研磨除去することにより、コンタクトホール113内に埋め込まれた第1コンタクトプラグ114cpを形成する。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板の主表面側に形成された凹部を有する下地領域と、前記下地領域の凹部内全体に埋め込まれた塩素を含有するシリコン酸化膜とを有することを特徴とする。

(もっと読む)

デュアルダマシン用途における底部反射防止コーティング層のエッチング方法

デュアルダマシン構造においてBARC層を2工程エッチングするための方法を提供する。一実施形態において、本方法は、基板上に配置されたBARC層で充填されたビアを有する基板をエッチングリアクタ内に配置し、第1ガス混合物をリアクタに供給してビアを充填しているBARC層の第1部位をエッチングし、NH3ガスを含む第2ガス混合物をリアクタに供給してビア内のBARC層の第2部位をエッチングすることを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】二酸化炭素の排出量を低減しつつ、塗布法により高いスループットで絶縁膜を形成し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、シリコン含有化合物を溶剤に溶解してなる塗布液を供給する工程、前記半導体基板を回転させて、前記シリコン含有化合物を含む塗布膜を形成する工程、前記半導体基板の裏面に、少なくとも一部がα−ピネンであるリンス液を供給してバックリンスを施し、裏面を洗浄する工程、前記バックリンス後の前記半導体基板を乾燥して前記リンス液を除去する工程、および、前記半導体基板を熱処理して前記塗布膜から前記溶剤を除去し、前記シリコン含有化合物を含む絶縁膜を得る工程を具備することを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】微細パターンの形成工程におけるCMP時に生じる不均一性を最小化し、50nm以下の微細パターンを安定的に形成可能な半導体素子の製造方法を提供すること。

【解決手段】被エッチング層(21)上に、第1ハードマスク、第1パッド層及び第2パッド層を積層してエッチングマスクパターンを形成するステップと、エッチングマスクパターンの両側壁に、第1パッド層と同じ物質からなるスペーサを形成するステップと、エッチングマスクパターン間を埋め込むまで、第1ハードマスクとは異なり、且つ、第2パッド層と同じ物質からなる第2ハードマスクを形成するステップと、第1パッド層が露出するまで、第2ハードマスクを平坦化させるステップと、第1パッド層及びスペーサを除去するステップと、残留する第1ハードマスク(22A)及び第2ハードマスク(27B)をエッチングバリアとして、被エッチング層をエッチングするステップとを含む。

(もっと読む)

露光光遮蔽膜形成用材料、多層配線及びその製造方法、並びに半導体装置

【課題】多層配線、半導体装置等に好適に用いられ、露光光、例えば紫外線の吸収性が高い露光光遮蔽膜形成用材料等の提供。

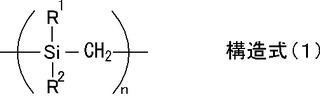

【解決手段】露光光遮蔽膜形成用材料は、構造式(1)で表されるシリコン化合物及び構造式(2)で表されるシリコン化合物のいずれかを含んでなり、R1及びR2のいずれかが露光光を吸収可能な置換基で置換されている。

(R1、R2及びR3は水素原子並びにアルキル基、アルケニル基、シクロアルキル基及びアリール基のいずれかを表す。nは2以上の整数を表す。)

(もっと読む)

窒化膜サイドウォール付きゲートの形成方法

【課題】 ストッパー窒化膜肩部の形状が垂直化され、コンタクトホールエッチングでの窒化膜の後退を低減することができる窒化膜サイドウォール付きゲートの形成方法を提供する。

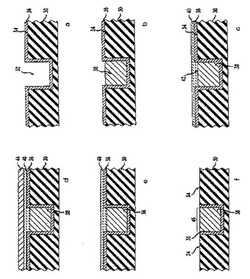

【解決手段】 自己整合プロセスによりコンタクトを形成する窒化膜サイドウォール付きゲートの形成方法において、ゲートを形成する前にシリコン基板30上にゲート材31を形成し、このゲート材31上に後述するCMP処理での膜減りを考慮して厚めのオフセット窒化膜32を生成し、その後、前記ゲート材31のゲートエッチングを行ってオフセット窒化膜付きゲートを形成し、このオフセット窒化膜付きゲート上にストッパー窒化膜を形成した後、サイドウォールエッチングにより、窒化膜サイドウォール33を形成し、その上に絶縁膜34を堆積し、その後、CMP処理を行い、垂直化したストッパー窒化膜を有するゲートを形成した後、層間絶縁膜36を形成し、さらに、レジストを塗布して、コンタクトホールを形成するためのレジストパターン37を形成する。

(もっと読む)

半導体装置とその製造方法、およびそのパターン生成方法

【課題】層間絶縁膜、特にLow−k膜を用いた場合の絶縁膜中の残留ガスによるバリアメタル等の劣化を抑制し、信頼性の高い半導体装置、その製造方法、およびパターン生成方法を提供する。

【解決手段】本発明の実施の形態に係る半導体装置10は、半導体基板上に形成された層間絶縁膜20と、この層間絶縁膜20上に形成された層間絶縁膜20よりも高い密度を有する保護膜21と、これら層間絶縁膜20および保護膜21内に形成された配線14およびダミー配線15の少なくとも一方と、を含む配線層11a〜11cと、前記層間絶縁膜20内で、前記配線14および前記ダミー配線15の被覆密度の合計が所定の規定値よりも低い低密度領域17を取り囲んで他の領域と分離する分離壁(金属壁16)と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】基板面内でゲート電極高さのばらつきが小さい半導体装置の製造方法および研磨方法を提案する。

【解決手段】半導体基板1における素子形成領域上に形成されたゲート電極4の上部にシリサイド層8を形成し、半導体装置の全体を覆うように保護膜(シリコン窒化膜)9を形成し、保護膜9上に層間絶縁膜10を形成し、層間絶縁膜10上にこの層間絶縁膜よりも研磨に対する抵抗力が大きい研磨ストッパ膜11を形成し、研磨ストッパ膜11および層間絶縁膜10を研磨し、ゲート電極4の存在に起因する凸部領域Aの外側の領域Bでの研磨ストッパ膜11の作用により研磨を停止させ、その研磨の工程の後に、研磨ストッパ膜11を除去し、ゲート電極4の全体をシリサイド化してシリサイド化ゲート電極を形成する。

(もっと読む)

半導体装置の微細パターン形成方法

【課題】パターンのCD変異を減らすことが可能な半導体素子の微細パターン形成方法を提供すること。

【解決手段】被エッチング層を有する半導体基板上に第1ポリシリコン膜28とバッファ酸化膜29を順次形成し、さらに第2ポリシリコン膜30、研磨停止膜31及び第1酸化膜32が積層された構造のハードマスクを形成する。ハードマスクの側面に窒化膜スペーサ35を形成し、全体に第2酸化膜36を形成する。第2酸化膜、窒化膜スペーサ及び第1酸化膜を研磨し、前記研磨停止膜と窒化膜スペーサを除去する。第2ポリシリコン膜と第2酸化膜をマスクとしてバッファ酸化膜をエッチングする。第2酸化膜を除去し、第2ポリシリコン膜とバッファ酸化膜をマスクとして第1ポリシリコン膜をエッチングし、第2ポリシリコン膜を除去する。バッファ酸化膜と前記第1ポリシリコン膜をマスクとして被エッチング層をエッチングする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高信頼性で高歩留まりの半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1ゲート電極14と、この第1ゲート電極14の一方の側面下の半導体基板中に形成された第1拡散層20と、第1ゲート電極14の他方の側面下の半導体基板中に形成された第2拡散層18と、この第2拡散層18の上に側面が形成された第2ゲート電極13と、第1ゲート電極14と第2ゲート電極13間を埋め込み、第1拡散層20上では、第1ゲート電極14と第2ゲート電極13間を埋め込む厚さよりも薄く形成され、窒素を主成分としない第1絶縁膜25と、この第1絶縁膜25上に形成された第2絶縁膜26と、この第2絶縁膜26上に形成され、この第2絶縁膜26とは主成分が異なる層間絶縁膜27と、第1拡散層20に接続され、第1絶縁膜25、第2絶縁膜26及び層間絶縁膜27中に形成されたコンタクト電極23とを有する。

(もっと読む)

半導体デバイスの製造方法

【課題】半導体基板の表面に形成される成膜の段差を減少させ、成膜後の平坦化処理に必要な成膜の厚さを減少させ、平坦化処理工程にかかる時間を短縮し生産性を向上させることができる半導体デバイスの製造方法を提供することを目的とする。

【解決手段】半導体デバイスの製造方法は、半導体基板WAの表面に配線用の凹部15Aを形成する工程と、凹部内に導電性材料でダミーパターン16Aを形成する工程と、ダミーパターン16Aを形成した後に、半導体基板WAの表面に成膜する工程と、前記成膜した後に、半導体基板の表面を平坦化処理する平坦化処理工程を備える。

(もっと読む)

半導体装置の製造方法

【課題】微細な配線構造を形成可能であると共に、製造コストの低い半導体装置の製造方法を提供する。

【解決手段】配線層11上の低誘電率材料からなる第1層間絶縁層13および第2層間絶縁層15のそれぞれを覆うSiO膜14,16を形成する。SiO膜14,16は、CVD法によりSiH4ガスとCO2ガスを用いて、ウェハを350℃〜500℃に加熱して形成する。このようにして形成されたSiO膜14,16は、実質的に窒素を含まないため、シリコン窒化膜等の反射防止膜18を形成する際にアンモニアガスや窒素ガス等の透過を抑制し、第1層間絶縁層13および第2層間絶縁層15に窒素に由来する塩基性物質の吸蔵を抑制する。その結果、レジストポイゾニングを抑制できる。さらに、SiO膜14,16は原料がガスのみであるので液体原料を使用するTEOS膜よりもCVD装置の汎用性が高まり、製造コストを低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】段差上に形成された絶縁膜の平坦性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10の主表面上に形成されるパターン層100と、パターン層100上に設けられる層間絶縁膜110とを備える。パターン層100は、上面の高さが相対的に高いメモリセルアレイ部1と、上面の高さが相対的に低い周辺回路部2とを含む。層間絶縁膜110は、相対的に研磨レートが高い第1の層111と、該第1の層111上に形成された相対的に研磨レートが低い第2の層112とを含む。そして、パターン層100における周辺回路部2上に位置する第1の層111の上面は、パターン層100におけるメモリセルアレイ部1の上面よりも下側に位置している。

(もっと読む)

電気的プログラム可能ヒューズおよびその製造方法

【課題】 プログラム中にシリサイド層に形成されるギャップの長さに依存しない抵抗を有するeヒューズおよびその製造方法を提供する。

【解決手段】 電気的プログラム可能ヒューズ(eヒューズ(eFuse))は、基板の絶縁酸化物層の上の(1)半導体層、この半導体層に形成された(2)ダイオード、および、ダイオード上に形成された(3)シリサイド層を含む。ダイオードは、N+、p−、P+、またはP+、n−、N+構造を含む。

(もっと読む)

161 - 180 / 245

[ Back to top ]