Fターム[5F033QQ49]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | ストッパー膜、研磨速度調整膜 (245)

Fターム[5F033QQ49]に分類される特許

81 - 100 / 245

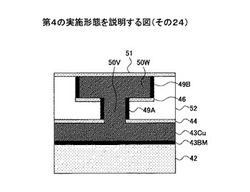

半導体装置およびその製造方法

【課題】ダマシン法による配線パターン形成の際、低誘電率膜を層間絶縁膜に使った場合においてもビアホールや配線溝の側壁面における損傷や変形の発生を抑制し、同時に、下側配線パターンと上側配線パターンとのコンタクト抵抗を低減する半導体装置の提供。

【解決手段】活性素子を有する基板と、前記基板上において前記活性素子を覆う第1の層間絶縁膜と、前記第1の層間絶縁膜中に埋設された第1の配線層43Cuと、前記第1の層間絶縁膜上に形成された第2の層間絶縁膜52と、前記第2の層間絶縁膜中に埋設された第2の配線層と、を備え、前記第2の配線層は配線パターンと、前記配線パターンから延在し前記第1の配線層を構成する導体パターンの表面と直接に接触するビアプラグ50Vとを有し、前記配線パターンの底面および側壁面、および前記ビアプラグの側壁面は拡散バリア膜49A,49Bにより覆われることを特徴とする半導体装置。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線間に空隙を有する不揮発性半導体記憶装置で、従来に比してワード線間の容量の増大を抑えることができる不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1上にゲート絶縁膜11、多結晶シリコン膜12、電極間絶縁膜13および多結晶シリコン膜14が順に積層された積層ゲート構造MGと、積層ゲート構造MGの下部のチャネル領域を挟んで形成されるソース/ドレイン領域と、を有するメモリセルトランジスタが複数隣接して配置され、隣接する積層ゲート構造MG間に空隙AG1,AG2ができるように連続したシリコン酸化膜がメモリセルトランジスタ上に形成され、電極間絶縁膜13の形成位置よりも高い位置での基板面に平行な空隙AG1,AG2の開口面積が、その位置よりも低い位置での基板面に平行な空隙AG1,AG2の開口面積よりも狭くなるように、積層ゲート構造MGの側面にシリコン酸化膜20,21が形成される。

(もっと読む)

半導体装置

【課題】CMPによる平坦化時にディッシングや配線パターン剥離の発生を抑制して安定生産が可能で、ダミーパターン内における渦電流の発生に伴うインダクタンス素子のQ値の低下を抑制可能な半導体装置を提供。

【解決手段】半導体装置10は、基板と、この基板上に形成され化学的機械的研磨工程(以下CMPと称する)を制御するためのダミーパターン16と、基板上に螺旋状に形成されたインダクタンス素子15と、を有し、ダミーパターン16Pが、それぞれ先端が鋭角の突起Apを八つ有する多角形状の平面視形状を有するように形成されている。突起の先端を挟む両側の縁部に沿ってそれぞれ発生する渦電流は、向きが互い逆方向であるため相殺されて打ち消され、大きな渦電流とならない。また、縁部に沿って流れる渦電流の経路が長くなることにより抵抗が増加し、渦電流が流れる面積も減少するので、渦電流を抑制する。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わる半導体装置は、ウェハ1内に設けられる第1及び第2半導体チップエリア21,22と、第1及び第2半導体チップエリア21,22内の各々に設けられ、トランジスタが形成される第1素子領域51,52と、第1及び第2半導体チップ51,52間に設けられるダイシングエリア3Aと、ダイシングエリア3A内に設けられ、アライメントマークが形成されるアライメント領域35と、第1素子領域51,52とアライメント領域35との間に設けられ、ウェハ1表面に対して垂直方向に突出した凸部91,92を有する凸部形成領域71,72とを具備し、凸部91,92の上端は、ウェハ1表面より高い位置にあり、トランジスタのゲート電極12上端よりも低い位置にある。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】微細な構造でも安定して製造可能な不揮発性記憶装置の製造方法を提供する。

【解決手段】第1の方向に延在する第1の配線と、前記第1の方向と非平行な第2の方向に延在する第2の配線と、前記第1の配線と前記第2の配線との間に挟持され、前記第1の配線と前記第2の配線とを介して供給される電流により、第1の状態と第2の状態との間を可逆的に遷移可能な記録層と、を有する不揮発性記憶装置の製造方法であって、前記第1の配線の層を形成する工程と、前記第1の配線の層の主面上に前記記録層の層を形成する工程と、前記記録層の層と前記第1の配線の層を選択的にエッチングして、前記第1の方向に延在する複数の積層体を形成する工程と、前記複数の積層体の間隙の表面に、気相成長法を用いて第1の絶縁層を形成する工程と、前記第1の絶縁層の上に、塗布法を用いて第2の絶縁層を形成する工程と、を備えたことを特徴とする不揮発性記憶装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】

DRAMの容量を安定化し、メモリセル部と周辺回路部の高低差を小さくして平坦化を容易にする。

【解決手段】

メモリセルトランジスタ上の第1の絶縁膜に第1のコンタクトプラグを埋め込み、エッチング特性の異なる第2、第3の絶縁膜を形成し、第3、第2の絶縁層を貫くコンタクト窓を形成し、シリンダ型蓄積電極を形成し、第2の絶縁膜をエッチングストッパとして第3の絶縁膜を除去し、キャパシタ絶縁膜、導電膜を形成し、パターニングして対向電極を形成し、対向電極に合わせて第2の絶縁膜も除去してメモリセルを形成し、周縁領域において第1の絶縁膜の上に導電膜、絶縁膜を形成し、第2のコンタクトプラグを埋め込む。第2の絶縁膜端部は、第2のコンタクトプラグに接しない。

(もっと読む)

半導体装置の製造方法

【課題】配線間の層間絶縁膜に空洞を形成する場合における配線間の層間絶縁膜の高さの減少を抑制することを目的とする。

【解決手段】半導体装置の製造方法は、基板上方に第1の層間絶縁膜を形成する工程と、

第1の層間絶縁膜上に保護膜を形成する工程と、保護膜及び第1の層間絶縁膜に配線溝を形成する工程と、酸素を含む処理ガスを用いたプラズマ処理により、第1の層間絶縁膜の側面部分に酸化膜を形成する工程と、配線溝に金属膜を形成する工程と、研磨処理により、金属膜を部分的に除去することで配線溝に金属配線を形成する工程と、保護膜及び酸化膜の除去処理により、酸化膜を除去した部分に空間を形成する工程と、第1の層間絶縁膜、金属配線及び空間を覆うように第2の層間絶縁膜を形成する工程と、を備える。

(もっと読む)

半導体デバイスのメタライゼーションシステムにおけるキャップ層のCMP及びエッチング停止層としての使用

【解決手段】

進歩的なメタライゼーションシステムを製造する間、敏感な誘電体材質上に形成される誘電体キャップ層が、過剰な金属を除去するためのCMPプロセスの間に部分的に維持されてよく、それにより、CMPプロセスの間に誘電体キャップ材質を実質的に完全に消耗する場合に従来の手法で必要であろうような専用のエッチング停止層を堆積させる必要性が回避され得る。従って、低減されたプロセスの複雑性及び/又は高い柔軟性が低k誘電体材質の高い完全性との組み合わせにおいて達成され得る。

(もっと読む)

自己整合両面垂直MIMコンデンサ

【課題】MIM(金属−絶縁体−金属)コンデンサの面積削減製造方法の提供。

【解決手段】コンデンサ誘電体の垂直部の周辺に挟持された第1伝導線124及び第2伝導線を含む垂直MIMコンデンサ。追加の伝導線は、両面コンデンサを形成して静電容量を増加させるために、コンデンサ誘電体のもう一つの垂直部によって分離された直近第1伝導線124に垂直に位置しても良い。複数の垂直MIMコンデンサは、静電容量を増加させるために、同時に平行に接続してもよい。

(もっと読む)

シリコン貫通ビアおよびこれを製作する方法

【課題】 シリコン貫通ビア構造およびシリコン貫通ビアを製作する方法を提供する。

【解決手段】 この方法は、(a)シリコン基板(100)内にトレンチ(140)を形成するステップであって、トレンチ(140)が基板(100)の上面(105)に対して開いているステップと、(b)トレンチ(140)の側壁上に二酸化シリコン層(145)を形成するステップであって、二酸化シリコン層がトレンチ(140)を充填しないステップと、(c)トレンチ内の残りの空間をポリシリコン(160)で充填するステップと、(d)(c)の後に、基板(100)内にCMOSデバイス(200)の少なくとも一部分を製作するステップと、(e)トレンチ(140)からポリシリコン(160)を除去するステップであって、誘電体層(145)がトレンチの側壁上に残存するステップと、(f)トレンチ(140)を導電性コア(255)で再充填するステップと、(g)(f)の後に、基板(100)の上面(105)の上に1つまたは複数の配線層(260)を形成するステップであって、基板(100)に隠されている1つまたは複数の配線レベルのうちの1つの配線レベル(255)の1つの電線(260)が導電性コア(255)の上面に接触するステップとを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】CMP(Chemical Mechanical Polishing)ストッパ膜を終点検出膜として利用しつつ、CMPによる平坦化精度を向上させる半導体装置及びその製造方法の提供。

【解決手段】ゲート電極3a上にはシリサイド層7aを形成するとともに、ゲート電極3b上にはシリサイド防止膜4bを形成し、半導体基板1上の第1の領域においては、シリサイド防止膜4bが露出するように、犠牲膜10、CMPストッパ膜9および層間絶縁膜8のCMPを行い、第2の領域においては、CMPストッパ膜9が露出するように、犠牲膜10のCMPを行うことで、第1の領域R1および第2の領域R2を平坦化する。

(もっと読む)

ポリシラザン溶解用処理液、およびこれを用いた半導体装置の製造方法

【課題】安定したプロセス処理が可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、ポリシラザンを溶剤に溶解してなる塗布液を供給する工程、前記半導体基板を回転させて、前記ポリシラザンを含む塗布膜を形成する工程、前記半導体基板の裏面に、リンス液を供給してバックリンスを施し、裏面を洗浄する工程、前記バックリンス後の前記半導体基板を乾燥して前記リンス液を除去する工程、および、前記半導体基板を熱処理して前記塗布膜から前記溶剤を除去し、シリコン酸化物を含む絶縁膜を得る工程を具備する方法である。前記溶剤および前記リンス液は、少なくとも一部にテルペン類を含み、酸価0.036mgKOH/g未満であることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

半導体装置の製造方法

【課題】配線抵抗の面内ばらつきを低減することが可能な半導体装置の製造方法を提供する。

【解決手段】低誘電率膜101上にキャップ絶縁膜102を形成し、キャップ絶縁膜および低誘電率膜の上部をエッチングして、配線層105aを形成する領域にキャップ絶縁膜を貫通して低誘電率膜にトレンチ103を形成する。トレンチ内およびキャップ絶縁膜上に、バリアメタル膜104と導電性材料を成膜する。バリアメタル膜をストッパとして導電性材料を第1のCMPにより平坦化する。次に、導電性材料に対する濡れ性が低誘電率膜に対する濡れ性よりも高いスラリーを用いた第2のCMPにより、導電体層、バリアメタル膜およびキャップ絶縁膜を研磨する。このとき、キャップ絶縁膜は途中まで研磨する。残ったキャップ絶縁膜をエッチング除去する。この後、バリア膜、層間絶縁膜を形成する。

(もっと読む)

カーボンナノチューブ系材料の先端部形成方法

【課題】CNT系材料と他の導電体との低接触抵抗を実現でき、あるいは他の導電体との接触に高い信頼性が確保できる技術を提供する。

【解決手段】凹所に設置され、その凹所上の空間にその先端部が突き出たCNT系材料のその突き出た先端部に、酸化性物質であるまたは酸化性物質を発生しうるガス状物質を接触させつつ、活性エネルギー線を照射する。

(もっと読む)

CMOSイメージセンサの製造方法

CMOSイメージセンサにおいて相互接続の層間剥離によるヒルロックタイプのピデフェクトの発生を回避可能なCMOSイメージセンサの製造方法が開示されている。CMOSイメージセンサの製造方法は、第1の金属相互接続を有する基板を準備するステップと、第1の金属相互接続上に中間層の絶縁層を形成するステップと、中間層の絶縁層をエッチングすることにより第1金属相互接続の一部を露光するためのコンタクトホールを形成するステップと、コンタクトホールの内側表面に沿って中間層の絶縁層上にバッファ層を形成するステップと、アニール処理を行うステップと、バッファ層をエッチングすることによりコンタクトホールの側壁にスペーサを形成するステップと、スペーサを有す、中間層の絶縁層の頂面に沿ってバリア金属層を形成するステップと、コンタクトホールがコンタクトプラグで埋められるようにバリア金属層上にコンタクトプラグを形成するステップと、および第2の金属相互接続がコンタクトプラグと接触するように中間層の絶縁層上に第2の金属相互接続を形成するステップとを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】多層配線に挟まれたある層の層間絶縁膜が厚薄各部分を有し、容易に製造することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1領域と第2領域を有する半導体基板と、第1領域の半導体基板上方に配置されたMTJと、MTJを覆うように配置され、第2領域上方よりも第1領域上方の膜厚が薄い絶縁膜と、絶縁膜中に配置され、MTJと電気的に接続された導電膜と、第1領域上方の絶縁膜上方に形成され、導電膜と電気的に接続されたビット線と、第2領域上方の絶縁膜上方に形成された配線と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線コンタクトのホールパターンと、ソース線コンタクトの溝パターンを同時に開口加工する際に、溝パターンにおける半導体基板の削れ量の増大を抑制する。

【解決手段】本発明の半導体装置は、半導体基板1上にメモリセルアレイを備え、各メモリセルにおけるホールパターンからなるビット線コンタクトをワード線方向に配列し、各メモリセルにおけるソース線コンタクトをワード線方向に延びる溝パターンから構成したものにおいて、半導体基板1の表面におけるソース線コンタクトを囲む選択ゲートトランジスタのゲート電極間の部位に、シリコン酸化膜12とRIEのバリヤ膜13とを積層して設け、半導体基板1の表面におけるビット線コンタクトを囲む選択ゲートトランジスタのゲート電極間の部位に、シリコン酸化膜12を設け、バリヤ膜が存在しないように構成した。

(もっと読む)

配線構造、半導体装置及び半導体装置の製造方法

【課題】 高周波信号の伝達も含めた配線抵抗を低減することができると共に、良好な遮蔽導体として機能する配線構造及びその配線構造を有する半導体装置を提供する。

【解決手段】 複数の配線層にそれぞれ設けられた配線1,3が互いに重複し、互いに電気的に複数層に亘り並列接続された配線構造であって、複数の配線層の少なくとも下層の一つの配線層が、少なくとも2本以上の並列配線に分離されて延伸しているスリット配線部を有し、上層の配線3からスリット配線部の並列配線の間隙に浸入して両側の並列配線と接続しているスリット接続部2aを有する配線構造とする。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜にCMPによるスクラッチが発生することを防止することや層間絶縁膜の膜厚均一性の悪化を防止することが可能な半導体装置の製造方法を提供すること。

【解決手段】キャップSiO2膜15上にアモルファスカーボン膜16を形成する工程と、アモルファスカーボン膜16をパターニングし、アモルファスカーボン膜16をハードマスクとしてエッチングによりコンタクトホール32を形成する工程と、アッシングによりアモルファスカーボン膜16を薄膜化する工程と、アモルファスカーボン膜16上にタングステン層22を形成する工程と、タングステン層22をアモルファスカーボン膜16が露出するまでタングステンCMPにより研磨する工程と、露出したアモルファスカーボン膜16をアッシングにより除去する工程とを備える。

(もっと読む)

81 - 100 / 245

[ Back to top ]