Fターム[5F033QQ49]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | ストッパー膜、研磨速度調整膜 (245)

Fターム[5F033QQ49]に分類される特許

21 - 40 / 245

多相超低誘電膜の形成方法

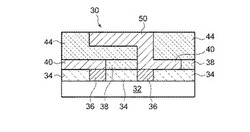

【課題】誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および膜の製造方法を提供する。

【解決手段】多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CFx膜を層間絶縁膜として有する多層配線構造の半導体装置において、低誘電率であるCFx膜の利点を生かすことができ、かつCMP処理による特性の劣化を防止することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、CFx膜を成膜する工程(a)と、CFx膜に所定パターンの凹部を形成する工程(b)と、凹部を埋めかつCFx膜上にわたって配線層を設ける工程(c)と、凹部内以外の前記CFx膜上の余剰の配線層をCMP(化学機械研磨)によって除去してCFx膜の表面を露出させる工程(d)と、を有し、工程(b)の前または後において、CFx膜の表面を窒化する工程(e)を備える。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

半導体装置の製造方法

【課題】厚みのばらつきが低減したCu配線層を形成する半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板1上に所望の配線厚みに対応する厚みのエッチングストッパー膜2を形成し、酸化膜3を形成し、マスク材4を形成し、マスク材に配線の形状の溝パターンを形成し、溝パターンが形成されたマスク材をマスクとして酸化膜に溝パターンが形成されるようにエッチングする。溝パターンが形成された酸化膜をマスクとして、溝パターンが形成されるようにエッチングストッパー膜を貫通するまでエッチングし、エッチングストッパー膜および酸化膜に形成された溝パターンを埋め込み、酸化膜の上面を覆いつくすようにCu膜5を形成し、エッチングストッパー膜をストッパーとして、その上面が露出するまでCu膜及び酸化膜にCMPを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホールの形状制御が容易な半導体装置の製造方法を得る。

【解決手段】実施形態の半導体装置の製造方法は、基板1上にゲート絶縁膜2、ゲート電極3,4、第1ハードマスク5を形成し、第1ハードマスクをパターンニングして第1マスクを形成し、これをマスクにゲート電極及びゲート絶縁膜を基板が露出するまでエッチングしラインパターンを形成し、露出した基板及び第1マスクを覆うようにライナー膜7を形成する。更にライナー膜に覆われたラインパターンの間隙を有機系絶縁膜で埋め込み、少なくともライナー膜が露出するまで有機系絶縁膜を平坦化してその上に第2ハードマスク9を形成し、第2ハードマスクを第1マスクと交差するようにパターンニングして第2マスクを形成し、第1及び第2マスクをマスクに有機系絶縁膜をライナー膜が露出するまでエッチングしてコンタクトホールを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置

【課題】ゲートコンタクトプラグ形成のためのコンタクトホールの深さを適切に制御可能とする。

【解決手段】半導体装置1は、活性領域ARを囲む第1の絶縁体ピラー21と、第1の絶縁体ピラー21の活性領域AR側の側面21sとy方向に相対向する側面22sを有する第2の絶縁体ピラー22と、第1及び第2の絶縁体ピラー21,22の上面を覆う絶縁膜31と、第1のゲート電極16と電気的に接続し、かつ少なくとも側面21s,22sを覆う第2のゲート電極23と、底面に絶縁膜31及び第2のゲート電極23が露出したコンタクトホールの内部に設けられ、かつ第2のゲート電極23の上面と電気的に接続するゲートコンタクトプラグ42とを備え、側面21s,22s間の距離は、ゲートコンタクトプラグ42のx方向の長さより短く、ゲートコンタクトプラグ42は側面21s,22s間の領域で第2のゲート電極23と電気的に接続する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】プロセスマージンを大きく取れる配線配置構造を提供する。

【解決手段】基板上に形成された複数の第1配線6を含む第1配線層と、第1配線層上に形成され、第1配線6に接続された複数のビアコンタクト10を含むコンタクト層と、コンタクト層上に形成され、ビアコンタクト10に接続された複数の第2配線14を含む第2配線層とを備える半導体装置において、コンタクトピッチは、第1配線6の最小配線ピッチ、又は、第2配線14の最小配線ピッチ、よりも大きくなるようにする。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

配線構造の形成方法および配線構造

【課題】太い幅の配線溝と細い幅の配線溝をCuの電解メッキで充填する際に、アンダープレートの発生を抑制し、化学機械研磨後におけるディッシングの発生を抑制する。

【解決手段】表面の第1の領域に縦/横比小さい第1の配線溝22Aが形成され、表面の第2の領域に縦/横比が大きい第2の配線溝22Bを形成された絶縁膜の表面上にレジスト膜R1を形成し、第1の領域を露出する第1のレジスト開口部R1Aを形成する工程と、レジスト膜をマスクに電解メッキを行い、第1の配線溝を第1の配線パタ―ン25Aで充填する工程と、第2の領域を露出する第2のレジスト開口部を形成する工程と、レジスト膜をマスクに電解メッキを行い、第2の配線溝を第2の配線パタ―ンで充填する工程と、レジスト膜を除去し、第1の配線パタ―ンおよび第2の配線パタ―ンを、それぞれの表面が絶縁膜の表面に一致するように、化学機械研磨により平坦化する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】低誘電率の絶縁膜を備える一方で、当該絶縁膜上に選択的に設けられたキャップ層を備えておらず、信頼性に優れた半導体装置を効率よくかつ確実に製造することができる製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする、ナノインデンターを用いた測定から求められる弾性率が、4.0GPa以上である絶縁膜を形成する工程を有する一方で、絶縁膜上にキャップ層を形成する工程を有していない。

(もっと読む)

絶縁膜および半導体装置

【課題】誘電率の低い絶縁膜であって、半導体装置の製造においてCMP法により当該絶縁膜上の膜を好適に除去することができるとともに、キャップ層を備えておらず、かつ、信頼性に優れた半導体装置の製造に好適に用いることができる絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成された絶縁膜であって、0.03〜20μmの膜厚を有し、ナノインデンターを用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする測定から求められる弾性率が、4.0GPa以上であることを特徴とする。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

21 - 40 / 245

[ Back to top ]