Fターム[5F033QQ49]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | ストッパー膜、研磨速度調整膜 (245)

Fターム[5F033QQ49]に分類される特許

41 - 60 / 245

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

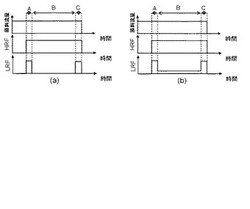

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置の製造方法

【課題】配線密度の高い領域に発生するエロージョンを抑えることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、配線8aおよび配線8aよりもパターンの密度が低い配線8bを、第1の絶縁膜3中の高密度領域4aおよび低密度領域4bにそれぞれ形成する工程と、第1の絶縁膜3の高さを下げて配線8a、8bの上部10a、10bを露出させる工程と、低密度領域4bにおける上面の最低高さが配線8a、8bの上面の高さよりも低くなるように、第1の絶縁膜3の上面、および上部10a、10bの表面を覆う第2の絶縁膜11を形成する工程と、第2の絶縁膜11上に第3の絶縁膜12を形成する工程と、配線8a、8b、および第3の絶縁膜12の研磨レートが第2の絶縁膜11の研磨レートよりも高い条件の下で第3の絶縁膜12、第2の絶縁膜11、配線8a、8bを研磨して平坦化させる工程と、を含む。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

半導体装置及びその製造方法

【課題】配線が形成される多孔質絶縁膜がプラズマダメージ等を受けるのを防ぐことにより、高歩留り且つ高信頼性な半導体装置を得られるようにする。

【解決手段】半導体基板の上に、化学気相成長法により、炭素濃度、空孔形成剤濃度及び酸素濃度がそれぞれ異なる複数の領域を有する空孔形成剤含有膜を形成する工程を備えている。この工程は、前駆体、空孔形成剤及び酸化剤を第1の流量で流す第1の期間と、第1の期間の後に、前駆体の流量に対する空孔形成剤の流量を減少させる第2の期間と、第2の期間の後に、前駆体の流量に対する空孔形成剤の流量の減少を停止し、前駆体、空孔形成剤及び酸化剤を第2の流量で流す第3の期間と、第3の期間の後に、前駆体の流量に対する酸化剤の流量を増大させる第4の期間と、第4の期間の後に、前駆体、空孔形成剤及び酸化剤を第3の流量で流す第5の期間とを含む。

(もっと読む)

半導体デバイス用基板およびSOI基板

【課題】 裏面研削加工および裏面CMP処理が施されて製造される薄型半導体デバイスに用いられる半導体デバイス用基板であって、裏面研削を過不足なく行うことが可能であるとともに、研削加工の高速化を図ることができて、生産効率を向上させることができる半導体デバイス用基板を提供することである。

【解決手段】 半導体デバイス用基板10は、結晶性のシリコン基板11の内部に、構造変化層12が形成されたものである。この構造変化層12は、導電型領域を形成することがないイオンが注入されてなる層であって、シリコンとは異なる結晶構造に変化した層である。

(もっと読む)

半導体装置の製造方法

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

半導体素子の製造方法

【課題】 デュアルダマシンプロセスを同一チャンバ内で行っても、再現性よくビアホールを貫通させる技術が望まれる。

【解決手段】 層間絶縁膜上の第1のマスク膜及び層間絶縁膜に、層間絶縁膜の厚さ方向の途中まで達するビアホールを形成する。第1のマスク膜の上に、下層レジスト膜を形成し、その上に、配線溝に対応する開口を有する第2のマスク膜を形成する。チャンバ内において、O2とCOとのプラズマを用い、下層レジスト膜をエッチングするとともに、ビアホール内の一部には、下層レジスト膜を残す。下層レジスト膜の開口の平面形状が転写された開口を、第1のマスク膜に形成するとともに、下層レジスト膜を除去し、ビアホールをさらに掘り下げて、下層配線を露出させる。層間絶縁膜を厚さ方向の途中までエッチングして配線溝を形成する。配線溝及び前記ビアホール内を、導電部材で埋め込む。

(もっと読む)

基板製造方法及び基板

【課題】CMPの処理時間を短縮する。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

(もっと読む)

電子部品の製造方法

【課題】側壁転写プロセスにより複数層に形成された配線層を有する電子部品を簡便且つ安価な方法で得ること。

【解決手段】パターン27の側壁に沿った閉ループを有する側壁膜30を形成し、このパターン27を除去して前記側壁膜30を残存させた後この側壁膜30をマスクとして下地材料を選択的に除去する側壁転写プロセスを用いて下層配線層21を形成する第1の工程と、前記下層配線層21の上層に、前記側壁転写プロセスを用いて1層以上の上層配線層41,51を他の層22,23,24,42,43,44を介して形成する第2の工程と、前記下層配線層21および前記上層配線層41,51のそれぞれを切断するエッチングを一括で行うことにより、前記下層配線層21と前記上層配線層41,51に対して閉ループカットを施す第3の工程と、を含む。

(もっと読む)

キャパシタ・モジュール・アレイを含む半導体構造とその製造方法および動作方法

【課題】漏れ電流の大きいキャパシタを電気的に切断することができるキャパシタ・モジュールを含む半導体構造、これを製造する方法、およびこれを動作させる方法を提供する。

【解決手段】モジュール化したキャパシタ・アレイは複数のキャパシタ・モジュールを含む。各キャパシタ・モジュールは、キャパシタと、このキャパシタを電気的に切断するように構成されたスイッチング・デバイスと、を含む。スイッチング・デバイスは、キャパシタの漏れのレベルを検出するように構成された検知ユニットを含み、漏れ電流が所定のレベルを超えるとスイッチング・デバイスがキャパシタを電気的に切断するようになっている。各キャパシタ・モジュールは、単一のキャパシタ・プレート、2つのキャパシタ・プレート、または3つ以上のキャパシタ・プレートを含むことができる。漏れセンサおよびスイッチング・デバイスを用いて、漏れを生じたキャパシタ・アレイのキャパシタ・モジュールを電気的に切断し、これによってキャパシタ・アレイを過剰な電気的漏洩から保護する。

(もっと読む)

ハイブリッド誘電体を備えた高信頼低誘電率相互接続構造

【課題】ハイブリッド誘電体を有する拡張型バック・エンド・オブ・ライン(BEOL)相互接続構造を提供すること。

【解決手段】ビア・レベルでの層間誘電体(ILD)は、ライン・レベルでのILDとは異なることが好ましい。好ましい実施形態では、ビア・レベルのILDを低k SiCOH材料で形成し、ライン・レベルのILDを低kポリマー熱硬化性材料で形成する。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

埋め込み配線を有する半導体装置及び埋め込み配線の製造方法

【課題】ディッシングを抑制できる太幅の埋め込み配線を有する半導体装置、及びディッシングを抑制できる太幅の埋め込み配線の簡易な製造方法を提供する。

【解決手段】金属製埋め込み配線を有する半導体装置であって、該埋め込み配線の表面の長さ方向に、所定値以下の間隔で、該金属よりも硬度の高い金属材料からなるバリア線6が配設されていることを特徴とする半導体装置及びその埋め込み配線の製造方法。

(もっと読む)

半導体基板上のスルーインターコネクトを製造する方法

半導体基板のスルーインターコネクトを製造する方法は、基板の第1側部上に基板を部分的に通るビアを形成するステップと、第1側部上及びビア内に電気絶縁層を形成するステップと、絶縁層上にビアを少なくとも部分的にライニングする導電層を形成するステップと、ビア内の導電層上に第1コンタクトを形成するステップと、ビア内の、少なくとも絶縁層まで基板の第2側部から基板を薄層化するステップとを含む。また、本方法は、第1コンタクトと電気接続状態にある第2コンタクトを基板の第2側部に形成するステップをも含み得る。本方法は、ウエハスケールのインターコネクト要素を形成するように半導体ウエハ上で実行可能である。さらに、インターコネクト要素を、発光ダイオード(LED)システムのような半導体システムを構築するのに使用可能である。 (もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法を使用して配線を形成する半導体装置の製造技術において、信頼性の高い配線を形成する技術を提供する。

【解決手段】ハードマスク膜HM1上にハードマスク膜HM2が形成され、このハードマスク膜HM2上に有機樹脂膜ORFが形成された状態で、レジストCMPを実施する。これにより、ハードマスク膜HM2上に形成されている有機樹脂膜ORFが除去されるとともに、ハードマスク膜HM2の膜厚が膜減りする。その後、膜減りしたハードマスク膜HM2を除去し、露出したハードマスク膜HM1をマスクにしてトレンチを加工する。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造等を含む半導体装置の製造工程を簡略化する。

【解決手段】半導体装置の製造方法は、基板101上に絶縁膜102を形成する工程(a)と、絶縁膜102上にハードマスク膜103を形成する工程(b)と、ハードマスク膜103上に第1のモールド108を接触させて、陽極酸化により第1の酸化領域110を形成する工程(c)と、ハードマスク膜103上に第2のモールド111を接触させて、陽極酸化により第2の酸化領域112を形成する工程(d)と、第1の酸化領域110及び第2の酸化領域112を除去してハードマスク103aを形成する工程(e)と、ハードマスク103aをマスクとするエッチングにより、絶縁膜103中に接続孔104及び配線溝105を形成する工程(f)とを備える。第1の酸化領域110と第2の酸化領域112とは面積及び深さが異なる。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、固体撮像装置に含まれる配線層間の絶縁膜の平坦性の向上に有利な技術を提供することを目的とする。

【解決手段】半導体基板上に、第1の配線層の導電パターンと、当該導電パターンの上部を覆う絶縁性を有する第1の研磨停止層とを形成する第1の形成工程と、第1の研磨停止層が形成された半導体基板上に層間絶縁層を形成する工程と、層間絶縁層の上に、半導体基板の少なくとも受光領域を覆うように絶縁性を有する第2の研磨停止層を形成する第2の形成工程と、導電パターンの上部を覆う第1の研磨停止層が少なくとも露出し、且つ受光領域を覆う第2の研磨停止層の少なくとも表面が研磨されるまで、第2の研磨停止層が形成された半導体基板の上側表面を平坦化するように研磨する研磨工程と、研磨された半導体基板に、第2の配線層の導電パターンを形成する工程とを含むことを特徴とする固体撮像装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】銅を用いた多層配線を有する半導体装置を高性能化する。

【解決手段】シリコン基板上に第1配線層用絶縁膜Z1を形成し、第1配線層用絶縁膜Z1に第1配線用孔部H1を形成する。その後、第1配線用孔部H1の側壁および底面を覆うようにして、タンタルまたはチタンを含む下部バリア導体膜eb1と、ルテニウムを主体とする上部バリア導体膜et1とからなる第1配線用バリア導体膜EM1を形成する。続いて、上部バリア導体膜et1をシード層として、電気めっき法により、銅を主体とする第1配線用導体膜EC1を形成し、CMP法により第1配線用導体膜EC1を第1配線用孔部H1に埋め込む。特に、上部バリア導体膜et1として、1〜5%の濃度で炭素を含ませるようにして、ルテニウムを主体とする導体膜を形成する。

(もっと読む)

不揮発性記憶装置

【課題】第1の配線と第2の配線との交差部に整流素子と不揮発性記憶素子を有する不揮発性記憶装置で、従来に比して高さを抑えることができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するビット線BLと、ビット線BLとは異なる高さに形成され、第2の方向に延在するワード線WLと、ビット線BLとワード線WLとが交差する位置にビット線BLとワード線WLの間に挟持されるように配置される抵抗変化型メモリセルと、を備え、抵抗変化型メモリセルは、抵抗変化素子20がN型半導体層10とP型半導体層30で挟まれた構造を有する。

(もっと読む)

41 - 60 / 245

[ Back to top ]