Fターム[5F033QQ90]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 窒化処理 (195)

Fターム[5F033QQ90]に分類される特許

121 - 140 / 195

成膜方法

【課題】 低温のプロセス温度によるタングステン膜の形成工程を用いることで、バリヤ層として十分な膜厚を得るために従来行われた熱CVDによるTiN膜の形成工程を省略することが可能な成膜方法を提供する。

【解決手段】 真空引き可能な処理容器内にて被処理体Wの表面に所定の膜を形成する方法において、前記被処理体の表面にチタン膜32を形成するチタン膜形成工程と、前記チタン膜の表面を窒化して窒化膜34を形成する窒化工程と、前記被処理体の表面に、還元ガスとタングステン含有ガスとを交互に間欠的に1回、或いは複数回繰り返し供給しつつ比較的低温でタングステン膜36を形成するタングステン膜形成工程と、を有する。これにより、バリヤ層として十分に機能するタングステン膜を形成する。

(もっと読む)

半導体装置及び当該半導体装置を具備する電子機器

【課題】無線通信によりデータの交信が可能な半導体装置において、復調信号を基に生成したクロックを利用するために引き起こされる誤動作するまたは応答しない等の動作不良を防止することを課題とする。

【解決手段】無線信号を受信するためのアンテナ回路と、アンテナ回路で受信した前記無線信号により電源を生成する電源回路と、電源が供給されるクロック発生回路と、を有し、クロック発生回路には、自己発振するリングオシレータと、リングオシレータの出力信号を適切な範囲の周波数に調整する分周器を設け、周波数の精度が高いクロックをもってディジタル回路部を駆動することで、誤動作するまたは応答しない等の動作不良を防止する。

(もっと読む)

アレイ基板、これを有する表示装置及びその製造方法

【課題】配線抵抗及び不良が減少したアレイ基板を提供する。

【解決手段】絶縁基板120上にバリア層を形成する。その後、バリア層上に銅または銅合金を含むゲートライン131及びゲートラインに電気的に接続されるゲート電極118を形成する。その後、ゲートライン131及びゲート電極118の表面を窒化プラズマ処理する。続いて、絶縁基板120上にゲートライン131及びゲート電極118をカバーするゲート絶縁膜126を蒸着する。続いて、ゲート絶縁膜126上にデータライン133、データライン133に電気的に接続されるソース電極117、ソース電極117と離隔されて配置されるドレイン電極119、及びゲート電極118上でソース電極117とドレイン電極119との間に配置される半導体パターンを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れ、また、書込み電圧を低減することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、互いに離間して形成された一対の不純物領域18a,18bの間にチャネル形成領域14を有する半導体層または半導体基板と、半導体層または半導体基板の上方であってチャネル形成領域14と重なる位置に、第1の絶縁層16、少なくとも一つ以上の層は、絶縁性であり、電荷を保持するトラップを有する層である異なる窒化化合物で形成される複数の層20、第2の絶縁層22、制御ゲート24を有する。

(もっと読む)

液晶表示装置、液晶表示装置を具備した電子機器

【課題】入力信号のHレベルとLレベルとを同時にレベルシフトすることができ、且つ低コストで製造できるレベルシフタ、及びレベルシフタを具備する表示装置を提供することを目的とする。

【解決手段】単一の導電型のトランジスタで構成されたオフセット回路を用いて、入力信号をオフセットする。そして、オフセットされた入力信号をオフセット回路と同じ導電型のトランジスタで構成された論理回路に供給することによって、入力信号のHレベルとLレベルとを同時にレベルシフトすることができる。また、オフセット回路と論理回路は単一の導電型のトランジスタで構成されているため、表示装置を低コストで製造することができる。

(もっと読む)

アクティブマトリクス型表示装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】高度に微細化が進んでもコンタクト抵抗、バリア性及び金属埋め込み特性の三者を同様に満足のいくものとする高信頼性のコンタクトプラグ構造を有した半導体装置の製造方法を提供する。

【解決手段】下層と上層の電気的接続をするため絶縁膜41にコンタクトホール42を形成し、コンタクトホール42内に第1の高融点金属膜43を堆積し、第1の高融点金属膜43の表面を窒化し、第1の高融点金属膜の窒化表面44上に第2の高融点金属膜45を堆積し、第2の高融点金属膜45を熱処理により窒化物46に変化させる。

(もっと読む)

半導体装置の製造方法

【課題】 制御電極と電荷蓄積層との間に優れた絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11上に形成された第1の絶縁膜12と、第1の絶縁膜上に形成された電荷蓄積層13と、電荷蓄積層上に形成された第2の絶縁膜20と、第2の絶縁膜上に形成された制御電極とを備えた半導体装置の製造方法であって、第2の絶縁膜を形成する工程は、酸素及び金属元素を含有した下層絶縁膜201を形成する工程と、下層絶縁膜に対して酸化性ガスを含む雰囲気下で熱処理を施す工程と、熱処理が施された下層絶縁膜上に水素及び塩素の少なくとも一方を含んだ成膜ガスを用いて上層絶縁膜202を形成する工程とを備える。

(もっと読む)

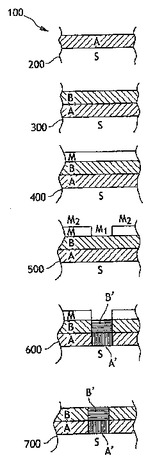

特性が制御された多層構造物の製造方法

本発明はn層の所定材料の元素状活性層(nは2以上の整数)を含む多層構造物を支持体上に製造する方法(100)に関する。この方法は、第1の元素状材料活性層の成膜工程(200)と、n番目の元素状材料活性層の成膜工程(300)とを含む方法であって、特性が制御された多層構造物を得るために、成膜されたn層の材料元素状活性層上に、n層の元素状活性層のそれぞれの個々の特性を変性させるのに適したイオン種をレジストを介して注入する単一の工程(600)を含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】 FRAMの強誘電体容量素子を形成する際に強誘電体を酸素雰囲気中で熱処理しても位置合わせマークの溝に埋設するW膜の酸化を防止することができる

【解決手段】 強誘電体容量をメモリとして用いた半導体装置の製造に際して、溝状に掘って形成した位置合わせマーク1に埋設したW膜2が酸化することを防止した半導体装置の製造方法において、該強誘電体容量を形成する前に、該W膜2をP−SiN(SiON)からなる酸化防止膜3によって覆い、次いで、該酸化防止膜3に熱処理を行って予め熱収縮させるように構成する。

(もっと読む)

半導体装置の製造方法及び磁気ヘッドの製造方法

【課題】高温環境下における配線層内でのボイドの発生を抑制して配線層の導通不良を抑制し、半導体装置の信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜34に、配線溝38を形成する工程と、配線溝38内に、Cuを主材料とする配線層44を形成する工程と、配線溝38内に埋め込まれた配線層44の表面に、アンモニア及び水素が溶解された純水を含ませた布2を摩擦させる布摩擦処理を行う工程とを有する。

(もっと読む)

強誘電体メモリ装置、強誘電体メモリ装置の製造方法

【課題】信頼性の高い強誘電体メモリ装置を提供する。

【解決手段】本発明の強誘電体メモリ装置は、第1電極32と第2電極36との間に強誘電体層34を有してなる強誘電体キャパシタ30を備え、前記第2電極36に接続される配線44を有し、前記配線44が、(111)面方位に配向を有する窒化チタンからなる第1配線層41と、当該第1配線層41上に形成され、(111)面方位に配向を有する窒化チタンアルミニウムからなる第2配線層42と、を含むことを特徴とする。

(もっと読む)

強誘電体メモリおよびその製造方法

【課題】強誘電体層の結晶配向性が良好に制御された強誘電体メモリおよびその製造方法を提供する。

【解決手段】本発明にかかる強誘電体メモリ100の製造方法は、基体の上方にチタンを構成元素として含む第1の金属層を形成する工程と、第1の金属層を窒化して窒素化合物からなる第1の配向制御層12を形成する工程と、第1の配向制御層の上方にチタンを構成元素として含む第2の金属層を形成する工程と、第2の金属層を窒化して窒素化合物からなる第2の配向制御層112を形成する工程と、第2の配向制御層の上方に第1電極32を形成する工程と、第1電極の上方に強誘電体層34を形成する工程と、強誘電体層の上方に第2電極36を形成する工程と、を含む。

(もっと読む)

強誘電体メモリおよびその製造方法

【課題】強誘電体層の結晶配向性が良好に制御された強誘電体メモリおよびその製造方法を提供する。

【解決手段】

本発明にかかる強誘電体メモリ100の製造方法は、絶縁層26を形成する工程と、前記絶縁層を貫通するコンタクトホール22を設ける工程と、コンタクトホールの側面および底面と、絶縁層の上方に配向制御層12を形成する工程と、配向制御層の上方に導電層20aを成膜する工程と、絶縁層の上方において配向制御層が露出するように、導電層を研磨する工程と、配向制御層の上方に第1電極32を形成する工程と、第1電極の上方に強誘電体層34を形成する工程と、強誘電体層の上方に第2電極36を形成する工程と、を含む。

(もっと読む)

強誘電体メモリおよびその製造方法

【課題】強誘電体層の結晶配向性が良好に制御された強誘電体メモリおよびその製造方法を提供する。

【解決手段】本発明にかかる強誘電体メモリ100の製造方法は、(a)導電層20を形成する工程と、(b)導電層の表面をアモルファス化してアモルファス層を形成する工程と、(c)導電層の上方に配向制御層12を形成する工程と、(d)配向制御層の上方に第1電極32を形成する工程と、(e)第1電極の上方に強誘電体層34を形成する工程と、(f)前記強誘電体層の上方に第2電極36を形成する工程とを含む。

(もっと読む)

基板の製造方法及び基板処理装置

【課題】工程数を増やすことなく、Mo酸化物を除去すると共にMo酸化物の基板への付着を抑制する基板の製造方法を提供する。

【解決手段】本発明に係る基板の製造方法は、基板上にモリブデンを含む層を形成し、前記モリブデンを含む層が露出した状態において、前記基板に対し、少なくとも窒素ガスを用いた大気圧プラズマ処理を行うものである。このような構成により、工程数を増やすことなく、Mo酸化物を除去すると共にMo酸化物の基板への付着を抑制する基板の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタ等のデバイスを構成する各層の結晶配向に優れた半導体装置を提供する。

【解決手段】本発明の半導体装置は、基板10上の層間絶縁膜26に形成された貫通孔24内に設けられてなるプラグ20を介した導電接続構造を具備した半導体装置であり、前記プラグ20が前記貫通孔24内に第1導電膜を埋め込んでなるプラグ導電層22を有しており、少なくとも前記プラグ導電層22上には、シリコンからなる第2導電膜21と、自己配向性を有する導電材料からなる窒化チタン層12とが積層されている。

(もっと読む)

半導体装置およびその製造方法

【課題】配線のマイグレーション耐性を向上させるとともに、シリコンの配線内部への拡散を抑制する。

【解決手段】半導体装置100は、シリコン基板101、シリコン基板101上に設けられ、SiCN膜103、SiOC膜105およびSiO2膜107からなる第一絶縁膜、当該第一絶縁膜中に設けられ、主として銅含有金属からなる第一銅配線111、を含む。第一銅配線111の内部の表面近傍に、シリコンが導入されたSi−O偏在層115を有し、導入されたシリコンの少なくとも一部が、Si−O結合を形成している。

(もっと読む)

半導体装置

【課題】入出力配線やゲート配線などのように、長い距離にわたって形成されるような配線を低抵抗化し、動作性能の高い半導体装置を提供する。

【解決手段】画素部に形成されたゲート配線、若しくは駆動回路と外部入力端子とを電気的に接続する入出力信号配線、を有し、前記ゲート配線若しくは前記入出力配線は、前記第1及び第2の薄膜トランジスタのゲート電極と同一層で且つ同一材料からなる第1配線と、前記第1配線の上に形成された第2配線と、を有し、前記第2配線は、前記第1配線よりも抵抗率が低い材料を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性を向上することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を備えている。下部配線14が形成された層間絶縁膜11上に層間絶縁膜1を積層して形成する。下部配線14に達する上部孔5を層間絶縁膜1に開口する。上部孔5に連通するトレンチ6を形成する。上部孔5内をウエットエッチングすることにより、下部孔17を下部配線14内に形成する。トレンチ6の側面および底面と、上部孔5の側面と、下部孔17の底面とにバリアメタル2を形成する。下部孔17の底面に存在するバリアメタル2を物理的にエッチングすることにより、下部孔17の側面17aに導電膜15を形成する(エッチング工程)。エッチング工程の後に、Nなどの元素を含むプラズマを用いて層間絶縁膜1を形成する。トレンチ6内、上部孔5内および下部孔17内を埋めるようにCu膜4を形成する。

(もっと読む)

121 - 140 / 195

[ Back to top ]