Fターム[5F033QQ90]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 窒化処理 (195)

Fターム[5F033QQ90]に分類される特許

61 - 80 / 195

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、絶縁膜の誘電率を低く維持すると共に、半導体装置の信頼性を高めること。

【解決手段】シリコン基板1の上方に層間絶縁膜29を形成する工程と、層間絶縁膜29に配線溝29aを形成する工程と、層間絶縁膜29の上面と配線溝29aの中とに導電膜27を形成する工程と、導電膜27を研磨することにより、層間絶縁膜29の上面から導電膜27を除去すると共に、配線溝29aの中に導電膜27を残す工程と、導電膜27の表面を還元性プラズマに曝す工程と、導電膜27の表面にシリサイド層34を形成する工程と、シリサイド層34の表面に窒化層36を形成する工程と、炭素を含むガス又は液に層間絶縁膜29の上面を曝す工程と、層間絶縁膜29の上面に紫外線を照射する工程と、導電膜27の上にバリア絶縁膜40を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】導電性プラグの上に低誘電率絶縁膜を堆積させる場合、低誘電率絶縁膜の膜厚均一性の悪化による配線のオープン不良もしくはショート不良の発生を抑え、また低誘電率絶縁膜の機械強度や密着性の低下による信頼性の低下を抑えることを目的とする。

【解決手段】半導体装置の製造方法は、半導体基板の上に、第1の絶縁膜を形成する工程(a)と、工程(a)の後に、第1の絶縁膜を貫通する導電性プラグを形成する工程(b)と、工程(b)の後に、導電性プラグの上面に保護膜を形成する工程(c)と、工程(c)の後に、第1の絶縁膜の上および保護膜の上に第2の絶縁膜を形成する工程(d)と、工程(d)の後に、保護膜の上面に達するように第2の絶縁膜を貫通する配線溝を形成する工程(e)と、工程(e)の後に、保護膜を除去する工程(f)と、工程(f)の後に、配線溝内に配線を形成する工程(g)とを備えている。

(もっと読む)

薄膜の成膜方法及び成膜装置

【課題】被処理体の凹部の径が小さくても、例えばバリヤ層として機能する薄膜が凹部の側壁へ堆積することを抑制しつつ、凹部の底部に効率的に堆積させることが可能な薄膜の成膜方法を提供する。

【解決手段】表面に凹部6が形成されている被処理体Wの表面に薄膜を形成する成膜方法において、凹部の内面を含む被処理体の表面にチタン化合物ガスと還元ガスとを用いてチタン膜100を形成するチタン膜形成工程と、窒化ガスを用いてチタン膜を全て窒化して第1の窒化チタン膜104を形成する窒化工程と、凹部の内面を含む被処理体の表面に第2の窒化チタン膜106を堆積させて形成する窒化チタン膜堆積工程と、を有する。これにより、被処理体の凹部の径が小さくても、薄膜が凹部の側壁へ堆積することを抑制しつつ、凹部の底部に効率的に堆積させる。

(もっと読む)

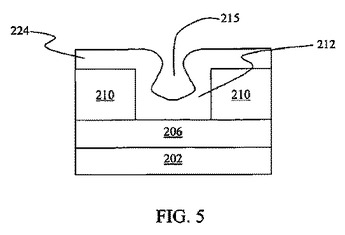

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置及び半導体装置の製造方法

【目的】Cu配線上に形成されるCuとSiとを含有する化合物膜の余剰SiがCu配線中へと拡散することを防止した半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、SiとOとが他より多く含まれる領域を有するCu配線となるCu膜260,262と、Cu膜260,262上に選択的に形成された、CuとSiとを含有する選択キャップ膜280と、Cu膜260,262の側面側に形成された層間絶縁膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜中の水分による配線メタルの腐食を防止することができ、配線の信頼性向上をはる。

【解決手段】埋め込み配線を有する半導体装置であって、一部に配線用溝113が形成された配線間絶縁膜111,112と、配線間絶縁膜111,112の配線用溝113内に埋め込み形成され、且つ配線用溝113の側壁面との間にギャップを有する金属配線層115と、配線層115の側壁面と上面を覆うように形成された耐水性バリア層118とを備えた。

(もっと読む)

半導体装置及びその作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子と、半導体素子上の絶縁膜と、絶縁膜中に、欠陥の多い領域と欠陥の少ない領域とを有し、欠陥の多い領域は、金属元素が拡散され、絶縁膜の表面の一部と裏面の一部をつなぐ導電領域である半導体装置、及び、基板上に半導体素子を形成し、半導体素子上に絶縁膜を形成し、絶縁膜上に、半導体素子と電気的に接続された第1の導電膜を形成し、絶縁膜中にイオンを添加して、あるいはレーザビームを照射して、欠陥の多い領域を形成し、欠陥の多い領域上に、金属元素を含む導電材料を形成し、欠陥の多い領域に、金属元素を拡散させ、絶縁膜中に、第1の導電膜と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細コンタクト孔の形状寸法を安定させつつ、コンタクト抵抗ばらつきを低減することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11上にニッケルを含む金属シリサイド層12を形成し、その最表面12aを窒化した半導体装置を構成する。この構造によれば、金属シリサイド層最表面12aの窒化により、金属シリサイド層12中に存在するシリコンのダングリングボンドと窒素が結合するため、金属シリサイド層12中への酸素の拡散を抑制することができる。したがって、金属シリサイド層12の酸化による電気的絶縁を低減できるため、コンタクト抵抗を安定化することができる。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの開口が容易であり、歩留まりが改善され、キャパシタ特性が向上した強誘電体メモリ等の半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に層間絶縁膜6を形成する工程と、層間絶縁膜6を貫通し半導体基板表面を露出する第1のホール及び第2のホールを形成する工程と、第1のホール及び第2のホールにそれぞれ導電膜を埋め込んで第1のプラグ10及び第2のプラグ10を形成する工程と、層間絶縁膜6上に第1のプラグ10と接続し、順に積層された導電性バリア膜、下部電極、誘電体膜、及び上部電極を有するキャパシタCを形成する工程と、キャパシタC、層間絶縁膜6、及び第2のプラグ10を覆うように少なくとも1つのAlON層を有する水素バリア膜20を形成する工程と、を備える。

(もっと読む)

誘電体層と導電性層との間の付着性改善およびエレクトロマイグレーション改善

基板を加工処理するための方法および装置を提供する。基板を加工処理するための方法は、導電性材料を備えた基板を準備することと、導電性材料上に前処理プロセスを実行することと、シリサイド層を形成するために導電性材料上にシリコン系化合物を流すことと、シリサイド層上に後処理プロセスを実行することと、基板上にバリア誘電体層を堆積することとを含む。  (もっと読む)

(もっと読む)

半導体集積装置の製造方法

【課題】金属銅膜や金属タングステン膜に対して有効なバリアメタルを提供する。

【解決手段】半導体集積装置のバリアメタル14として、WNx或いはWSiNxを用いる。これにより、金属銅膜や金属タングステン膜に対して有効にバリア機能を発揮させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 耐湿(耐水分、耐水素)性の優れた強誘電体膜を有するキャパシタのパッド構造を備え、パッドに傷が生じても、水素、水分に対する耐性を回復することのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 半導体基板の上方に電極間に挟まれた強誘電体膜を備えたキャパシタを形成する工程と、半導体基板の上方にキャパシタの電極と電気的に接続されるパッド電極を形成する工程と、半導体基板の上方にパッド電極を保護する保護膜を形成する工程と、保護膜にパッド電極の少なくとも一部が露出する開口部を形成する工程と、パッド電極の表面に測定端子を当てる工程と、測定端子を当てたパッド電極の表面をエッチングする工程と、保護膜とパッド電極の開口部を覆う水素吸蔵膜を形成する工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】コンタクトプラグ材料の基板への拡散を抑制する半導体装置及び半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、半導体基板200と導通するコンタクトプラグとなるCu膜260と、Cu膜260の少なくとも底面側に、半導体基板200と接触して配置された柱状結晶構造をもつTiN膜242と、Cu膜260の少なくとも底面側に、TiN膜242と接触して配置された、TiNのアモルファス膜244と、Cu膜260の底面側と側面側に、少なくとも一部がアモルファス膜244とCu膜260とに接触して配置された、TiN膜242材と同じ材料で柱状結晶構造をもつTiN膜246と、Cu膜260の側面側に配置されたSiO2膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】半導体装置に適用される比較的膜厚の厚い絶縁膜中の水素濃度を大幅に低減する。

【解決手段】半導体装置70には、半導体基板1上に複数のメモリセルトランジスタが設けられる。n型拡散層7、シャロートレンチアイソレーション(STI)2、及び絶縁膜6上と、側壁絶縁膜8の側面とには積層シリコン窒化膜9が形成される。メモリセルトランジスタのゲートの周囲に積層シリコン窒化膜9が設けられる。積層シリコン窒化膜9は、例えば膜厚が略100nmであり、n層のシリコン窒化膜から構成される。n層のシリコン窒化膜の膜厚は、それぞれ3nm以下に設定される。n層のシリコン窒化膜は、それぞれ膜中の水素結合がプラズマ処理で置換され、水素が離脱され、膜中の水素濃度が大幅に低減されたシリコン窒化膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】十分なEM耐性および配線間TDDB寿命を確保しつつ、層間絶縁膜の低誘電率化を行っても絶縁膜ライナー膜厚を薄くすることができ、配線間の実効比誘電率Keffを低減した高速で高信頼性な配線を得ることができる。

【解決手段】第1の絶縁膜1には配線溝M1が形成されており、配線溝M1内にはCu膜2bが設けられている。Cu膜2bの上にはSiCN膜3a、SiCO膜3bおよびSiOC膜4aが順に設けられており、SiOC膜4aはSiCN膜3aおよびSiCO膜3bよりも低誘電率な絶縁膜である。SiCO膜3bの上面には、高密度化処理が施されて高密度膜3cが形成されている。

(もっと読む)

絶縁膜の形成方法

【課題】高誘電率ゲート絶縁膜としての使用に適し、高誘電率窒化金属シリケート膜を含んでなる絶縁膜を形成する。

【解決手段】金属原子及びシリコン原子が酸化反応を生じ難い雰囲気中にてスパッタ法によりシリコン基体101上に金属及びシリコンからなる膜102を堆積する第1の工程と、膜102を窒素プラズマを用いて窒化して窒素、金属及びシリコンからなる膜103を形成する第2の工程と、膜103を酸素プラズマを用いて酸化して窒化金属シリケート膜104を形成する第3の工程とを含む。第1の工程の終了から第2の工程の開始までの間、膜102を、その酸化反応が生じ難い雰囲気中に保持する。第3の工程により、膜104の下のシリコン基体101の表層部を酸化してシリコン酸化膜105を形成する。金属は、少なくともハフニウム及びジルコニウムのうちのいずれかを含む。

(もっと読む)

高信頼性銅配線及びその製造方法

【課題】銅配線を用いる半導体装置において、銅配線の酸化を防ぐと共に、配線間誘電率を低下させる。

【解決手段】半導体装置10は、半導体基板上に形成された第1の層間絶縁膜11と、第1の層間絶縁膜11上に埋め込まれて形成され、銅を含む導電膜12bを有する配線12と、配線12上を含む第1の層間絶縁膜11上に形成された絶縁性バリア膜15と、絶縁性バリア膜15上に形成され、低誘電率膜からなる第2の層間絶縁膜16と、導電膜12bと絶縁性バリア膜15との間に導電膜12上を覆うように形成され、銅よりも酸化還元電位の大きい元素を含む合金層17とを備える。

(もっと読む)

61 - 80 / 195

[ Back to top ]