Fターム[5F033QQ90]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 窒化処理 (195)

Fターム[5F033QQ90]に分類される特許

101 - 120 / 195

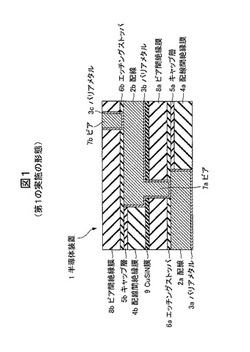

半導体装置、およびその製造方法

【課題】配線間絶縁膜からビア間絶縁膜への水分の移動を抑制し、配線間の実効誘電率に与える影響の少ない絶縁膜を有する半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置1は、表面に半導体素子を有する半導体基板と、前記半導体基板上に形成された配線2bと、前記配線2bと同じ層に形成された配線間絶縁膜4bと、前記配線2bの下面に接続された第1のビア7aと、前記第1のビア7aと同じ層に形成された第1のビア間絶縁膜8aと、前記配線2bの上面に接続された第2のビア7bと、前記第2のビア7bと同じ層に形成された第2のビア間絶縁膜8bと、前記配線間絶縁膜4bと前記第1のビア間絶縁膜8aとの間、および前記配線間絶縁膜4bと前記第2のビア間絶縁膜8bとの間の少なくともいずれか一方に形成されたCuSiN膜9と、を有する。

(もっと読む)

薄膜トランジスタ製造方法、液晶表示装置製造方法

【要 約】

【課題】ガラス基板から剥離しないゲート電極を形成する。

【解決手段】本発明では、酸素を含有する銅又は銅を主成分とした薄膜である第一の層32をガラス基板11の表面に形成し、第一の層32の表面に、酸素を含有しない銅又は銅を主成分とした薄膜をから成る第二の層33を形成し、第一の層32と第二の層33の二層構造の銅を主成分とする配線膜13を形成しており、銅を主成分とする配線膜13を窒素プラズマで処理した後、その表面に窒化ケイ素薄膜(例えばゲート絶縁膜14)を形成している。窒化ケイ素薄膜を形成する際のシランガスの影響が、ガラス基板11の界面に及ばないので、銅を主成分とする配線膜13から成るゲート電極15や蓄積容量電極12がガラス基板11から剥離しない。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】DRAMの1情報保持性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜及びゲート電極を順次形成し、前記ゲート絶縁膜及び前記ゲート電極の側部を少なくとも覆うシリコン窒化膜を形成する工程を備えた半導体装置の製造方法であって、減圧CVD法により所定の厚みのシリコン窒化物層を形成する工程と、減圧雰囲気下で前記シリコン窒化物層を窒素に暴露させる工程とを繰り返し行って、前記シリコン窒化物層を複数積層することにより、前記シリコン窒化膜を形成することを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】銅配線上に形成された導電層と銅配線との短絡や、ショートマージンの低下を防ぐ。

【解決手段】半導体装置100は、半導体基板102上に形成された絶縁膜104中に埋め込まれ、表面に複数のヒロック108が形成された下層銅配線106と、絶縁膜104および下層銅配線106上に形成された第1の層間絶縁膜112と、第1の層間絶縁膜112上に形成された第2の層間絶縁膜116と、第2の層間絶縁膜116上に形成された容量素子120とを含む。複数のヒロック108のうちの高さが最も高い少なくとも一つの上面が、第2の層間絶縁膜116の下面と接している。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁層への吸湿や絶縁層を通過する水分の配線層やビアへの悪影響を抑制でき、その結果、誘電率の上昇、配線金属の腐食、配線金属の絶縁膜中への滲みだし、リーク電流の増大等の問題のいずれかまたは全てを抑制できる半導体装置を提供する。

【解決手段】本半導体装置は、絶縁性組成物上の溝、穴または溝と穴の両方に、当該絶縁性組成物を窒化してなる窒素含有組成物とフッ素含有組成物と導体とがこの順に積層されてなる構造体を含む。

(もっと読む)

2層金属キャップを有する相互接続構造体及びその製造方法

【課題】 2層金属キャップを有する相互接続構造体を製造するための構造及び方法を提供する。

【解決手段】 1つの実施形態において、本方法は、誘電体材料層内に相互接続構造部を形成するステップ、及び、相互接続構造部の上面に2層金属キャップを形成するステップを含む。本方法は、誘電体材料層の露出面及び2層金属キャップの表面を覆う、誘電体キャップ層のブランケット層を堆積するステップを更に含む。2層金属キャップは、相互接続構造部の導電面上に形成された金属キャップ層、及び金属キャップ層の頂部に形成された金属窒化物を含む。また、誘電体層内に形成された相互接続構造部、相互接続構造部の頂部に形成された2層金属キャップ、及び、2層金属キャップを覆って形成された誘電体キャップ層を有する相互接続構造体を含む。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体ウエハ構造

【課題】コンタクト不良を防止して半導体装置の歩留まりを向上させることが可能な半導体装置の製造方法、半導体装置、及び半導体ウエハ構造を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25のうち、膜厚が基準値ΔT1よりも厚い肉厚部25xを選択的に薄くする工程と、薄くされた部分の第1絶縁膜25にコンタクトホール38c、38dを形成する工程と、コンタクトホール38c、38d内に導電性プラグ40c、40dを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

成膜方法,基板処理装置,および半導体装置

【課題】タングステンを埋め込むときのバリア層を形成する際に,チタン膜を形成し,そのチタン膜をすべて窒化して単一の窒化チタン膜をバリア層として形成することで,チタン層の変質によるタングステン膜の剥離を防止しつつ,従来よりもバリア層を薄くして,生産性を向上させる。

【解決手段】層間絶縁膜520上およびコンタクトホール530底部のシリコン含有表面512上にチタン膜を形成するチタン膜形成工程と,このチタン膜をすべて窒化し,単一の窒化チタン膜550を形成する窒化工程と,窒化チタン膜上にタングステン膜560を形成するタングステン膜形成工程とを有する。

(もっと読む)

半導体装置と半導体装置の製造方法

【課題】配線溝とスルーホール形成時の洗浄でキャップ金属が溶解して初期不良率の低下、エレクトロマイグレーション耐性の低下を防止することを目的とする。

【解決手段】上層配線開口部112の底部となる下部銅配線上に密着性を向上させるために形成されるキャップ金属の少なくとも上部のプラグと接続する部分を、科学的に安定するように変性された変性膜にすることにより、配線溝113形成後の洗浄工程においてキャップ金属の溶解を防止でき、初期不良率の低減及びエレクトロマイグレーション耐性の向上を実現することができる。

(もっと読む)

半導体装置の製造方法および製造装置、ならびに記憶媒体

【課題】銅含有金属膜の表面にSiを導入し、その部分を窒化してCuSiNバリアを形成する技術を採用する際に、層間絶縁膜へのダメージおよび大気開放による水分吸着の生じ難い半導体装置の製造方法を提供すること。

【解決手段】表面に銅含有金属膜が露出した状態の半導体基板を準備する工程と、銅含有金属膜の表面をラジカルまたは熱化学的手法により清浄化処理する工程と、銅含有金属膜の表面にSiを導入する工程と、銅含有金属膜のSiが導入された部分をラジカルにより窒化する工程とによって半導体装置を製造する際に、清浄化処理工程、Si導入工程、および窒化工程を真空を破ることなく連続的に行う。

(もっと読む)

半導体装置

【課題】メモリを有するRFIDにおいて、プロセスもしくは回路面積を増大させることなくアンテナの配置を行うことを課題とする。

【解決手段】メモリを中央に配置し、メモリ共通電極を囲むようにアンテナの配線を行う。さらに、メモリ共通電極とアンテナの距離は500μm以上、好ましくは1000μm以上離して配置する。このような構成により、メモリ共通電極とアンテナとを共通の絶縁層上に形成することが可能となり、余剰プロセスを防ぐことができる。

(もっと読む)

不均一窒化金属膜を用いる電気的接続構造物の形成方法およびこの方法によって製造された接続構造物

【課題】集積回路素子の電気的接続構造物の形成方法を提供する。

【解決手段】半導体基板100上に第1絶縁層200を形成し、第1絶縁層に開口を形成する。開口の側壁を不均一の窒素濃度を有する窒化第1金属層312でライニングする。開口の内部に導電パターン410が形成される。導電パターンと窒化第1金属層との間に第2金属窒化膜320が形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】Cu配線のCu拡散防止性能を向上する。

【解決手段】酸化シリコン膜39の上面、配線溝42の側壁部の酸化シリコン膜39の表面、配線溝42の底部の酸化シリコン膜31bの上面およびスルーホール34の側壁部の酸化シリコン膜31bの表面に、アンモニアプラズマ処理を施す。これにより、例えば厚さ10nm未満の薄い窒化シリコン膜が形成される。この結果、酸化シリコン膜39の上面、配線溝42の側壁部の酸化シリコン膜39の表面、配線溝42の底部の酸化シリコン膜31bの上面およびスルーホール34の側壁部の酸化シリコン膜31bの表面部分の膜質、清浄度、電気的な安定性を向上でき、Cuの拡散防止性能を向上させることが可能となる。

(もっと読む)

表示装置

【課題】MoあるいはMo合金から成る導電層上に塗布型絶縁膜を塗布したときに、導電層の表面に生じるMo酸化物層により発生するコンタクト不良や、膜はがれを防止する。

【解決手段】第1の基板を有し、前記第1の基板は、MoあるいはMo合金層で構成される第1導電層と、前記第1導電層よりも上層に形成される塗布型絶縁膜とを有する表示装置(例えば、液晶表示装置)であって、前記第1導電層上に形成され、AlあるいはAl合金層(または、TiあるいはTi合金層)で構成される第2導電層を有し、前記塗布型絶縁膜は、前記第2導電層上に形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】Al膜の埋め込み性を向上させた半導体装置の製造方法、及び半導体装置の製造装置に関するものである。

【解決手段】制御部が、ビアホールVHを有したシリコン基板の表面に金属膜BM1(Ti膜)と金属窒化膜BM2(TiN膜)を被覆させ、金属窒化膜BM2に被覆されたビアホールVHの内部にCVD法を用いてAl−CVD膜P1を形成させた。そして、制御部が、成膜条件データに対応する成膜条件の下で金属窒化膜BM2を被覆させ、ビアホールVHの底部に位置する金属窒化膜BM2の膜厚を基準膜厚よりも薄く形成し、かつ、ビアホールVHの上部に位置する金属窒化膜BM2の膜厚を基準膜厚よりも厚く形成させた。

(もっと読む)

ダイの裏面に接点を形成する方法

半導体素子(10,20)を形成する方法は、第1の主要表面と第2の主要表面とを有する半導体基板(12)上に第1の能動回路(14)を形成する工程を含む。第1の能動回路(14)は第1の主要表面上に形成される。第1の半導体基板内には、第1の能動回路から第1の半導体基板の第2の主要表面まで延びるビア(16,18)が形成される。第2の主要表面上には第1のビアに隣接して誘電体層(24)が形成される。誘電体層(24)は窒素とシリコンを含んでよく、低圧プラズマ、低温プラズマ、または両方のプラズマプロセスにより形成され得る。  (もっと読む)

(もっと読む)

薄膜トランジスタ基板、および表示デバイス

【課題】バリアメタル層を省略しても優れたTFT特性を発揮し得、ソース−ドレイン配線をTFTの半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極28,29とを有する薄膜トランジスタ基板において、ソース−ドレイン電極28,29は、窒素を含有する窒素含有層、または窒素及び酸素を含有する酸素窒素含有層28a、29aと、純Cu又はCu合金の薄膜28b、29bとからなっている。窒素含有層を構成する窒素の一部若しくは全部、または、酸素窒素含有層を構成する窒素または酸素の一部若しくは全部は、薄膜トランジスタの半導体層33のSiと結合している。また、純CuまたはCu合金の薄膜28b、29bは、窒素含有層または酸素窒素含有層28a、29aを介して薄膜トランジスタの半導体層33と接続している。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に開口された接続孔の内部に、チタン膜上に窒化チタン膜が形成された積層構造のバリアメタル膜を介して金属膜を埋め込んだ接続部における不具合を回避する。

【解決手段】接続孔20の底部にTiCl4ガスを用いた熱反応により熱反応Ti膜21aを形成し、TiCl4ガスを用いたプラズマ反応によりプラズマ反応Ti膜21bを形成した後、H2ガスを用いたプラズマ処理及びNH3ガスを用いたプラズマ処理を施して、プラズマ反応Ti膜21bの表面に窒素リッチTiN膜21cを形成する。続いてWF6ガスを用いたCVD法による成膜とSiH4ガスまたはB2H6ガスを用いた還元とを複数回繰り返して、窒素リッチTiN膜21c上に多層構造のタングステン核膜22aを形成した後、WF6ガス及びH2ガスを用いたCVD法により400℃以下の温度でタングステン核膜22a上にブランケット・タングステン膜22bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】タングステンを含み、小さな線幅を有する配線パターンを形成する。

【解決手段】シリコン基板11の上部に、タングステン層18を表面に有する配線層を形成するステップと、配線層上に、ハードマスク19を形成するステップと、ハードマスク19から露出する配線層の表面上に、窒化タングステン層21を形成するステップと、ハードマスク19を残したまま、窒化タングステン層21をエッチングするステップと、ハードマスク19をマスクとして配線層をエッチングし、配線パターンを形成するステップとを有する。

(もっと読む)

低抵抗コンタクト構造体及びその製造方法

【課題】 半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供すること。

【解決手段】 本発明の実施形態は、半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供する。この方法は、誘電体材料層内に少なくとも1つのコンタクト開口部を作成するステップと、化学気相堆積プロセスによって第1のTiN膜を形成するステップであって、第1のTiN膜はコンタクト開口部をライニングする(内側を覆う)ステップと、物理的気相堆積プロセスによって第2のTiN膜を形成するステップであって、第2のTiN膜は第1のTiN膜をライニングするステップとを含む。本発明の実施形態によって製造されるコンタクト構造体も提供される。

(もっと読む)

101 - 120 / 195

[ Back to top ]