Fターム[5F033QQ92]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803) | コンタクトホール部の清浄化 (522)

Fターム[5F033QQ92]に分類される特許

141 - 160 / 522

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造において、下層金属配線への接続用スルーホール内にボイドが発生することを防止する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に金属配線3を形成し、全面に層間絶縁膜4を形成する。絶縁膜内にスルーホールを形成する。スパッタエッチングにより、スルーホール開口部に傾斜部を設け断面を大きくするとともに金属配線の表面の酸化Alを除去する。半導体基板を冷却し、基板温度20℃〜40℃で、スルーホールの内面を含む全面に第1のチタン膜6、窒化チタン膜7、第2のチタン膜8、第1のAl層9aを形成する。続いて基板を加熱して第2のAl層9bをリフローしながら形成した後、第3のAl層9cを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

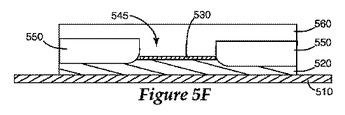

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

液晶表示装置の製造方法

【課題】一対の電極間に形成される層間絶縁膜のコンタクトホールによって露出される導

電層と電極とのコンタクト抵抗が大きくなるのを抑制することが可能な液晶表示装置の製

造方法を提供する。

【解決手段】この液晶表示装置100の製造方法では、共通電位配線17および画素電極

19を覆うように有機膜からなる層間絶縁膜20を形成する工程と、層間絶縁膜20の共

通電位配線17に対応する領域にコンタクトホール20aを形成する工程と、コンタクト

ホール20aによって露出された共通電位配線17および層間絶縁膜20の表面をエッチ

ングする工程と、共通電位配線17にコンタクトホール20aを介して接続され、層間絶

縁膜20を挟んで画素電極19と対向するように設けられる共通電極21を形成する工程

とを備える。

(もっと読む)

ギャップ充填信頼性を改良し及び容量を減少させるためのデュアル金属インターコネクト

【課題】 ギャップ充填信頼性を改良し及び容量を減少させるためのデュアル金属インターコネクトを提供する。

【解決手段】 本発明のインターコネクト形成方法は;パターン化された金属層の上に誘電層を堆積し、前記誘電層をエッチングしてトレンチ及び下置金属表面を露出するために開口部を形成し、前記前処理された開口部に、及び前記下置金属表面に直接隣接した高融点インターコネクトを形成し、前記トレンチと前記高融点インターコネクト上にバリア層とシード層を堆積し、及び前記シード層上に低抵抗金属を形成することを含む、方法である。  (もっと読む)

(もっと読む)

薄膜トランジスタ、表示装置、およびそれらの作製方法

【課題】薄膜トランジスタの電気特性の信頼性を高めることが可能な薄膜トランジスタ及びその作製方法を提供する。また、画質を向上させることが可能な表示装置及びその作製方法を提供する。

【解決手段】また、ゲート電極と、ゲート電極上に形成されるゲート絶縁層と、ゲート電極に重畳し、且つゲート絶縁層上に形成される酸化物半導体層と、ゲート絶縁層及び酸化物半導体層上に形成される配線と、酸化物半導体層及び配線に接する有機樹脂層とを有する薄膜トランジスタである。

(もっと読む)

半導体装置の配線構造物及びその形成方法

【課題】後工程における、キャパシタの下部電極と接続されるべき第2コンタクトプラグの形成の際の洗浄液による第1コンタクトパッドの損傷を防止できる、半導体装置の配線構造物及びその形成方法を提供する。

【解決手段】配線構造物は、第1コンタクトパッド126、第1コンタクトプラグ150、スペーサー140、及び層間絶縁膜パターン120、130を含む。第1コンタクトパッド126は、基板100の第1コンタクト領域116aと電気的に接続される。第1コンタクトプラグ150は、第1コンタクトパッド126上に具備され、第1コンタクトパッド126と電気的に接続される。スペーサー140は、第1コンタクトプラグ150の側壁と第1コンタクトパッド126の側壁の上部とに同時に面接する。層間絶縁膜パターン120,130は、コンタクトパッド126とスペーサー140を収容する開口を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】ビア又は接着層とカルコゲナイド膜とのコンタクト性を確保しつつ、量産性を向上させることができる半導体装置及びその製造方法を提供すること。

【解決手段】層間絶縁膜3にビア2を形成する第1の工程と、層間絶縁膜3上のビア2の周囲の領域に接着層5を形成する第2の工程と、ビア2及び接着層5の表面にできた酸化物を、フッ化還元ガス雰囲気中に晒して還元する第3の工程と、ビア2及び接着層5の表面にできたフッ化物を、アンモニアガスを用いて除去する第4の工程と、ビア2及び接着層7を含む層間絶縁膜3上に、スパッタ法により相変化材料膜4を形成する第5の工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】銅を主成分とするコンタクトプラグを有する半導体装置において、コンタクトプラグに隆起が発生することを防止する。

【解決手段】第1の層間絶縁膜102に、金属シリサイド層101に到達するコンタクトホール103を形成する工程(c)と、コンタクトホールの底面及び側壁に、高融点金属膜104を形成する工程(d)と、高融点金属膜上に、銅を主成分とする金属膜106Aを形成し、コンタクトホール内に、高融点金属膜を介して、金属膜が埋め込まれてなるコンタクトプラグ107を形成する工程(e)と、第1の層間絶縁膜及びコンタクトプラグの上に、第2の層間絶縁膜108を形成する工程(f)とを備え、工程(f)は、コンタクトプラグの表面に存在する酸素ガスを除去する工程(f1)と、工程(f1)の後に、コンタクトプラグの表面に存在する酸素ガスが除去された状態で、第2の層間絶縁膜を形成する工程(f2)とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体装置とその製造方法

【課題】キャパシタを備えた半導体装置とその製造方法において、キャパシタの品質を向上させること。

【解決手段】第1の導電膜19、誘電体膜20、及び第2の導電膜21をこの順に形成する工程と、第2の導電膜21をパターニングして、複数の上部電極21aを形成する工程と、レジストパターン27の側面27bが後退するエッチング条件を用いて、該レジストパターン27をマスクにしながら誘電体膜20をエッチングし、キャパシタ誘電体膜20aを形成する工程と、第1の導電膜19をパターニングして下部電極19aを形成する工程と、上部電極19aの上の層間絶縁膜33にホール33aを形成する工程と、ホール33aに導体プラグ37を埋め込む工程とを有し、端部の上部電極21a上のホール37の形成予定領域が、側面27bが後退した後のレジストパターン27により覆われる半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】エッチング工程で生成される反応生成物による配線信頼性の低下を防ぐ半導体装置の製造方法を提供する。

【解決手段】電極の側壁にスペーサを有する半導体装置の製造方法であって、電極を覆う絶縁膜を形成する工程と、電極の側壁にスペーサを形成するために絶縁膜にドライエッチングを行う工程と、水素単体ガスまたは窒素を含むガスによるプラズマ放電により、ドライエッチングにより生じた反応生成物を除去する工程と、反応生成物を除去した後、少なくとも絶縁膜にオーバーエッチングを行う工程とを有するものである。

(もっと読む)

半導体装置の製造方法

【課題】ポリマー残渣の発生と、エッチングプロセスの変動を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】Low−k膜II2の上面に、パターニングされたハードマスク層HMが形成される。ハードマスク層HMをマスクとしてLow−k膜II2にエッチングが施されてLow−k膜II2に配線用溝TRが形成される。配線用溝TR形成のためのエッチングを行なったチャンバーと同じチャンバー内でハードマスク層HMが除去されてLow−k膜II2の上面が露出される。

(もっと読む)

半導体装置の製造方法

【課題】接合リーク電流の低減が図られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に所定の深さのトレンチが形成され、そのトレンチ5内に分離酸化膜6が形成される。不純物イオンを注入することにより、分離酸化膜6の表面に、分離酸化膜6のエッチング特性とは異なるエッチング特性を有する改質層7が形成される。半導体基板の領域に、トランジスタ等の所定の半導体素子が形成される。半導体基板1上に、エッチングストッパ膜10および層間絶縁膜16が形成される。その層間絶縁膜16およびエッチングストッパ膜に、金属シリサイド9の表面を露出するコンタクトホール16a,16bが形成される。コンタクトホール16a,16b内にプラグ18a,18bが形成される。

(もっと読む)

インダクタの金属配線形成方法

【課題】UTM反応性イオンエッチングで発生するポリマーを除去するのに好適なインダクタの金属配線形成方法を提供する。

【解決手段】半導体素子製造において、特にRF(Radio Frequency)素子に用いられるインダクタの金属配線を形成する方法に関するもので、ポリマーとの反応性に優れたラジカルを用いて、トレンチ形成のためのエッチング時に発生したポリマーを効果的に除去する目的として、トレンチを形成するための第1のメインエッチング段階と、該第1のメインエッチングで発生したポリマーを除去するアッシュ段階と、トレンチの底面にビアを形成するための第2のメインエッチング段階と、を含む。

(もっと読む)

141 - 160 / 522

[ Back to top ]