Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

2,041 - 2,060 / 5,243

半導体装置

【課題】大型絶縁基板に非単結晶Si半導体素子と単結晶Si半導体素子とを形成し、高性能なシステムを集積化した半導体装置を製造する場合に、単結晶Si部分の製造工程を簡略化し、かつ大型絶縁基板に転写した後、高精度のフォトリソグラフィなしに微細な単結晶Si半導体素子の素子分離を実現し得る半導体基板、半導体装置、及びそれらの製造方法を提供する。

【解決手段】チャネル領域17、ソース領域4及びドレイン領域5を含む活性層6を有し、ウエル構造及びチャネルストップ領域を有しない単結晶Siウエハ8と、単結晶Siウエハ8上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極2と、活性層6の周囲の単結晶Siウエハ8上に形成された、ゲート絶縁膜3よりも膜厚の厚いLOCOS酸化膜7と、ゲート電極2及びLOCOS酸化膜7上に形成された平坦化絶縁膜1を有する。

(もっと読む)

半導体装置

【課題】MEMS構造体に対して外部空間からの圧力や振動信号を直接受信できるように構成し、かつ、MEMS構造体と集積回路とを形成した半導体チップをバンプ電極でモジュール基板にフェイスダウン実装することにより、小型化を実現できる技術を提供する。

【解決手段】半導体基板1の一方の面に集積回路が形成され、半導体基板1の他方の面にMEMS構造体が形成されている。そして、集積回路上に形成されているバンプ電極BPによって実装基板にフリップチップ接続する構造となっている。このとき、トランスデューサは外部空間に向いた状態で配置できる。このため、トランスデューサが外部空間と直接対話する機能を損なうことなく、半導体装置を小型化することができる。なお、集積回路とMEMS構造体とは半導体基板1を貫通する貫通電極20a、20bにより電気的に接続される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ワイヤボンディングで実装されるチップとバンプ電極で実装されるチップとで、製造工程を共通化できる技術を提供する。

【解決手段】バンプ電極によりチップ1が外部との電気的接続を行う場合においても、ボンディングワイヤによりチップ1が外部との電気的接続を行う場合においても、1本の最上層の配線7にバンプ接続部15およびボンディングパッド16の両方を設ける。バンプ電極を用いる場合にはバンプ接続部15上の絶縁膜に開口部を設け、ボンディングパッド16上は絶縁膜で覆う。一方、ボンディングワイヤを用いる場合にはボンディングパッド16上の絶縁膜に開口部を設け、バンプ接続部15上は絶縁膜で覆う。

(もっと読む)

半導体装置およびその製造方法

【課題】ストレスライナー膜の形成を適切に実施できる半導体装置およびその製造方法を提供する。

【解決手段】シリコン窒化膜110は、PMOS領域100pおよびNMOS領域100nにおいて、サイドウォールとしてのシリコン窒化膜106の両側壁に形成され(第1のストレスライナー膜)、シリコン窒化膜112は、NMOS領域100nにおいて、フルシリサイドゲート電極103およびシリコン窒化膜106,110を覆うように形成される(第2のストレスライナー膜)。

(もっと読む)

パッド電極の開口方法および固体撮像素子の製造方法、固体撮像素子および電子情報機器

【課題】パッド電極にかかるオーバーエッチング量を抑制して、後のシンター処理で発生するパッド電極上のAl空洞化によるパッシベーション膜の膜剥がれを低減してパッド電極のボンディング不良を抑える。

【解決手段】パッド電極上の酸化膜、前述した絶縁膜5をウェットエッチングでパッド電極上のみ取り除き、パッド電極のTi系バリアメタル層3のみをドライエッチングで除去することにより、パッド電極のメタル層4に与えるドライエッチングのオーバーエッチによるダメージを大幅に抑える。

(もっと読む)

半導体装置およびその製造方法

【課題】アライメントマークの視認性を向上することにより、半導体チップと実装基板との位置合わせを高精度に行なうことができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップにおいて、半導体基板1S上のアライメントマーク形成領域にマークMK1を形成する。このマークMK1は、集積回路形成領域の最上層配線(第3層配線L3)と同層で形成されている。そして、マークMK1およびマークMK1を囲む背景領域の下層にパターンP1a、P1b、P2、P3を形成する。このとき、パターンP1aは第2層配線L2と同層で形成されており、パターンP1bは、第1層配線L1と同層で形成されている。さらに、パターンP2は、ゲート電極Gと同層で形成されており、パターンP3は素子分離領域STIと同層で形成される。

(もっと読む)

半導体パッケージおよびその製造方法

【課題】半導体素子の性能劣化を引き起こすことなく、小型化が可能かつ高信頼性を有する安価なウエハレベルCSPの半導体パッケージを提供する。

【解決手段】半導体パッケージ100であって、半導体基板の第1の面に配置された電極パッド106と、前記半導体基板の第2の面から該電極パッドが露出するように、該電極パッド直下の該半導体基板内に開けられた貫通孔と、前記半導体基板の第2の面と該貫通孔の内側面とを覆い、前記電極パッドが露出するように配置された電気絶縁膜と、該電気絶縁膜を介して、前記貫通孔の内側面及び前記電極パッドの露出部を覆うように配置され、該電極パッドと電気的に接続された金属薄膜からなる貫通電極108と、該貫通電極と前記半導体基板の第2の面101bに設けられた外部配線領域とを接続するために貫通電極から延長された外部配線109と、該外部配線領域に外部端子と接続するための接続部111と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】アスペクト比10以上のコンタクトホール形成に際して、デポ物の除去効率を高める半導体装置の製造方法を提供する。

【解決手段】コンタクトホールのホールエッチング後、フルオロカーボン系ガスと酸素を酸素過多で含む処理ガスでバイアス無印加の条件でライトエッチングし、ホール3側壁に付着するC−F結合を有する反応生成物5をプラズマ処理で除去し、その後WET処理によりホール底に残存するデポ物4を除去してから、ホール内に導電材料を埋め込みコンタクトプラグ7を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】複数枚のウエハを貼り合わせる際に、電気信号接続部に発生する損傷を効果的に防止することができ、信頼性に優れ、安定した性能の得られる半導体装置を提供する。

【解決手段】各ウエハ1WA,1WBにおける別のウエハとの貼り合わせ面30a、30bには電気信号接続部9、26が設けられ、電気信号接続部と、対向する別のウエハに設けられた電気信号接続部とが電気的に接続され、対向する電気信号接続部9、26同士のうちの少なくとも一方が、貼り合わせ面30a、30bから突出して形成された凸状接続部であり、前記凸状接続部の形成されている貼り合わせ面30a、30b上における電気信号接続部9、26の配置されていない領域に、前記半導体回路と絶縁され、前記凸状接続部と同じ高さ又は前記凸状接続部よりも高い高さで前記貼り合わせ面30a、30bから突出する補強凸部5b、9b、26bが形成されている半導体装置とする。

(もっと読む)

ケイ素含有膜形成用組成物、ケイ素含有膜の形成方法、およびケイ素含有膜

【課題】高集積化および多層化が望まれている半導体素子などにおいて好適に用いることができ、機械的強度に優れ、低比誘電率でかつ吸湿性が低く、加工耐性が高い膜を形成することができるケイ素含有膜形成用組成物、上記組成物を用いるケイ素含有膜の形成方法、および上記形成方法によって得られるケイ素含有膜を提供する。

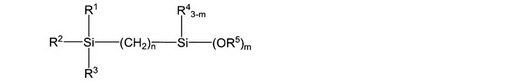

【解決手段】ケイ素含有膜形成用組成物は、下記一般式(1)で表される有機シラン化合物と、空孔形成剤とを含む。

【化1】

・・・・・(1)

(式中、R1〜R4は、同一または異なり、水素原子、炭素数1〜4のアルキル基、ビニル基、またはフェニル基を示し、R5は炭素数1〜4のアルキル基、アセチル基、またはフェニル基を示し、nは1〜3の整数を示し、mは1〜2の整数を示す。)

(もっと読む)

半導体装置の製造方法

【課題】ビアファースト方法を用いるデュアルダマシン配線の形成において、レジストポイズニングを抑制する。

【解決手段】半導体装置の製造方法は、基板101上に層間絶縁膜108を形成する工程(a)と、層間絶縁膜108にビアホール109を形成する工程(b)と、ビアホール109内にダミープラグ111を形成する工程(c)と、工程(c)の後、層間絶縁膜108上に第1のバリア絶縁膜120を形成し、更にその上に反射防止膜105を形成するする工程(d)と、第1のバリア絶縁膜120上に、配線溝形成用開口114を有するレジストマスク113を形成する工程(e)と、レジストマスク113をマスクとして層間絶縁膜108、第1のバリア絶縁膜120及びダミープラグ111のそれぞれ一部を除去することにより、ダミープラグ111の残存部分に接続する配線溝を形成する工程(f)とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】WPP技術における再配線を有する半導体装置の信頼性を向上させる。

【解決手段】再配線が半導体基板1Sの面内において互いに電気的に分離された本体パターン2およびダミーパターン3を有している。多層配線と電気的に接続された本体パターン2と、フローティングされたダミーパターン3とが、半導体基板1Sの面内で混在して設けられている。半導体基板1Sの面内における本体パターン2およびダミーパターン3を合わせた占有率、すなわち再配線の占有率が35%以上60%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】Nチャネル領域内、およびPチャネル領域内のチャネルに印加するストレスを制御でき、面積の増加抑制および歩留まりの低下を実現できる半導体装置およびその製造方法を提供する。

【解決手段】Nチャネル領域201内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断する。Pチャネル領域202内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断後、酸素などをイオン注入する。その後、熱処理を加えてNチャネル領域201内のコンタクトライナー513を収縮させてnチャネルコンタクトライナー518を形成し、Pチャネル領域202内のコンタクトライナー513を膨張させてpチャネルコンタクトライナー519を形成する。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたSiおよび/またはGe:0.1〜1.5 原子%、Niおよび/またはCo:0.1〜3.0原子%、Laおよび/またはNd:0.1〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】バリア膜を薄くする場合であっても良好なバリア性を確保し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の導電体32と、半導体基板上及び第1の導電体上に形成され、第1の導電体に達するコンタクトホール52と、コンタクトホールの上部に接続された溝54とが形成された、酸素を含む絶縁膜48と、コンタクトホールの側面並びに溝の側面及び底面に形成された酸化ジルコニウム膜62と、コンタクトホール内及び溝内における酸化ジルコニウム膜上に形成されたジルコニウム膜64と、コンタクトホール内及び溝内に埋め込まれたCuより第2の導電体70とを有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】複数枚のウエハを貼り合わせる際に、電気信号接続部に発生する損傷を効果的に防止することができ、信頼性に優れ、安定した性能の得られる半導体装置を提供する。

【解決手段】素子の形成された基板1SA,1SBからなる複数枚のウエハ1WA,1WBが貼り合わされてなり、各ウエハ1WA,1WBにおける別のウエハとの貼り合わせ面30a、30bには電気信号接続部9、26が設けられ、対向する電気信号接続部9、26同士のうちの少なくとも一方が、基板1SAが露出されている貼り合わせ面30aから突出して形成された凸状接続部であり、凸状接続部の形成されている貼り合わせ面30a上における前記電気信号接続部の配置されていない領域に、基板1SAと同じ材料からなり、半導体回路と絶縁され、貼り合わされたウエハ1WA,1WB間の間隔の寸法と同じ高さで貼り合わせ面30aから突出する補強凸部52が形成されている半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の半導体チップを多段に積層した半導体装置において、ワイヤボンディング工程におけるチップクラックを防いで製造歩留まりを向上させることのできる技術を提供する。

【解決手段】下段チップ3Dのボンディングワイヤ11が接続されない未接続パッド電極10N上に、ダミーバンプ16を形成する。これにより、下段チップ3Dの未接続パッド電極10Nの上に位置する上段チップ3Uのパッド電極10にボンディングワイヤ11を接続する際、下段チップ3Dの未接続パッド電極10N上に形成されたダミーバンプ16が上段チップ3Uの支えとなって上段チップ3Uのたわみを低減し、上段チップ3Uのパッド電極10に生じるクラックを防ぐことができる。

(もっと読む)

半導体装置

【課題】配線の幅広配線部から突出した凸状配線部に形成されたビアについて、ストレスマイグレーション耐性を向上し得る半導体装置を提供する。

【解決手段】第1の配線18と、第1の配線18の上方に形成され、第1の配線18に接続されたビア38を一体的に有する第2の配線34と、ビア38に隣接して配置され、ビア38と同層に形成された複数のダミービア40a、40b、40c、40dとを有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】素子分離部への凹部の形成やエッチング残りなどの問題を生じることなく、NMOS形成領域およびPMOS形成領域にそれぞれ引張り応力膜および圧縮応力膜を選択的に形成することができる、半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体層4上に、NMOS形成領域7を選択的に露出させる第1開口28を有する第1マスク26が形成され、引張り応力膜23が形成された後、第1マスク26が、第1マスク26上に形成された引張り応力膜23とともに除去される。また、半導体層4上に、PMOS形成領域6を選択的に露出させる第2開口29を有する第2マスク27が形成され、圧縮応力膜22が形成された後、第2マスク27が、第2マスク27上に形成された圧縮応力膜22とともに除去される。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留りが高く且つ配線間容量を十分に低減でき、且つ機械的強度を十分に得られるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の配線105と、第1の層間絶縁膜101に複数の配線105の少なくとも1つと接続するように形成されたビア113及びダミービア106とを有している。第1の層間絶縁膜101における互いに隣り合う配線105同士の間には空隙部109が選択的に形成されており、ダミービア106は、空隙部109と接する配線105Aの下側に該配線105Aと接続して形成され、ビア113及びダミービア106は、空隙部109を介することなく第1の層間絶縁膜101により周囲を覆われている。

(もっと読む)

2,041 - 2,060 / 5,243

[ Back to top ]