Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

2,081 - 2,100 / 5,243

半導体装置の製造方法

【課題】信頼性や製造歩留まりを向上し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10の第1の主面上に、ゲート電極24とソース/ドレイン拡散層32とを有するトランジスタ33を形成する工程と、半導体基板の第1の主面上及びトランジスタ上に第1の絶縁膜38を形成する工程と、第1の絶縁膜に、ゲート電極に達するコンタクトホール40を形成する工程と、コンタクトホール内及び第1の絶縁膜上に、プラズマCVD法により導電膜42,44を形成する工程と、第1の絶縁膜の表面が露出するまで導電膜を研磨し、コンタクトホール内に、導電膜を含む導体プラグ44を埋め込む工程とを有し、導電膜を形成する工程の前に、第1の主面の反対側の面である第2の主面に存在する第2の絶縁膜29のうち、第2の主面の周縁部に存在する第2の絶縁膜をエッチング除去する工程を更に有している。

(もっと読む)

半導体装置の製造方法

【課題】レジストマスクを用いたフォトリソ工程を追加することなく、微細な容量コンタクトプラグ上部の面積を拡大させることが可能なCOB型DRAMの製造方法を提供する。

【解決手段】製造方法は、層間膜8にコンタクトホールを形成後、コンタクトホールに第一の導電材料を埋め込みエッチバックして、第一のコンタクトプラグ10を形成する工程、層間膜8をエッチングして第一のコンタクトプラグ10上部を露出させる工程、及び、層間膜8及び第一のコンタクトプラグ10上に第二の導電材料を成膜しエッチバックして、自己整合的に第一のコンタクトプラグ10上部周囲に第二の導電材料11を残すことで、プラグ10上部を拡大した第二のコンタクトプラグを形成する工程、とを有する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を増大させることなく、酸化銅の成長を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】半導体装置10は、電極12が設けられた主面に、絶縁層13、銅薄膜14、銅再配線(配線)15、酸化銅16、塩基性炭酸銅(保護膜)17、及び、樹脂絶縁層18が順次形成されており、酸化銅16の界面を、二酸化炭素の濃度制御によりpH値が6≦pH<7に制御された炭酸水に浸漬させることで、炭酸銅CuCO3及び水酸化銅Cu(OH)2の復塩である塩基性炭酸銅17を形成する工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】減圧状態の空洞を有する半導体装置の簡易な製造方法を提供すること。

【解決手段】本発明にかかる半導体装置の製造方法は、半導体基板10の上方に絶縁層20を形成する工程と、絶縁層20をエッチングして孔部22を形成する工程と、絶縁層20の上方に接着層30を形成する工程と、水素ガスおよびヘリウムガスの少なくとも一方の雰囲気中で、孔部22を密閉するように、接着層30の上方に封止板40を積層する工程と、半導体基板10を減圧雰囲気中で加熱する工程と、を有する。

(もっと読む)

半導体装置、その製造方法及び感光性樹脂組成物

【課題】有機絶縁膜を被覆した無機絶縁膜のエッチング時にエッチング残渣が生成しない半導体装置、その製造方法及び当該製造方法に使用する感光性樹脂組成物を提供する。

【解決手段】半導体装置の製造方法は、半導体素子1上に形成された少なくともパッド電極2及び金属配線上に無機絶縁膜3を形成する工程と、前記無機絶縁膜3上に有機絶縁膜4であるフッ素非含有有機絶縁膜を形成する工程と、前記フッ素非含有有機絶縁膜をパターン加工する工程と、前記パターン加工により露出された前記無機絶縁膜3をフッ素含有ガスによりドライエッチングして前記パッド電極2を露出させる工程とを含む。

(もっと読む)

半導体装置

【課題】静電保護素子のクランプ能力を十分に発揮し、内部回路を静電気によるサージから保護することができる半導体装置を提供することを目的とする。

【解決手段】半導体基板上に、内部回路と、前記内部回路と接続配線及び接地配線により接続される接続パッド及び接地パッドと、前記接続パッドと前記接地パッドとの間に接続される静電保護素子とが設けられ、前記半導体基板と前記接地配線とが、前記接地配線に所定の密度で形成されたコンタクトにより電気的に接続されている半導体装置であって、前記所定の密度は、前記接続パッドから前記静電保護素子を経由して前記接地パッドに至る部分のインピーダンスが、前記接続パッドから前記内部回路を経由して前記接地パッドに至る部分のインピーダンスよりも低くなるように設定されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 CSPと呼ばれる半導体装置の製造方法において、柱状電極形成用メッキレジスト膜の剥離時間を短縮する。

【解決手段】 柱状電極形成用露光マスク26は、柱状電極形成領域に対応する部分を遮光部26aとされ、遮光部26aの周囲を透過部26bとされ、それ以外の領域を半透過部26cとされたものからなっている。露光を行なうと、柱状電極形成用メッキレジスト膜25のうち、遮光部26aに対応する領域が非露光部となり、その周囲が露光部となり、それ以外の領域が半露光部となる。現像を行なうと、柱状電極形成用メッキレジスト膜25のうち、非露光部である柱状電極形成領域に対応する部分に開口部が形成され、開口部の周囲部以外であって半露光部である領域における厚さが開口部の周囲部の厚さのほぼ半分程度と薄くなる。これにより、柱状電極形成用メッキレジスト膜25の剥離時間を短縮することができる。

(もっと読む)

パワーMOSトランジスタ

【課題】 エレクトロマイグレーションの制約を受け難く、配線抵抗が小さくトランジスタの電力損失が少ない、パッド配置の制約の少ないパワーMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成されたソース領域2およびドレイン領域3が格子状に形成されたゲート4を挟んで互いに隣接するMOSトランジスタにおいて、半導体基板1上に順次形成された3層のメタル配線5、6、7とを有する。メタル配線は、ソース領域及びドレイン領域に電気的に接続され、ドレイン領域を第3層メタル配線7に接続する場合、ソース領域を第2層メタル配線6及び第1層メタル配線5に接続する。第3層メタル配線7のドレイン配線は、半導体基板1の全領域を覆うように配置され、第1層及び第2層メタル配線5、6のソース配線は第1層及び第2層メタル配線の全領域を覆うように配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】ビット線間の間隔が狭くなった場合の配線間ショートに対するマージンや耐圧を確保する。

【解決手段】隣接配置される選択ゲートトランジスタのコンタクトプラグを、第1および第2のコンタクトプラグ4、5として交互に配置した構成とし、配線層を2層にして下層側を第1の配線層6、上層を第2の配線層7として形成する。第1のコンタクトプラグ4を第1の配線層6にヴィアプラグ13を介して接続し、第2のコンタクトプラグ5をヴィアプラグ13、16を介して第2の配線層7に接続する構成とする。第1の配線層6、第2の配線層7が共にコンタクトプラグのピッチの倍のピッチで配置できる。ショート不良、耐圧不良、リーク不良、配線間容量の増大を防止できる。

(もっと読む)

中間材と関連構成部品とを有する集積回路構成

【課題】集積回路の電気的性質、特に耐用年数もしくは信頼性が向上するのに好適なビアライナと導電通路ライナとが接触した集積回路を提供する。

【解決手段】特に、ビアライナ28と導電通路ライナ20とが接触した集積回路。ビアライナ28は、接続部分中間材であって、いずれの場合にも、接続部分と該接続部分誘電体の間および/または接続部分とインターコネクトとの間に配置される材料である。導電通路ライナ20は、電気的に導電性を有するインターコネクト中間材であって、いずれの場合にも、インターコネクトの側面とインターコネクト誘電体との間に配置される材料である。インターコネクト中間材と接続部分中間材は少なくとも1つの接続において接触する。これにより、集積回路10の電気的性質、特に耐用年数もしくは信頼性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたセル構造などの半導体装置において、容量コンタクトの接触抵抗を増大させることなく、ビットコンタクトと容量コンタクトのように2つの高さの異なるコンタクトが近接する場合に、その目合わせずれによるショートを防止する構造及びその製造方法を提供する。

【解決手段】少なくとも1層の層間膜3を共有し、少なくとも第1のコンタクト4と該第1のコンタクトよりも高い第2のコンタクト6が近接して配置された半導体装置において、前記第1のコンタクト4の上面が該第1のコンタクトの形成される層間膜3に対しリセス構造を成し、該リセス内に前記第1のコンタクトの上面からリセス側壁にかけてシリコン窒化膜サイドウォール9を有することを特徴とする。

(もっと読む)

被覆パターン形成方法およびパターン形成方法

【課題】CVDを使用することなく、被覆されたパターンを形成することが可能な被覆パターン形成方法およびこれを利用してより高密度なパターンを形成するパターン形成方法を提供する。

【解決手段】パターン2を有する熱伝導性基板1に熱重合性組成物を塗布して塗膜3を形成したのち、ベークおよび現像をして被覆パターン7を形成する。このようにして形成された被覆パターン上に無機性組成物膜を形成したのち、エッチングすることによって、より高密度なパターンを形成することができる。

(もっと読む)

相互接続構造のための貴金属キャップおよびこれを形成する方法(相互接続構造のための貴金属キャップ)

【課題】 誘電率が約3.0以下の誘電材料(52)を含む相互接続構造を提供する。

【解決手段】 この低k誘電材料は、上面が埋め込まれた少なくとも1つの導電材料(60)を有する。また、誘電材料は、貴金属キャップ(62)の形成前に疎水性とされた表面層(52B)を有する。貴金属キャップは、少なくとも1つの導電材料の上面上に直接に配置されている。誘電材料上に疎水性表面層が存在するために、貴金属キャップは、少なくとも1つの導電材料に隣接した誘電材料の疎水性表面層上に実質的に延出せず、この疎水性の誘電表面上に貴金属キャップ堆積からの貴金属残留物は存在しない。

(もっと読む)

多孔質絶縁膜及びその形成方法並びに半導体装置の製造方法

【課題】 炭化水素含有の多孔質層間絶縁膜を用いた多層配線では、低エネルギプラズマによる放電不安定性と隣接膜との密着性劣化により、低誘電率化と高信頼化を両立することが困難であった。

【解決手段】 本発明の多孔質絶縁膜10は、有機シロキサンを原料とするプラズマCVDによって形成されたものにおいて、第一の電子エネルギのプラズマを用いてプラズマCVDによって形成された第一層11と、第一層11の上に第二の電子エネルギのプラズマを用いて前記プラズマCVDによって形成された第二層12とを備え、第一の電子エネルギが第二の電子エネルギよりも大きい、ことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の電気的特性のばらつきを低減することにより、半導体素子の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】半導体基板1上にニッケル−白金合金膜を形成した後、熱処理温度が210〜310℃の1回目の熱処理をヒータ加熱装置で行うことで、ニッケル−白金合金膜とシリコンとを反応させて(PtNi)2Si相の白金添加ニッケルシリサイド層33を形成する。続いて未反応のニッケル−白金合金膜を除去した後、1回目の熱処理よりも熱処理温度が高い2回目の熱処理を行い、PtNiSi相の白金添加ニッケルシリサイド層33を形成する。1回目の熱処理の昇温速度は10℃/秒以上(例えば30〜250℃/秒)とし、2回目の熱処理の昇温速度は10℃/秒以上(例えば10〜250℃/秒)とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体装置の製造方法および半導体ウエハ洗浄装置

【課題】カロー酸を用いたウエハ(基板)洗浄工程において、H2O2の使用量を低減しつつ、フォトレジスト膜(感光性マスキング層)の除去性を向上できる技術を提供する。

【解決手段】基板1の洗浄(フォトレジスト膜の除去)時以外のSPM液中のH2O2の濃度は、フォトレジスト膜の少なくとも一部を除去できる最低限の第1濃度以上で制御する。そして、基板1をSPM槽51(内槽51A)へ浸漬する直前に、SPM液中のH2O2の濃度がフォトレジスト膜を確実に除去できる第2濃度以上となり、また基板1をSPM槽51(内槽51A)へ浸漬した時にSPM液中のH2O2の濃度がその第2濃度未満とならないように、過酸化水素水供給系54からSPM槽51(内槽51A)へ所定量のH2O2を供給する。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクト孔形状の改善することで配線材料のカバレージの向上を計り、配線材料の第1導電型半導体基板への拡散によるリーク電流の防止を図る。

【解決手段】 第1導電型半導体基板に形成されている第2導電型高濃度拡散層と配線材料を接合させるコンタクト孔を具備し、コンタクト孔形成後にバリアメタル膜と配線材料を堆積後パターニングされていることを特徴とする半導体装置において、第2導電型高濃度拡散層と配線材料の接触面近傍において、単層の絶縁膜あるいは熱膨張係数が同程度の複層の絶縁膜を形成させることで、配線材料カバレージ向上、およびバリアメタル膜の劣化を抑制することで、配線材料の第1導電型半導体基板に拡散することを防止しリーク電流を防止する。

(もっと読む)

優勢エッチング抵抗性を具備する低K誘電バリアを得る方法

【課題】低い誘電率、向上したエッチング抵抗性、優れたバリア特性を設けた誘電バリアを形成する方法を提供する。

【解決手段】半導体基板を処理する方法を提供し、この方法は、ケイ素−炭素結合および炭素−炭素結合を備える前駆物質を処理チャンバへ流すステップと、半導体基板上に炭素−炭素結合を有する誘電バリア膜を形成するために、処理チャンバ内において前駆物質の低密度プラズマを生成するステップであって、この前駆物質中の炭素−炭素結合の少なくとも一部は低密度プラズマ中に保存されかつ誘電膜内に組み込まれるステップと、を備える。

(もっと読む)

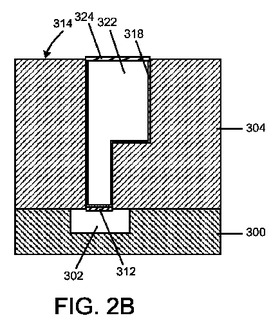

半導体デバイスのCuメタライゼーションへ選択的低温Ru堆積を統合する方法

半導体デバイスの製造に選択的低温Ru堆積を統合することで、バルクCu金属中でのエレクトロマイグレーション及びストレスマイグレーションを改善する方法。当該方法は、誘電体層(304)中に凹部を有するパターニング基板を供する工程であって、前記凹部は平坦化されたバルクCu金属(322)によって少なくとも実質的に充填されている工程、H2、N2、若しくはNH3、又はこれらの混合気体が存在する中で前記バルクCu金属及び前記誘電体膜を熱処理する工程、並びに、前記の熱処理されたバルクCu金属上にRu金属膜を選択的に堆積する工程、を有する。  (もっと読む)

(もっと読む)

2,081 - 2,100 / 5,243

[ Back to top ]