Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

1,961 - 1,980 / 5,243

半導体集積回路装置の製造方法

【課題】銅ダマシン関連のバック・エンド領域におけるエッチング装置等の運用に関して、無駄時間が発生していることが明らかとなった。すなわち、たとえば、銅ダマシン配線における層間膜のドライ・エッチング工程においては、5分に1度程度の高頻度でステージ温度の切り替えが発生していることが明らかとなった。これは、ドライ・エッチングのステージ温度等のデータが製造実行システムに登録されていないために、ロット優先度の高いロットが仕掛となるたびに、高頻度でステージ温度の切り替えが発生しているからである。

【解決手段】本願発明は、エッチング・ステージ温度等のように、条件変更に比較的長い準備時間を要する処理条件を製造実行システムに登録しておくことによって、効率のよいウエハ・プロセスの進行管理を実現するものである。

(もっと読む)

パッドと半導体装置の製造方法

【課題】パッドと半導体装置の製造方法において、パッドの配置密度を向上させると共に、電気的試験で使用されるプローブによってパシベーション膜が欠損するのを防止する手段の提供。

【解決手段】開口面以外がパシベーション膜40、41で覆われたパッド37bにおいて、半導体装置に設けられた三角形状又は台形状の第1の金属膜37xと、第1の金属膜37x上であって、パッド37bの開口面の一部分に開口41aの側面と接するように形成された第2の金属膜37yとを備えたパッドとする。

(もっと読む)

コンタクトホールの形成方法、パターン形成方法、及び電気光学装置の製造方法

【課題】エッチング時におけるホール径が小さく、アスペクト比が高い場合においても、テーパ角を良好にコントロール可能なコンタクトホールの形成方法、パターン形成方法、及び電気光学装置の製造方法を提供する。

【解決手段】基材1上に形成された膜2上に金属膜3を形成する。そして、金属膜3上にレジストマスク4を形成する。このレジストマスク4を用い、金属膜3をドライエッチングするとともに、ドライエッチングによるレジストマスク4の後退量を制御して、開口側面5aが膜に対して第1の傾斜角度を有する金属マスク5を形成する。第1の傾斜角度を有する金属マスク5を用いて膜をドライエッチングすることで、基材1の表面に形成された導電部6を露出させるとともに、開口側面5aが導電部6に対して第1の傾斜角度に応じた第2の傾斜角度を有する孔を形成する。そして、金属マスク5を除去するコンタクトホールの形成方法である。

(もっと読む)

ドライエッチング終点検出方法

【課題】コンタクトのホール加工等におけるドライエッチングにおいて、エッチング対象のパターン占有率が微小であっても、エッチング終点を安定して検出することができる技術を提供する。

【解決手段】ドライエッチング終点検出方法であって、コンタクトホール等のドライエッチング工程において、プラズマ発光のスペクトル分析を利用するものである。そして、2波長の発光強度比の時系列データを二次微分演算して第2変極点(just2)402でエッチング終点を検知することにより、エッチング終点検出の安定化を達成する。また、異常放電を同時に検出することにより、外乱を排除し、エッチング終点検出の安定化を達成する。

(もっと読む)

スパッタリング装置および金属化構造体を製造する方法

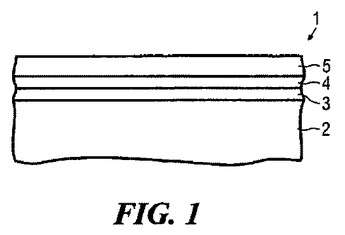

複数のパルスで陽極とターゲット間に電力を印加することによってTaN層(4)を被着し、ターゲットから基板(2)へ反応的にTaをスパッタしてTaNシード層(4)を形成する方法から成る。Ta層(5)は複数のパルスにおける電力を印加すると共に、前記基板(2)を支持するペデスタルに高い周波数信号を印加することによって前記TaNシード層(4)の上に被着され、前記基板(2)に隣接した自己バイアス場を生成する金属化構造体(1)を被着する方法。  (もっと読む)

(もっと読む)

パターン形成方法

【課題】疎密に配置された複数のパターンを正確に形成できるパターン形成方法を提供する。

【解決手段】基板14上に第1絶縁膜15を形成し、第1絶縁膜15上に疎密に配置された第1開口パターン31a〜31dを有する第1マスク材31を形成し、第1マスク材31を用いて第1絶縁膜15をエッチングして第1開口パターン31a〜31dを転写する工程と、第1マスク材31を除去し、第1開口パターン15a〜15dの上面を塞いで第1絶縁膜15上に、第1絶縁膜15と異なる材質の第2絶縁膜32を形成する工程と、第2絶縁膜32上に、第1開口パターン15a〜15dと対向する第2開口パターン36a〜36dを有する第2マスク材36を形成し、第2マスク材36を用いて第2絶縁膜32をエッチングし、第2マスク材36を用いて第1絶縁膜15を予め定められた深さまでエッチングする工程と、を具備する。

(もっと読む)

不揮発性半導体メモリ

【課題】信頼性の高い不揮発性半導体メモリを提供できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、複数のメモリセルが配置されるメモリセルアレイ領域100と、メモリセルアレイ領域100の周囲を取り囲む周辺回路領域と、周辺回路領域とメモリセルアレイ領域100との境界部分であるセルアレイ隣接領域105と、メモリセルアレイ領域100内に層間絶縁膜を介して設けられる複数の第1導電線SLと、セルアレイ隣接領域105内に層間絶縁膜を介して設けられる複数の第2導電線M2とを具備し、複数の第2導電線M2はその配線内にスリット50が形成されていることを備える。

(もっと読む)

半導体装置およびその形成方法

【課題】半導体装置の多層配線構造において、下部Cu配線と上部絶縁層との界面に、優れた密着性と耐酸化性と拡散バリア性を有する新規界面層を形成する。

【解決手段】半導体装置の多層配線構造は、半導体ウェハ(1)上に形成した第1の絶縁層(2)と、前記第1の絶縁層上(2)に形成されるCu配線層(4)と、前記Cu配線層上(4)に形成される第2の絶縁層(6)と、前記Cu配線層(4)と前記第2の絶縁層(6)との界面に形成される金属酸化物層(5)と、を備える。金属酸化物層(5)は、Cu配線層(4)上にSnまたはZnなどの金属を浸漬メッキし、その後このメッキ層を酸化性雰囲気中で加熱処理して形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】コンタクトプラグ材料の基板への拡散を抑制する半導体装置及び半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、半導体基板200と導通するコンタクトプラグとなるCu膜260と、Cu膜260の少なくとも底面側に、半導体基板200と接触して配置された柱状結晶構造をもつTiN膜242と、Cu膜260の少なくとも底面側に、TiN膜242と接触して配置された、TiNのアモルファス膜244と、Cu膜260の底面側と側面側に、少なくとも一部がアモルファス膜244とCu膜260とに接触して配置された、TiN膜242材と同じ材料で柱状結晶構造をもつTiN膜246と、Cu膜260の側面側に配置されたSiO2膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

電解メッキ液、電解メッキ方法、および半導体装置の製造方法

【課題】銅配線層を電解メッキ法で形成する際に電極となるシード層の溶解に起因する銅メッキ層の欠陥の発生を抑制する電解メッキ液及び該メッキ液を用いた電解メッキ方法を提供する。

【解決手段】電解メッキ液として、極性溶媒と、前記極性溶媒中に溶解した硫酸銅を含み、さらに添加剤として、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤とを添加した電解メッキ液を使う。

(もっと読む)

マスクパターン形成方法

【課題】隣接するマスクパターンが揃った状態に形成できるマスクパターンを提供する。

【解決手段】下地層のシリコン酸化膜7上にマスク用の多結晶シリコン膜8を形成する。その上にシリコン酸化膜9を成膜し、リソグラフィ処理でラインパターン9aに加工し、シリコン窒化膜を膜厚dで形成しスペーサ加工する。スペース領域にシリコン酸化膜12aを埋め込み、シリコン窒化膜を除去して間隔dの空隙部を形成する。ラインパターン9a、12aを利用してRIE加工して多結晶シリコン膜8をエッチングし、さらにCDE加工で横方向にwだけエッチングする。ラインパターン9a、12aを除去すると幅寸法Aのラインパターン8aを間隔Bを存したパターンを得ることができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 耐湿(耐水分、耐水素)性の優れた強誘電体膜を有するキャパシタのパッド構造を備え、パッドに傷が生じても、水素、水分に対する耐性を回復することのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 半導体基板の上方に電極間に挟まれた強誘電体膜を備えたキャパシタを形成する工程と、半導体基板の上方にキャパシタの電極と電気的に接続されるパッド電極を形成する工程と、半導体基板の上方にパッド電極を保護する保護膜を形成する工程と、保護膜にパッド電極の少なくとも一部が露出する開口部を形成する工程と、パッド電極の表面に測定端子を当てる工程と、測定端子を当てたパッド電極の表面をエッチングする工程と、保護膜とパッド電極の開口部を覆う水素吸蔵膜を形成する工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】半導体素子11は、半導体素子11の主面に形成された電極パッド10と、半導体素子11の主面及び電極パッド10の周辺部を被覆することにより、電極パッド10表面に露出領域を画定するカバー層12と、カバー層12及び電極パッド10の露出領域を被覆するとともに、電極パッド10の中心を基準として点対称となる部位に、露出領域に到達し且つカバー層12を露出させる貫通孔13hを有する絶縁層13と、を備える。このような構成の半導体装置1によれば、半導体装置の信頼性が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体基板のストリートに合金層を形成すること無く、しかもバリア層の横方向エッチングであるサイドエッチング量が少ない半導体装置および半導体装置の製造方法を提供する。

【解決手段】 半導体装置の入出力端子となる電極パッド2と、電極パッド2上に順次設けるバリア層および共通電極層6と、この共通電極層6上に設ける突起電極11を有する半導体装置において、バリア層は、2層からなるとともに、突起電極11材料または共通電極層6材料と電極パッド2材料とが相互に拡散することを抑制する材料からなり、共通電極層6側の第2のバリア層5は、電極パッド2側の第1のバリア層4より膜厚が薄い半導体装置およびその製造方法により、第2のバリア層5のサイドエッチング量を少なくすることが可能となり、さらに半導体基板のストリートに合金層が形成されることはない。

(もっと読む)

半導体チップ及び半導体装置

【課題】小型化が可能な半導体チップ及び半導体装置を提供する。

【解決手段】上面、底面、及びこれらの面を接続する側面13を有する半導体基板11と、上面にあり、半導体基板11に形成された半導体素子と接続された上部配線15と、底面にあり、側面13で囲まれた内側に側面13から離間して配置された複数の接続端子26と、半導体基板11を貫通する貫通孔21を通り、上部配線15と接続端子26とを電気接続する貫通配線25と、接続端子26間の底面にあり、接続端子26とは凹部31を隔てて配置された絶縁性の分離膜27とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の異なる回路領域にそれぞれの要求特性を満足する配線を形成する。

【解決手段】所定基板上に配線の主要部を構成する第1の金属膜を形成し(ステップS1)、その上にエレクトロマイグレーション耐性向上に寄与するTi,Zr等の不純物元素を含む第2の金属膜を形成する(ステップS2)。次いで、不純物元素を添加すべき配線の形成領域にある第2の金属膜は残し、不純物元素の添加が不要な配線の形成領域にある第2の金属膜を部分的に除去する(ステップS3)。その後、熱処理により、残る第2の金属膜の不純物元素を下の第1の金属膜に拡散させる(ステップS4)。これにより、不純物元素濃度の異なる第1の金属膜を基板上に形成できる。これを用いて配線を形成することにより、異なる領域にそれぞれに適した配線を形成することが可能になる。

(もっと読む)

半導体装置およびその製造方法

【課題】低温シリサイド膜を使用する半導体素子において、コンタクトプラグ形成時に、CMP処理でスクラッチが発生し、隣接のプラグとの短絡が生じるのを防止する製造方法を提供する。

【解決手段】NANDフラッシュメモリのゲート電極MG、SG、PGにコバルトシリサイド膜4を設ける。これらのゲート電極の上にプラズマTEOS膜からなるシリコン酸化膜5、シリコン窒化膜7、プラズマTEOS膜からなるシリコン酸化膜9を形成し、その上面にプラズマシラン膜10を形成する。これらの絶縁膜膜を貫通してシリコン基板1の表面に達するコンタクトホールを形成し、内部に窒化チタン膜とタングステン膜を埋め込んでコンタクトプラグ11を設ける。スクラッチ耐性の高いプラズマシラン膜を設けたので、タングステン膜を成膜した後のCMP処理において、プラグに曲がりが発生せず、隣接のプラグとの短絡が生じない。

(もっと読む)

半導体装置及びその製造方法

【課題】データ読み書きの繰り返しによるVthの変動を抑制する。

【解決手段】本発明の半導体装置は、第1の層間絶縁膜1中に形成された下層配線2を備え、第1の層間絶縁膜1と下層配線2の上に形成された絶縁膜3を備え、絶縁膜3の上に形成された第2の層間絶縁膜4を備え、第2の層間絶縁膜4の上に形成され下層配線2にビアホール6を介して接続されたAl製の上層配線5を備え、上層配線5の上面および側面に形成されたアルミナ膜8を備え、上層配線5の上に形成された第3の層間絶縁膜9を備えたものである。

(もっと読む)

半導体製造装置

【課題】配線回路パターンを形成するエッチングにおいて、加工変換差のバラツキを抑制すると共に、ウエハを載置する下部電極の温度を短時間で切り替え可能にする。

【解決手段】本発明の半導体製造装置は、反応室2と、半導体基板5を載置する下部電極4と、反応室2内に下部電極4と対向するように配設された上部電極3とを備え、2つの電極3、4間に高周波電力を供給してプラズマを発生させるように構成されたものであって、反応室2の外側に、発光した光を反応室2の透明な室壁2aを通して上部電極3の周辺部に照射して加熱する発光加熱装置6を配設したものである。

(もっと読む)

1,961 - 1,980 / 5,243

[ Back to top ]