Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

4,001 - 4,020 / 5,243

多孔質薄膜の製造方法、多孔質薄膜およびこれを用いた半導体装置

【課題】 成膜が容易で、高速で成膜可能な低誘電率薄膜を提供する。

【解決手段】気相より、空孔生成材料と、骨格生成材料とを、基板表面に供給する工程と、前記基板表面で、前記骨格生成材料によって生成される骨格が前記空孔生成材料を取り囲むように画定された薄膜を成膜する工程と、前記薄膜から前記空孔生成材料を除去し、空孔を形成する工程とを含み、前記空孔を前記骨格が取り囲むように形成された多孔質薄膜を形成する。

(もっと読む)

半導体装置用構造およびその製造方法

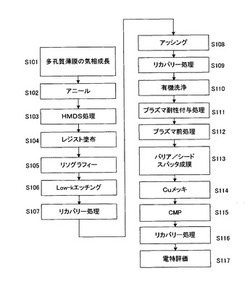

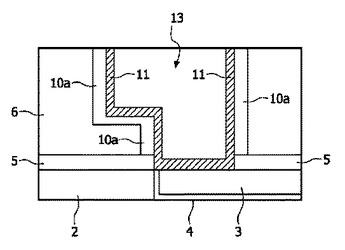

半導体装置用のダマシン配線(1)の製造方法を示す。非導電性バリヤ層(10)が、多孔質低誘電率材料によって定義されるパッセージ(7)の壁の上と、パッセージ(7)の一端を閉じる銅領域(3)の表面の上とに形成される。非導電性バリヤ層(10)は、誘電性材料の貫通細孔からなるその下層部(10a)が非導電性を残している間に、その上層部(10b)を導電層に変換するためにプラズマ処理される。ついで、パッセージ(7)は、今度は導電性になっているバリヤ(10)の上層部(10b)を介して第1銅領域(3)と電気配線を形成する第2銅領域(13)で満たされる。当業者にとって明らかなように、本文献において開示、請求される本発明のすべての実施形態は、本発明の範囲を超えることなしに結合されても良い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 WPPを使用した半導体装置において、最上層配線間のショート不良を防止することにより、信頼性を向上させることのできる技術を提供する。

【解決手段】 最上層配線43aと再配線50との間に緩衝層47を設ける。このとき、例えば、最上層配線43aは銅膜より形成され、緩衝層47は、アルミニウム膜より形成される。さらに再配線50は、銅膜51とニッケル膜52の積層膜から形成される。このように構成された半導体装置において、低温と高温との間の温度サイクルで3重点Xに応力が集中する。この3重点Xに集中した応力は、緩衝層47の存在によって緩和され、3重点Xの直下にある界面Yへの応力の伝達を抑制することができる。このため、界面Yでの応力による剥離を防止できる。

(もっと読む)

半導体装置の製造方法

【課題】被エッチング膜に堆積されるハロゲン化カーボン膜およびハロゲン化シリコン膜を効果的に除去することが可能な半導体装置の製造方法を提供する。

【解決手段】シリコン膜と酸化シリコン膜および窒化シリコン膜の少なくとも一方の層が成膜された半導体基板をハロゲンを含むエッチングガスによりドライエッチング処理する際、エッチング面に堆積されるハロゲン化カーボン膜およびこのハロゲン化カーボン膜上のハロゲン化シリコン膜を除去する工程を含む半導体装置の製造方法であって、前記ハロゲン化カーボンおよびハロゲン化シリコンの除去は、前記ドライエッチング後に希フッ酸水溶液でウェットエッチング処理する工程と、前記エッチング面を含む全面にOHまたはHを含む有機材料膜を被覆した後、酸素プラズマによりアッシングする工程とを含むことを特徴とする半導体装置の製造方法。

(もっと読む)

電子装置およびその製造方法

【課題】 電力増幅モジュールやそれに用いる集積受動部品または半導体チップの低コスト化および高性能化を図る。

【解決手段】 集積受動部品5において、シード膜51、銅膜53およびニッケル膜54の積層膜からなる配線55により、RFパワーモジュールのローパスフィルタ回路を構成するインダクタ素子が形成される。ニッケル膜54は、銅膜53の全面上に形成され、表面保護膜としての絶縁膜61の開口部62から露出するニッケル膜54上に、金膜63およびバンプ電極64が形成されている。ニッケル膜54は、無電解Ni−Pめっき膜であり、リンを10重量%以上含有し、非磁性状態とされている。

(もっと読む)

3次元半導体集積回路装置、その製造方法、それを用いたパッケージ化3次元半導体集積回路装置及びその実装方法。

【課題】製造歩留まりの優れた3次元半導体集積回路装置及びその製造方法、それを用いたパッケージ化3次元半導体集積回路装置及びその実装方法を提供する。

【解決手段】シリコン製半導体チップをベース部に機能素子が対向するように積層し、半導体チップの材質に近いポリシリコンで半導体チップを埋め込み、あたかも1枚のウエーハの如くする。

(もっと読む)

ヒューズ素子及びその切断方法

【課題】ヒューズ回路を大きくすることなく層間絶縁膜のクラックを防止できるとともに、ヒューズ切断前後において大きな抵抗変化を得ることができるヒューズ素子及びその切断方法を提供する。

【解決手段】シリコン層を含む配線部14と、配線部14の一端側に接続されたコンタクト部20bと、配線部14の他端側に接続されたコンタクト部20aとを有するヒューズ素子において、コンタクト部20bからコンタクト部20aへ配線部14を介して電流を流し、コンタクト部20aの金属材料をシリコン層中にマイグレーションさせることにより、配線部14とコンタク部20aとの間の接続抵抗を変化させる。

(もっと読む)

三次元積層構造を持つ集積回路装置の製造方法

【課題】 半導体回路層間の隙間に電気的絶縁性接着剤を確実に配置でき、前記隙間よりはみ出た余分の接着剤を除去しなくてすむ、三次元積層構造集積回路装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの内部に複数の埋込配線(導電性プラグ)15を形成し、それらの端を第1半導体回路層1aの裏面に露出させる。第2半導体回路層2の表面に、各プラグ15に対応して複数のバンプ電極43aを形成する。第2半導体回路層2の表面に、バンプ電極43aとは重ならない形状にパターン化された電気的絶縁性接着剤膜44aを形成する。その後、第1半導体回路層1aの裏面と第2半導体回路層2の表面を対向させて近づけ、その間で接着剤膜44aを変形させながら各バンプ電極43aの少なくとも一部を押し潰すことにより、埋込配線15とバンプ電極43aとを相互に機械的接続すると共に、接着剤膜44aにより両回路層1aと2を接着する。

(もっと読む)

層間絶縁構造およびその形成方法

【課題】層間絶縁体、あるいは層内絶縁体および層間絶縁体としてエアギャップを統合する銅のインタコネクトを製造する方法を提供すること。

【解決手段】層間絶縁構造の形成方法であって、第1の金属層を提供する工程と、第1の犠牲層を堆積する工程と、エッチング停止層を堆積する工程と、第2の犠牲層を堆積する工程と、2層のハードマスクを形成する工程と、2層のハードマスクをパターニングしてビアマスクおよびトレンチマスクを生成する工程と、第2の犠牲層をエッチングしてビアを形成する工程と、エッチング停止層の剥き出し部分と第1の犠牲層とをエッチングして第1の金属層を剥き出しにする工程と、第2の犠牲層をエッチングしてトレンチを形成する工程と、バリア金属および銅を堆積し、平坦化して第2の金属層を形成する工程と、第1および第2の犠牲層を分解して上記犠牲層をエアギャップと交換する工程とを包含する。

(もっと読む)

洗浄方法および半導体装置の製造方法

【課題】金属化合物からなるエッチング残渣または研磨残渣を、配線材料に対して選択的に除去することができる洗浄方法および半導体装置の製造方法を提供する。

【解決手段】下層配線18が設けられた基板上に、低誘電率絶縁膜20、低誘電率絶縁膜22を含む層間絶縁膜を成膜する。次いで、エッチングにより、層間絶縁膜をエッチングして、コンタクトホール24を形成するとともに、このコンタクトホール24の上部に連通する配線溝25を形成し、コンタクトホール24の底部に下層配線18を露出させる。続いて、トリアリルアミンおよびトリス(3−アミノプロピル)アミンの少なくとも1種を含有する超臨界二酸化炭素流体を、この状態の基板の表面に供給して洗浄することで、下層配線18からの金属化合物18’を含むエッチング残渣を除去する洗浄方法および半導体装置の製造方法である。

(もっと読む)

半導体装置、及びその製造方法

【課題】 チップサイズを増大させることなく、Cu配線等の配線における例えばCMP処理による膜厚の薄膜化が起こった箇所を特定するのに好適な電気抵抗測定パターンを有する半導体装置およびその製造方法を提供する。

【解決手段】 上層回路配線21bと、上層回路配線21bの膜厚を電気抵抗値によって測定するための電気抵抗測定パターン22aと、電気抵抗測定器を電気的に接続するための測定器用パッド24a・24bとを備えている。電気抵抗測定パターン22aおよび測定器用パッド24a・24bは、これら測定器用パッドおよび電気抵抗測定パターン22aが配置されている層とは異なる層に配置されている下層接続配線23a・23bを介して、互いに電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】 半導体装置100は、半導体基板(不図示)上に形成されるとともに凹部が形成された第1の絶縁膜102と、導電体206、ならびに導電体206の一端と他端にそれぞれ設けられた第1の端子202および第2の端子204を有し、第1の絶縁膜102上に設けられた電気ヒューズ200とを含む。導電体206は、第1の絶縁膜102の凹部を埋め込むように形成されるとともに、導電体206を構成する材料が凹部外に流出した流出領域212を有し、流出領域212とは異なる箇所が切断される。

(もっと読む)

半導体装置の製造方法

【課題】 コンタクトパッドを形成する半導体装置の製造方法において、隣接する半導体素子間のショートを防止する。

【解決手段】 シリコン基板11上に、それぞれが金属層15を含むゲート電極17とゲート電極17を覆うゲート側壁絶縁膜20とを有する複数のゲート電極構造体を形成する工程と、ゲート電極構造体を覆って全面にポリシリコン膜を堆積する工程と、ポリシリコン膜をパターニングし、隣接する2つのゲート電極構造体の間でシリコン基板11に接続するコンタクトパッド22を形成する工程(図3(g))と、ゲート側壁絶縁膜のくぼみ21に残留するポリシリコン24を酸化させて酸化シリコン25に形成する工程(図3(h))とをこの順に有する。

(もっと読む)

電気光学装置、電子機器

【課題】層間を電気的に接続するために形成されるコンタクトホールを、コンタクトホールの下層に形成された端部上に形成するに際し、コンタクトホールの形成に起因する層間の電気的な接続の切断を確実に防止できる構造を有する電気光学装置を提供する。

【解決手段】TFT基板10に成膜されるとともに、スペースh1を有する段部150が少なくとも一部に形成された走査線11と、走査線11上に積層された下地絶縁膜12と、下地絶縁膜12上に積層された半導体膜1と、半導体膜1上に積層された層間絶縁膜41と、層間絶縁膜41の段部150の上方に、層間絶縁膜41を貫通するよう形成されたコンタクトホール81と、を具備し、コンタクトホール81は、段部150の端部11tから、平面的に下地絶縁膜12の膜厚以上離間した段部150のスペースh1の位置上に形成されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 密着性を高める機能を併せ持つバリア層が形成されるまでの期間に、配線部材の十分な密着性を確保し、配線部材の剥離を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a1)半導体基板の上に形成された絶縁膜に凹部を形成する。(a2)凹部の内面、及び絶縁膜の上面を覆うように、CVD法により、Mnからなる第1の膜を形成する。(a3)第1の膜の上に、Cuを主成分とする導電材料を堆積させるとともに、凹部内に該導電材料を充填する。(a4)半導体基板をアニールする。

(もっと読む)

半導体装置

【課題】メモリセルと周辺回路を備えた半導体装置において、周辺回路領域にキャパシタを、マスク工程を増加させることなく形成する。

【解決手段】

メモリセルと周辺回路を備えた半導体装置において、前記周辺回路領域に形成されるキャパシタは、前記メモリセル領域のゲート電極と同時に形成される下部電極と、前記メモリセル領域において前記コンタクトホール内壁面を覆う絶縁膜と同時に形成される容量絶縁膜と、前記コンタクトホールに形成されるコンタクトプラグと同時に形成される上部電極とを備える。

(もっと読む)

デュアル・ダマシン構造を製造するためのフォトマスクおよびその形成方法

デュアル・ダマシン構造を製造するためのフォトマスク、およびこれを形成する方法が提供される。多層ステップ・アンド・プリント(SFIL)テンプレートの製造方法は、基板と金属化層と第1のレジスト層とを含むブランクを提供するステップとを含んでいる。デュアル・ダマシン構造の金属層パターンは、リソグラフィ・システムを使用して基板内に第1の深さで形成される。ブランクから第1のレジスト層が除去され、第2のレジスト層が塗布される。リソグラフィ・システムを使用して、第1のパターンが第2の深さにエッチングされると同時に、第1の深さでデュアル・ダマシン構造のバイア層パターンが形成される。第1および第2のパターンは、SFIL工程を使用してデバイスの多層内に形成されるべきフィーチャに対応している。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 導電部材中のCu以外の元素の含有量を低減させ、比抵抗を低下させることができる半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、凹部が設けられた絶縁膜を形成する。(b)開口の内面及び絶縁膜の上面を、Cu以外に第1の金属元素を含むCu合金からなる補助膜で覆う。(c)凹部内に充填されるように、補助膜上に、Cuを主成分とする導電部材を堆積させる。(d)P化合物、Si化合物、またはB化合物を含有する雰囲気下で熱処理を行う。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 チタンを含む金属膜のドライエッチにフッ素系ガスを使用する際に形成される側壁を除去する際に析出異物が生成されることがなく、短絡不良の発生を確実に防止することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 半導体基板上に形成されたチタンを含む金属膜17上にエッチングマスク23を形成し、エッチングマスク23を介して、金属膜17をドライエッチングする。当該ドライエッチング後に、エッチングマスク23を除去し、金属膜17の表面に水分子の透過を阻害する防水膜32を形成する。そして、前記ドライエッチングの過程でエッチング部位18の内側面に形成された反応生成物からなる側壁31の、金属膜17の上面より上方に突出する突出部を、フッ素元素を含むガスを用いたプラズマ処理により行うこと除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は小型化を図ると共に、デバイス形成層を保護した状態で貫通孔及び貫通電極を形成することを課題とする。

【解決手段】 デバイス形成層18と電極パッド20を有する半導体素子14の電極パッド20と半導体素子14の他面側に形成された再配線パターン52とを接続する貫通電極56を有する半導体装置の製造方法であって、半導体素子14の上面側にデバイス形成層18及び電極パッド20を形成し、電極パッド20及びデバイス形成層18の表面に第1レジスト層62を形成し、電極パッド20にエッチングにより開口64を形成し、開口64に連通する位置に貫通孔54をエッチングにより半導体素子14に形成する。第1レジスト層62によりデバイス形成層18を保護すると共に、貫通電極56を設けてフリップチップ接続を可能にして小型化を図る。

(もっと読む)

4,001 - 4,020 / 5,243

[ Back to top ]