Fターム[5F033RR05]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 窒化物 (4,436)

Fターム[5F033RR05]の下位に属するFターム

SiN (4,133)

Fターム[5F033RR05]に分類される特許

121 - 140 / 303

Cuキャップ層としてCuゲルマナイドおよびCuシリサイドを集積および作製する方法

【課題】周囲の誘電体材料にダメージを与えない銅配線上のキャップ層を形成する方法を提供する。

【解決手段】Cu、N、およびSiおよび/またはGeを含むキャップ層6を、銅の導電構造2の上に形成する方法であって、200℃と400℃との間の温度範囲で、構造をGeH4および/またはSiH4含有雰囲気3に晒すことにより、銅の導電構造2の上に少なくとも1つのキャップ層を形成する工程と、NH3プラズマ処理5を行って、少なくとも部分的に窒化されたキャップ層6を形成する工程と、少なくとも部分的に窒化されたキャップ層6の上に誘電体バリア層7を形成する工程とを含み、少なくとも1つのキャップ層を形成する工程の前に、250℃と450℃との間の温度範囲で、銅の導電構造のプレアニール工程が行われることを特徴とする方法。

(もっと読む)

半導体素子及びその製造方法

【課題】金属配線を電気的に連結させるビアプラグを形成する工程過程で発生する素子の信頼性を低下させる問題を解消すること。

【解決手段】半導体基板上に多数の金属配線を形成する段階;ビアホールが形成される領域の前記金属配線上に反応防止膜を形成する段階;前記反応防止膜を含む前記半導体基板上に層間絶縁膜を形成する段階;前記反応防止膜の上部の前記層間絶縁膜をエッチングしてビアホールを形成する段階;前記ビアホール内部にビアプラグを形成する段階を含む半導体素子の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】配線に十分なEM耐性を確保しつつ、配線層間・線間リークを低減しかつTDDB寿命を向上することができるとともに、ビアエッチの際に高選択比を確保して高信頼性な配線を得ることができる半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板上の第1の絶縁膜1に形成された配線溝M1と、配線溝M1側壁及び底部に形成されたタンタル系バリアメタル2aと、タンタル系バリアメタル2aに沿って配線溝M1を埋め込むように形成されたCu膜2bと、Cu膜2b表面に形成された銅とシリコンの合金層または銅とシリコンと窒素のCuSiN層3aと、CuSiN層3aの上及び第1の絶縁膜1の上に形成され第1の絶縁膜1より高密度なSiNx膜3dとを有する。

(もっと読む)

半導体装置とその製造方法

【課題】水素等の還元性物質からキャパシタ誘電体膜を効果的に保護できる半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に形成された第1絶縁膜20と、第1絶縁膜20の上に形成された強誘電体キャパシタQと、キャパシタQを覆う第1絶縁性水素バリア膜31及び第2絶縁性水素バリア膜32と、第2絶縁性水素バリア膜32の上に形成され、前記第1、第2絶縁性水素バリア膜31、32を貫くホール46を上部電極28aの上に備えた第2絶縁膜33と、ホール46内に形成されて上部電極28aと電気的に接続された導電性部材47とを有し、所定のエッチングガスに対し、第2絶縁性水素バリア膜32のエッチング速度が第1絶縁性水素バリア膜31のエッチング速度よりも速いことを特徴とする半導体装置による。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上にnチャネル型及びpチャネル型電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。nチャネル型及びpチャネル型電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。応力を有する絶縁膜によって半導体層へ与えられる歪み、半導体層の面方位、又はチャネル長方向の結晶軸を制御することによって、nチャネル型とpチャネル型電界効果トランジスタとの移動度の差を軽減し、電流駆動能力及び応答速度を同等とする。

(もっと読む)

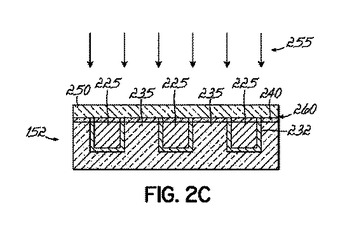

RC遅延を減少するために誘電体層にエアギャップを生成する方法及び装置

【課題】 誘電率の低い誘電体材料を含む多レベル相互接続構造体を形成するための方法を提供する。

【解決手段】 相互接続構造体の誘電体材料にエアギャップを生成するための方法及び装置。一実施形態では、半導体構造体を形成する方法において、基板上に第1の誘電体層を堆積し、第1の誘電体層にトレンチを形成し、トレンチに導電性材料を充填し、導電性材料を平坦化して第1の誘電体層を露出させ、導電性材料及び露出された第1の誘電体層に誘電体バリア膜を堆積し、この誘電体バリア膜の上に硬質マスク層を堆積し、誘電体バリア膜及び硬質マスク層にパターンを形成して基板の選択された領域を露出させ、基板の選択された領域において第1の誘電体層の少なくとも一部分を酸化させ、第1の誘電体層の酸化された部分を除去して、導電性材料の周りに逆のトレンチを形成し、逆のトレンチに第2の誘電体材料を堆積しながら逆のトレンチにエアギャップを形成することを含む方法が提供される。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】SiOF膜を含む層間絶縁膜にダマシン法で埋め込み配線を形成する半導体集積回路装置において、埋め込み配線用の配線溝を形成する際に用いるエッチングストッパ層とSiOF膜との界面剥離を防止する。

【解決手段】SiOF膜26、29を含む層間絶縁膜をドライエッチングして形成した配線溝32の内部にダマシン法でCu配線33を埋め込む際、上記ドライエッチングのエッチングストッパ層を構成する窒化シリコン膜28とSiOF膜26との間に酸窒化シリコン膜27を介在させ、SiOF膜26中で発生した遊離のFを酸窒化シリコン膜27でトラップする。

(もっと読む)

電界効果トランジスタ、半導体チップ及び半導体装置

【課題】均一性や生産性が高いと共に、高周波性能として、雑音指数が小さく、かつ付随利得の大きい電界効果トランジスタ(FET)、このFETを備える半導体チップ及び半導体装置を提供すること。

【解決手段】本発明のFET1は、GaAs半導体基板2の上に、i形GaAsバッファ層3と、i形InGaAs二次元電子ガス層4と、n形AlGaAs電子供給層5と、が積み上げられ、n形AlGaAs電子供給層5の上に線状にショットキー性接触するゲート電極12があり、ゲート電極12の両横から離れ、かつn形AlGaAs電子供給層5の上に、n形InGaPエッチング停止層6と、続いて同程度の横位置でn形GaAsコンタクト層7とが積み上げられ、n形GaAsコンタクト層7の上にコンタクト層7の端から離れて帯状にオーム性接触をする電極として各側にソース電極9とドレイン電極10とを備える。

(もっと読む)

BCN系の絶縁膜及びその製造方法並びに半導体装置およびその製造方法

【課題】安定した低誘電率と高い硬度(ヤング率)を有するBCN膜が形成できる半導体装置の製造方法が提供する。

【解決手段】従来のBCl3ガスに代わる、腐食性のない有機アミノボロン系ガスを用いてBCN膜を成膜する。その例として、トリスジメチルアミノボロンを用いて、プラズマCVDにより成膜を行うことで、 比誘電率が2.5以下で弾性率(ヤング率)が8GPa以上であるBCN系の低い誘電率を持つ絶縁体材料膜を得る。

(もっと読む)

半導体素子のコンタクトプラグ形成方法

【課題】セル領域及び周辺回路領域のコンタクトプラグ形成工程の単純化及びコスト削減をする方法を提供する。

【解決手段】セル領域A及び周辺回路領域Bが定義され、上記周辺回路領域Bに第1のコンタクトプラグ110が形成された半導体基板100上に第1の絶縁膜108を形成する段階と、上記第1の絶縁膜をエッチングして上記セル領域Aには接合領域104が露出され、上記周辺回路領域Bでは上記第1のコンタクトプラグが露出される第2のコンタクトホールを形成する段階と、上記第2のコンタクトホール内に第2のコンタクトプラグ116を形成する段階と、上記周辺回路領域Bの上記第2のコンタクトホール内に形成された上記第2のコンタクトプラグを除去する段階と、上記第2のコンタクトホール側壁にスペーサ120を形成する段階と、上記第2のコンタクトホール内に第3のコンタクトプラグ124を形成する段階を含む。

(もっと読む)

半導体装置の製造装置

【課題】メタルキャップ層の製造工程におけるパーティクルの発生や組成比の変動を抑制させて、半導体装置の信頼性と生産性を向上させた半導体装置の製造装置に関するものである。

【解決手段】成膜チャンバ33は、第1カソード40aと第2カソード40bを備え、各カソード40a,40bに、それぞれZrを含む第1ターゲット42aと、BNを主成分とする第2ターゲット42bを搭載する。そして、成膜チャンバ33は、各外部電源を駆動して第1ターゲット42aと第2ターゲット42bとを同時にスパッタし、第1絶縁層の表面と第1配線の表面、又は、第2絶縁層の表面と第2配線の表面に、ZrBNを主成分とするメタルキャップ層を成膜させる。

(もっと読む)

半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法

本明細書には概して半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法が記載されている。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】接続孔内から無電解めっき層が剥がれて抜け落ちるのを防止できる半導体装置及びその作製方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体層32上に形成された第1の絶縁層33,203と、前記第1の絶縁層に形成され、前記第1の絶縁層の上面から途中まで異方性エッチングにより形成された第1の接続孔203cと、前記第1の絶縁層に形成され、前記第1の接続孔に繋げられ、前記第1の接続孔下の前記第1の絶縁層が等方性エッチングにより形成され、前記半導体層上に位置する第2の接続孔203gと、前記第1の接続孔内の側面及び前記第1の絶縁層上に形成された第2の絶縁層203dと、前記第2の接続孔の底面の前記半導体層から成長され、前記第2の接続孔内及び前記第1の接続孔内に埋め込まれた無電解めっき層204aと、を具備することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型不揮発性半導体記憶装置において、製造時にメモリセルを紫外線から保護する紫外線遮光膜を安定して形成できるようにする。

【解決手段】半導体基板1の上部にX方向に延びるビット線拡散層9と、半導体基板1の上にY方向に延びると共に電荷トラップ膜4及びゲート電極5からなるゲート構造体とを有する不揮発性半導体記憶装置に、ビット線拡散層3と接続される第1のコンタクト9が形成された第1の層間絶縁膜8と、該第1の層間絶縁膜8の上に形成された紫外線遮光膜10及び第2の層間絶縁膜11を貫通して下端部が第1のコンタクト9と接し且つ上端部が金属配線13と接続される第2のコンタクト12とを設ける構成とする。

(もっと読む)

半導体装置

【課題】銅めっき層をアンテナの導体に用いた、集積回路とアンテナが一体形成された半導体装置において、銅の拡散による回路素子の電気特性への悪影響を防止するとともに、密着性の良い銅めっき層を提供することを課題とする。また、集積回路とアンテナが一体形成された半導体装置において、アンテナと集積回路の接続不良に伴う半導体装置の不良を防止することを課題とする。

【解決手段】アンテナ101と集積回路100が一体形成された半導体装置において、アンテナ101として銅めっき層を用いるとともに、そのシード層107としてAg、Pd及びCuの合金を用い、バリア層116としてTiN又はTiを用いるものである。

(もっと読む)

電子素子および電子素子の製造方法

電子素子、特にTFT、蓄積コンデンサまたはスタック装置の導電層間の交差部等を備えるものが開示されている。電子素子は、電極を形成する第1の導電層を基板上に備える。第2の導電層により形成された第2の電極は第1の電極から少なくとも誘電体層により隔てられている。この誘電体層は電気絶縁材料の中間層、好ましくは絶縁破壊に対して高い耐性を有する中間層と、光パターニング可能な電気絶縁材料のさらなる層とを包含する。 (もっと読む)

半導体装置の製造方法

【課題】P型トランジスタの特性向上処理とN型トランジスタの特性向上処理とを施したとしても、製造工程の増加を抑制することができ、かつデバイス全体の性能の劣化を抑制することができる半導体装置の製造方法を提供する。

【解決手段】第一の領域の半導体基板1上に、加熱により応力が生ずるカバー膜11を形成する。当該カバー膜11が形成された半導体基板1に対して、加熱処理を施す。これにより、カバー膜11に応力が発生し、当該応力に起因して第一のトランジスタの特性を向上させる第一の特性向上処理が、半導体基板1に施される。また、カバー膜11をマスクとして使用して、当該カバー膜11から露出している第二の領域の半導体基板1に対して、第二のトランジスタの特性を向上させる第二の特性向上処理を施す。

(もっと読む)

NORフラッシュデバイス及びその製造方法

【課題】本発明は、NORフラッシュデバイス及びその製造方法を提供する。

【解決手段】バックエンドオブライン(BEOL)構造を有するNORフラッシュデバイスにおいて、BEOL構造は導電領域を有する基板と、基板上に形成された第1層間絶縁膜と、導電領域に形成される第1金属ラインと、該第1金属ラインと第1層間絶縁膜を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通する第1コンタクト及び第1コンタクトを通じて第1金属ラインと連結される第2金属ラインを具備して、第1コンタクト、第1及び第2金属ラインのうちで少なくとも一つは銅であり、第1及び第2層間絶縁膜のうちで少なくとも一つは、低誘電物質を含む。

(もっと読む)

金属配線形成方法

【課題】本発明は、低価の工程が可能であり、低い電気抵抗を提供できる金属配線の形成方法を提供することを目的とする。

【解決手段】

(a)基板上部に誘電体層を蒸着する段階;(b)前記誘電体層上部に金属配線の潜在的マスクパターンを形成する段階;(c)前記潜在的マスクパターンにより露出された誘電体層をエッチングする段階;(d)前記基板を活性化処理して表面にシード層を形成する段階;(e)前記潜在的マスクパターンおよびその上部をリフトオフして除去する段階;および(f)上記ターン形成されたシード層上部に金属層をめっきする段階を含む金属配線形成方法と前記方法により製造された金属配線構造および前記構造を含む薄膜トランジスタ−液晶ディスプレーを提供する。

(もっと読む)

121 - 140 / 303

[ Back to top ]