Fターム[5F033RR26]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 不純物を含むもの (19)

Fターム[5F033RR26]に分類される特許

1 - 19 / 19

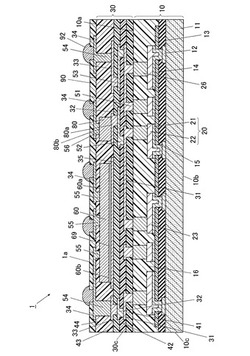

半導体装置及びその製造方法

【課題】薄型化及び小型化を図る半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10と、半導体チップ10の上に積層された多層配線構造30と、多層配線構造30内に埋設された電子部品60,80と、を備える。半導体チップは、半導体基板11と、半導体基板上に形成された内部配線20と、内部配線を被覆するようにして半導体基板上に形成された封止層16と、を有し、多層配線構造が封止層上に形成されている。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置用絶縁膜の製造方法、半導体装置の製造方法

【課題】半導体装置の性能向上と信頼性向上を両立することができる半導体装置用絶縁膜の製造方法、半導体装置の製造方法を提供する。

【解決手段】Cu配線21上に形成する半導体装置用絶縁膜として、プラズマにより解離したアルキルボラジン化合物中のボラジン骨格系分子を基本単位として気相重合した第1の膜23、第2の膜24を形成する際、配線21に接する第1の膜23の膜中炭素量を9%以上、かつ、35%以下とすると共に、第1の膜23及び第2の膜24全体の実効誘電率を4.0以下とする。

(もっと読む)

膜の形成方法、膜及び塗布液

【課題】本発明は、物体の表面の撥水性を幅広く制御することが可能な膜の形成方法、膜及び塗布液を提供することを目的とする。

【解決手段】膜の形成方法は、メラミン誘導体、メラミン誘導体と反応することが可能な官能基を有する樹脂、疎水性基を有する材料及び溶媒を含む塗布液を物体の表面に塗布する工程と、物体の表面に塗布された塗布液に含まれるメラミン誘導体と樹脂を反応させる工程を有する。

(もっと読む)

パッケージおよびその製造方法

【課題】工程時間を短縮し、平坦度(又は、ボンディングの均一性)を高め、絶縁層(絶縁基板)とチップとの間の接着力が向上したパッケージおよびその製造方法を提供することを目的とする。

【解決手段】本発明のパッケージは、パターニング層上に形成された第1導電層と、前記パターニング層上に前記第1導電層を埋め込むように形成された絶縁層と、前記絶縁層の外面に形成された第2導電層と、前記第1導電層と第2導電層とを電気的に接続するように前記絶縁層の内部に形成された第3導電層とを含むことを特徴とする。

(もっと読む)

有機珪素化合物とヒドロキシル形成化合物との反応による液状シリカ層の形成

【課題】サブミクロン素子におけるギャップ充填層、プリメタル誘電体層、インターメタル誘電体層、浅いトレンチ分離誘電体層等として使用するための低誘電率を有する酸化珪素層を均一に堆積するための方法と装置とを提供する。

【解決手段】約400℃未満の基板温度での有機珪素化合物とヒドロキシル形成化合物との反応によって低比誘電体率を有する酸化珪素層を堆積する。これらの低誘電率薄膜は、残留炭素を含んでおり、サブミクロン素子におけるギャップ充填層、プリメタル誘電体層、インターメタル誘電体層および浅いトレンチ分離誘電体層のために有用である。堆積に先立って水あるいは有機化合物からヒドロキシル化合物を調製することができる。酸化珪素層は、約3.0未満の誘電率を有するギャップ充填層を与えるために有機珪素化合物から生成されたライナー層の上に約40℃未満の基板温度で堆積されることが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

半導体装置の製造方法及びマスク

【課題】樹脂製のバンプコアの上に導電膜を形成したバンプを有する半導体装置の歩留まりを高くしつつ、バンプピッチを狭くする。

【解決手段】保護絶縁膜120上に感光性樹脂膜210を形成する。次いで、感光性樹脂膜210を露光及び現像することにより、保護絶縁膜120上に、第1の直線に沿って複数のバンプコアを形成する。次いで、複数のバンプコア上、複数の電極パッド130上、及び保護絶縁膜120上に導電膜を選択的に形成することにより、複数のバンプ、及び複数のバンプそれぞれをいずれかの電極パッド130に接続する複数の配線を形成する。そして複数のバンプコアを形成する工程において、多階調マスク50を使用して感光性樹脂膜210を1回のみ露光することにより、バンプコアの側面のうち配線に面する領域を、第1の直線と交わる領域より傾斜を緩やかにする。

(もっと読む)

ポロゲン、ポロゲン化された前駆体及び低誘電率をもつ多孔質有機シリカガラス膜を得るためにそれらを使用する方法

【課題】低い誘電率及び改良された機械的性質、熱的安定性及び化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、及びzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシラン及びオルガノシロキサンからなる群より選ばれる前駆体並びにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】複数の半導体集積回路を接続する配線の位置を容易に決定することを課題にする。

【解決手段】第1の基板上に第1の分離層と第1の半導体素子層を形成し、第1の半導体素子層に第1のレーザビームを照射することにより第1の開口部を形成し、第1の開口部に第1の半導体素子層と接続する第1の配線を形成し、第1の半導体素子層上に第1の保護材を形成し、第1の保護材に第1の配線に接続する第1の電極を形成し、第1の分離層に沿って第1の基板と第1の半導体素子層を分離し、上述の作製工程により第2の基板上に、第2の分離層、第2の半導体素子層、第2の配線、第2の保護材、第2の電極を作製し、第2の電極と第1の配線を接続するように第2の保護材上に第1の半導体素子層を貼り合わせ、第2の分離層に沿って第2の基板と第2の半導体素子層を含む積層構造を分離する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

微細構造におけるエアギャップの製造方法

【課題】化学エッチング液の膜を通じた拡散による犠牲膜材料の分解により、微細構造のエアギャップを形成する。

【解決手段】微細構造に少なくとも一つのエアギャップ35を製造する方法として、(a)犠牲材料で充填された少なくとも一つのギャップ35を備えた微細構造を提供し、前記ギャップ35は非透過性膜であるが犠牲材料を分解する性質を有する化学エッチング液の作用により透過性膜へと転換し得る膜33によりその表面の少なくとも一部分を覆われ画定される工程と、(b)膜33を透過性へと転換させ犠牲材料を分解するために前記化学エッチング液と微細構造とを接触させる工程と、(c)微細構造から化学エッチング液を除去し、前記化学エッチング液はフッ化水素酸及び/又はフッ化アンモニウムを含む流体である工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板および該シリコン基板上に設けられた低誘電率膜と配線との積層構造からなる低誘電率膜配線積層構造部を備えた半導体装置において、低誘電率膜を剥離しにくいようにする。

【解決手段】 低誘電率膜配線積層構造部3のうち配線5が配置された部分は平面方形枠状の溝6内に設けられ、その上には酸化シリコン等からなるパッシベーション膜8が設けられている。そして、溝6の内側における低誘電率膜配線積層構造部3およびパッシベーション膜8の側面は、溝6内およびその上方に設けられたポリイミド系樹脂等からなる保護膜10によって覆われている。これにより、溝6の内側における低誘電率膜4を剥離しにくいようにすることができる。この場合、溝6の外側における低誘電率膜4の側面が露出されているが、この露出された低誘電率膜4が剥離しても、保護膜10の側面が露出されるだけであり、溝6の内側における低誘電率膜4がそれに続いて剥離することはない。

(もっと読む)

半導体装置とその製造方法

【課題】コスト増を招くことなく高いインダクタンス値を得る。

【解決手段】半導体基板10にインダクタ素子40が形成される。粉末状の磁性体が分散された樹脂材で形成され、インダクタ素子40を覆う磁性樹脂体30、66を備える。また、巻き線41における配線間の隙間を埋めるように、透磁率の低い材料として非磁性の樹脂層42が製膜されている。樹脂剤42は磁性樹脂層30を形成する材料の中、磁性体が添加されない樹脂で形成される。

(もっと読む)

100%又はそれより大きい段差被覆性を有する相互接続部金属化プロセス

【課題】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法を提供すること。

【解決手段】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法が提供される。本発明の相互接続構造体は、従来のPVDプロセス、従来のイオン化プラズマ堆積、CVD、又はALDによってバリア材料が形成される従来技術の相互接続構造体と比べると、半導体業界のための改善された技術拡張性を有する。本発明によると、構造底部のバリア材料厚(ht)より厚い、構造側壁のバリア材料厚(wt)を有する相互接続構造体が提供される。すなわち、本発明の相互接続構造体において、wt/ht比は、100%に等しいか又はそれより大きい。

(もっと読む)

表面活性化剤を用いる金属含有フィルムの原子層蒸着

表面上に金属含有フィルムを形成させる原子層蒸着法が提供される。これらの方法は、これらの方法の最も広い態様において、(a)表面を表面活性化剤にさらして表面上に表面活性化錯体の蒸着物を形成させる工程と、

b)表面活性化錯体の蒸着物を金属前駆体にさらして表面上に金属錯体の蒸着物を形成させる工程と、

c)蒸着させた金属錯体を還元剤と反応させて、表面上に酸化物を含まない金属含有フィルムを形成させる工程とを含んでなり、ここで、金属はCo、Ni、Pt、Pd、IrおよびWよりなる群から選択される。

(もっと読む)

低誘電率層間絶縁膜の形成方法

【課題】 半導体装置の層間絶縁膜などとして有用な低誘電率の膜を形成する方法と、この方法により形成される膜を提供すること。

【解決手段】 基材上に膜を成長させるのに十分な化学気相成長条件下で、シリルエーテル、シリルエーテルオリゴマー又は1以上の反応性基を有する有機ケイ素化合物を含む、有機ケイ素前駆物質を反応させて、約3.5以下の誘電率を有する層間絶縁膜を形成する。

(もっと読む)

1 - 19 / 19

[ Back to top ]