Fターム[5F033SS00]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269)

Fターム[5F033SS00]の下位に属するFターム

原料ガス (1,958)

PVD(物理的気相成長法) (621)

CVD(化学的気相成長法) (4,764)

成膜の方向性制御 (10)

塗布 (1,869)

基板、導電膜からの変換 (952)

液相からの析出 (39)

Fターム[5F033SS00]に分類される特許

21 - 40 / 56

半導体基板の製造方法および半導体基板

【課題】ビア位置に形成されるパッドの平面寸法を小さくすることにより、上層の導電層における配線パターン形成の設計自由度を向上させることができる半導体基板の製造方法および半導体基板を提供する。

【解決手段】コア基板10に下層の配線パターン20を形成し、下層の配線パターン20を保護する第1の絶縁層30を形成し、第1の絶縁層30に第2の絶縁層であるレジスト40を積層し、レジスト40に上層の配線パターン80を形成するためのパターン溝42を形成した後、レジスト40に向けてレーザ光を照射し、レジスト40と第1の絶縁層30を厚さ方向に連通し下層の配線パターン20が底面に露出するビア穴60を形成し、ビア穴60内面、パターン溝42内面、レジスト40表面にシードメタル層70を形成した後、シードメタル層70上に電解めっきを行いめっき層72を形成する。

(もっと読む)

銅相互接続配線、ならびにそれを構成するための方法および機器

【課題】ガスクラスターイオンビーム処理プロセスの適用により、集積回路の相互接続構造に使用される、銅の相互接続配線層の表面上で、層をキャップ化する、改良された集積相互接続、集積回路の構造を形成する方法ならびに機器である。

【解決手段】

銅の拡散が抑制され、電気泳動寿命が向上し、選択金属キャップ化技術の使用、およびそれに付随した問題が解消される。銅のキャップ化処理、清浄化処理、エッチング処理、および膜形成処理用の、ガスクラスターイオンビーム処理モジュールを含む、各種クラスターツール構成について示した。

(もっと読む)

剥離装置

【課題】シート状の基材を貼付された基板から基材を剥離する作業を効率よく行う。

【解決手段】基板から剥離され巻き取りローラ220に巻き取られたシートフィルムFの巻き始め側端部Fsをシート剥がし爪512により引き出して把持し(図14(a))、シート剥がし機構510を下方に移動させる(同図(b))。最下端まで移動してくると従動ローラ522を配したシートガイド521を下降させて搬送ローラ531とのニップ部でシート端をクランプし、搬送ローラ531の回転により搬送経路Pに沿って回収ボックス600まで搬送する(同図(c))。

(もっと読む)

剥離装置

【課題】シート状の基材を貼付された基板の一方主面を下向きに保持したまま基材を剥離することのできる剥離装置を提供する。

【解決手段】表面にシートフィルムFが貼付されフェースダウン状態で搬入された基板Wを、吸着ステージブロック100によりフェースダウン状態のまま吸着保持する(図10(a))。巻き取りローラ220を有する巻き取りブロック200を基板Wの左下に移動させ(同図(b))、シートフィルムFの吸着を一部解除するとともに突き出しピン142により突き出すことで、端部を下方に垂れ下がらせる(同図(c))。こうして垂れ下がった端部をシートクランプ223、225によりクランプし(同図(d))、巻き取りローラ220を回転させながら右方向に移動させることにより、シートフィルムを剥離させ巻き取る。

(もっと読む)

成膜方法

【課題】低温領域で成膜しても、その膜ストレスを向上させることが可能な成膜方法を提供する。

【解決手段】被処理体Wの表面に所定の特性を有するシリコン窒化膜を形成する成膜方法において、シラン系ガスと窒化ガスとを用いて第1の温度で前記被処理体の表面にシリコン窒化膜を形成するシリコン窒化膜形成工程S1と、前記被処理体を前記第1の温度よりも高い第2の温度で窒化ガスの雰囲気下にてアニールして前記シリコン窒化膜を改質する改質工程S3とを行う。これにより、低温領域で成膜しても、その膜ストレスを向上させることが可能となる。

(もっと読む)

微細構造におけるエアギャップの製造方法

【課題】化学エッチング液の膜を通じた拡散による犠牲膜材料の分解により、微細構造のエアギャップを形成する。

【解決手段】微細構造に少なくとも一つのエアギャップ35を製造する方法として、(a)犠牲材料で充填された少なくとも一つのギャップ35を備えた微細構造を提供し、前記ギャップ35は非透過性膜であるが犠牲材料を分解する性質を有する化学エッチング液の作用により透過性膜へと転換し得る膜33によりその表面の少なくとも一部分を覆われ画定される工程と、(b)膜33を透過性へと転換させ犠牲材料を分解するために前記化学エッチング液と微細構造とを接触させる工程と、(c)微細構造から化学エッチング液を除去し、前記化学エッチング液はフッ化水素酸及び/又はフッ化アンモニウムを含む流体である工程を含む。

(もっと読む)

絶縁膜の形成方法

【課題】高誘電率ゲート絶縁膜としての使用に適し、高誘電率窒化金属シリケート膜を含んでなる絶縁膜を形成する。

【解決手段】金属原子及びシリコン原子が酸化反応を生じ難い雰囲気中にてスパッタ法によりシリコン基体101上に金属及びシリコンからなる膜102を堆積する第1の工程と、膜102を窒素プラズマを用いて窒化して窒素、金属及びシリコンからなる膜103を形成する第2の工程と、膜103を酸素プラズマを用いて酸化して窒化金属シリケート膜104を形成する第3の工程とを含む。第1の工程の終了から第2の工程の開始までの間、膜102を、その酸化反応が生じ難い雰囲気中に保持する。第3の工程により、膜104の下のシリコン基体101の表層部を酸化してシリコン酸化膜105を形成する。金属は、少なくともハフニウム及びジルコニウムのうちのいずれかを含む。

(もっと読む)

導電性クラッディング部を有する、ドープされた半導体ラインを含む集積回路

【課題】メモリセルアレイのメモリセルを選択する配線の抵抗率を低減することにより、配線中の電圧降下を低減し、消費電力を低減する半導体ラインの構造を提供する。

【解決手段】集積回路は、各メモリセルのアレイと半導体基板内に形成されたドープされた各半導体ライン202とを含む。上記ドープされた各半導体ライン202は、各メモリセルのロウに結合されている。上記集積回路は、上記ドープされた各半導体ライン202に接触している導電性クラッディング部203を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔内に配した保護部に起因する応力が小さく、接続信頼性の向上した半導体装置を提供する。

【解決手段】機能素子11を一面に配した半導体基板12、半導体基板12の一面にあって、機能素子11と電気的に接続して配した電極14、半導体基板12の他面から電極14に向けて設けた貫通孔12a、機能素子11の配した領域を除く半導体基板12の一面、及び他面と、貫通孔12aを覆うように配した絶縁層13、並びに半導体基板12の他面側に絶縁層13を介して配し、かつ貫通孔12aを覆うように配した導電部15、から少なくともなる半導体装置であって、導電部15に沿って貫通孔12a内に配した第一保護部16と、半導体基板12の他面側にあって、絶縁層13、導電部15、及び第一保護部16を覆うように配した第二保護部17とで囲まれる間隙16aを、貫通孔12a内の少なくとも電極近傍に有することを特徴とする半導体装置を提供する。

(もっと読む)

電子装置の製造方法及び電子装置

【課題】本発明は絶縁層上の導電パターンに外部接続用のバンプを設けた電子装置の製造方法及び電子装置に関し、実装信頼性の向上を図ることを課題とする。

【解決手段】電極パッド103上にバンプ104(突起部104Bを有する)を形成する工程と、半導体チップ101上に絶縁層105を突起部104Bを露出させて形成する工程と、絶縁層105上のバンプ配設領域135に応力吸収層120を形成する工程と、絶縁層105及び応力吸収層120上に第1の導電層107Aを形成する工程と、第1の導電層107Aを給電層とした電解メッキにより第2の導電層108Aを形成する工程と、第2の導電層108Aをパターニングして導電パターン106を形成する工程と、応力吸収層120上に形成された導電パターン106にはんだバンプ110を形成する工程とを有する。

(もっと読む)

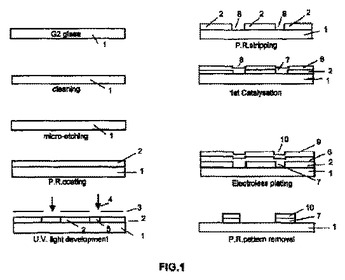

フラットパネルディスプレイの製造のための銅相互接続

フラットパネルディスプレイ相互接続システムに使用するための基板上に銅相互接続層を堆積させる方法であって、a)前記基板をフォトレジスト層で被膜する工程と、b)前記フォトレジスト層をパターン化し、前記フォトレジスト層中にパターン化された少なくとも1つのトレンチを含む、パターン化されたフォトレジスト基板を得る工程と、c)パターン化されたフォトレジスト基板上に第1の触媒層を提供する工程と、d)前記第1の触媒層上に堆積された絶縁層の無電解めっき層を設ける工程と、e)少なくとも1つのトレンチの中を除いて、連続して重ねられたフォトレジスト層、触媒層および絶縁層を除去し、第1の触媒層のパターンを、その上に堆積された絶縁層と共に得る工程を含む。  (もっと読む)

(もっと読む)

低誘電率膜の改質剤及び製造方法

【課題】 半導体デバイス製造時に使用される低誘電率膜の比誘電率を低下させるための改質剤、およびその改質剤を用いて改質された低誘電率膜を製造する方法を提供する。

【解決手段】 半導体デバイスに使用される低誘電率膜の比誘電率を低下させるための改質剤であって、一般式(1)

R3−xHxSiN3 (1)

(RはC1〜C4のアルキル基、nは0〜3の整数)で表されるケイ素化合物を有効成分として少なくとも一種類以上含有する低誘電率膜の改質剤。

(もっと読む)

集積回路デバイスとその製造方法

【課題】基板と複数のマイクロ電子デバイスを備える集積回路デバイス及びその方法を提供する。

【解決手段】少なくとも一つのマイクロ電子デバイス150に電気的に接触する導電性相互接続部を備える第1の層と、第1の層のラインに対して直角に整列された導電性のラインを備える第2の層であってかつ第2の層のラインが第1の層のラインと電気的に接触している第2の層と、第2の層のラインに対して直角に整列された導電性のラインを備える第3の層であってかつ第3の層のラインが第2の層のラインと電気的に接触している第3の層とを備え、第1の層を第2の層に相互接続し、かつ第3の層を第2の層に相互接続する複数のバイア224等を備える。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体基板の能動面に形成された金属層に付いた傷を除去することを目的とする。

【解決手段】集積回路が形成された半導体基板10の集積回路に電気的に接続された電極12を有する第1の面18に電極12を覆うように導電膜18を形成し、導電膜18上に導電膜18の一部が露出する開口20を有するようにメッキレジスト層22を形成し、導電膜18に電流を流して行う電解メッキによって導電膜18のメッキレジスト層22からの露出部上に金属層24を形成する。その後に、メッキレジスト層22を除去する。その後に、半導体基板10の第1の面16とは反対の第2の面26に樹脂層28を形成する。その後に、金属層24をマスクとして、導電膜18の金属層24からの露出部をエッチングして除去するとともにエッチングによって金属層24の表面をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体基板の能動面に形成された金属層に傷が付かないようにすることを目的とする。

【解決手段】集積回路が形成された半導体基板10の集積回路に電気的に接続された電極12を有する第1の面16に応力緩和層20を形成し、応力緩和層20及び電極12を覆うように導電膜22を形成し、導電膜22上に導電膜22の一部が露出する開口24を有するようにメッキレジスト層26を形成し、導電膜22に電流を流して行う電解メッキによって導電膜22のメッキレジスト層26からの露出部上に金属層28を形成する。その後に、メッキレジスト層26を除去する。その後に、金属層28をマスクとして、導電膜22の金属層28からの露出部をエッチングして除去する。その後に、金属層28上にソルダレジスト層30を形成する。その後に、半導体基板10の第1の面16とは反対の第2の面32に保護層34を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極のシリサイド化の際に形成された金属シリサイドに起因する短絡の発生を防止し、半導体装置の製造歩留まりを向上することができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上に、シリコンを含む配線パターンが形成され、配線パターン上に金属膜が形成される。次いで、熱処理により上記配線パターンがシリサイド化される。そして、当該シリサイド化に伴う上記配線パターンの膨張により、目的とする領域外に成長した金属シリサイドに対して、当該配線パターンの近傍に形成される導電体パターンとの短絡を防止する処理を行う。上記短絡防止は、酸化処理や除去処理により達成される。例えば、酸化処理は、フッ素と酸素とを含むガスから生成されるプラズマにより行うことができる。

(もっと読む)

半導体モジュール、携帯機器、および半導体モジュールの製造方法

【課題】放熱部に起因する信頼性の劣化が抑制され、且つ、放熱性の向上した半導体モジュールを提供する。

【解決手段】半導体モジュールは、表面Sに回路素子2の電極2aが形成された半導体基板1と、電極2aのピッチをより広くするために電極2aと接続する再配線パターン4と、この再配線パターン4と一体的に形成された電極4aと、半導体基板1の裏面Rに形成された絶縁層7と、この絶縁層7の上に形成された放熱部8と、この放熱部8と一体的に設けられ、絶縁層7を貫通して半導体基板1の裏面Rと接続する突起部8aとを備える。

(もっと読む)

半導体装置

【課題】誘電率が低く銅に対するバリア性に優れた絶縁層構造を有する半導体装置を提供する。

【解決手段】本半導体装置は、銅配線層を有する半導体装置であって、銅配線、密度2.4g/cm3以上のアモルファス炭素膜、酸化ケイ素系ポーラス絶縁材料層、密度2.4g/cm3以上のアモルファス炭素膜および銅配線をこの順に有する積層構造を少なくとも一つ有する。

(もっと読む)

樹脂層の形成方法並びに半導体装置及びその製造方法

【課題】バイトの摩耗や欠損を抑制しつつ平坦化し得る樹脂層の形成方法並びにその樹脂層の形成方法を用いた半導体装置及びその製造方法を提供する。

【解決手段】熱膨張率を低減するための混合物が含有された樹脂層34を基板10上に形成する工程であって、混合物が基板側に偏在する樹脂層を形成する工程と、樹脂層の表層部をバイト40により切削することにより、樹脂層の表面を平坦化する工程とを有している。熱膨張率を低減するための混合物が基板側に偏在する樹脂層を形成し、かかる樹脂層の表層部を切削することにより、樹脂層の表面を平坦化するため、熱膨張率を低減するための混合物によってバイトが著しく摩耗したり欠損したりするのを回避することができる。

(もっと読む)

絶縁膜の形成方法

【課題】ベースフィルムの剥離工程において、絶縁層の一部が配線層から剥離してしまうことを防ぎ、絶縁層でのリーク電流を無視できる程小さくする半導体装置の層間絶縁膜の形成方法を提供する。

【解決手段】半導体基板10上に、フォトリソグラフィで所望のレジストパターンを形成する工程、レジストパターンに基づいて、配線層となる所定の金属膜15を形成する工程、レジストパターンを保持したまま上記金属膜15上に密着層19aを形成する工程、該密着層19aに所定の熱処理を行う工程のあと、ベースフィルムに塗布形成された未架橋の高分子材料からなる絶縁層19bを加熱して押圧し、上記基板10上に層間絶縁膜19bを形成する。

(もっと読む)

21 - 40 / 56

[ Back to top ]