Fターム[5F033SS00]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269)

Fターム[5F033SS00]の下位に属するFターム

原料ガス (1,958)

PVD(物理的気相成長法) (621)

CVD(化学的気相成長法) (4,764)

成膜の方向性制御 (10)

塗布 (1,869)

基板、導電膜からの変換 (952)

液相からの析出 (39)

Fターム[5F033SS00]に分類される特許

41 - 56 / 56

半導体装置及びその製造方法

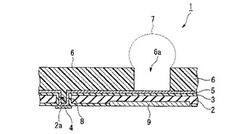

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

薄膜パターンの製造方法及びこれを用いる平板表示素子の製造方法

【課題】本発明は、フォト工程を使用しないで、段差を有する有機物パターンを形成することによって、キャパシタの容量が調節できる薄膜パターンの製造方法及びこれを用いる平板表示素子の製造方法に関する。

【解決手段】基板上に導電性第1薄膜パターンを形成するステップと、第2薄膜パターンが形成されたマスターモールドを設けるステップと、前記第2薄膜パターンが形成されたマスターモールド上に有機物を塗布するステップと、前記第1薄膜パターン及び前記基板の表面が前記有機物と接触するように前記基板と前記マスターモールドとを合着するステップと、前記有機物を硬化するステップと、前記基板とマスターモールドを分離して、前記第1薄膜パターンが形成された基板上に前記第2薄膜パターンにより段差を有することになる有機薄膜パターンを形成するステップと、を含むことを特徴とする。

(もっと読む)

樹脂層の形成方法及びめっき方法

【課題】表面の粗さが適度に設定された樹脂層を得ることができる樹脂層の形成方法、その樹脂層の形成方法を用いためっき方法及び半導体装置の製造方法を提供する。

【解決手段】樹脂より成る基材2と、基材中に分散された混合物4とを含む樹脂層32を、基板上に形成する工程と、樹脂層の表層部をバイト12により切削し、基材及び混合物のうちの一方が選択的に除去された切削面を形成する工程とを有している。表面が適度な粗さに設定された樹脂層を得ることができるため、樹脂層上に良好な密着性を有するめっき膜を形成することが可能となる。このため、高い信頼性を確保しつつ、めっき膜より成る配線を狭いピッチで形成することが可能となる。

(もっと読む)

半導体シリコン基板の製造方法およびその製造装置

【課題】超臨界状態の二酸化炭素を使用する製造方法であって、信頼性の高い半導体シリ

コン基板を与えることのできる半導体シリコン基板の製造方法を提供すること。

【解決手段】温度31〜100℃および圧力18〜40MPaの条件下、超臨界状態の二

酸化炭素の存在下に、被処理基板に対し洗浄を行なう洗浄工程、

温度150〜350℃および圧力7.5〜12MPaの条件下、導電膜および絶縁膜か

らなる群より選ばれる少なくとも一つを形成する成膜工程、

温度31〜100℃および圧力18〜40MPaの条件下、エッチングを行うエッチン

グ工程、ならびに

温度31〜80℃および圧力18〜40MPaの条件下、レジストを除去するレジスト

剥離工程、

のうち少なくとも2つの工程を有することを特徴とする半導体シリコン基板の製造方法

。

(もっと読む)

半導体装置の製造方法

【課題】容易にかつ安価に多層配線構造を構築することができる半導体装置の製造方法を提供する。

【解決手段】半導体ウェハWの薄膜担持面に、予めシートフィルムに塗布形成した金属薄膜を押し付け、該金属薄膜を転写する。その金属薄膜に凹凸パターンを型押しすることによって該パターンを転写し、エッチングによって配線1および隣接する配線1間の溝部を形成する。続いて、その上にシートフィルムに塗布形成した絶縁薄膜を押し付け、該絶縁薄膜8を転写する。そして、その絶縁薄膜8に凹凸パターン有するスタンパ31を押し付けることによって該パターンを転写する。このような転写形成による成膜、凹凸面を有するスタンパを使用したパターンニングおよびエッチングを金属層および絶縁層の双方について繰り返すことによって多層配線構造を構築する。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】 埋め込み性に優れ、誘電率の小さい絶縁膜を用い、電気的特性の優れた半導体装置の製造方法及び製造装置を提供する。

【解決手段】 真空排気したチャンバ1内に酸素ガス及び塩素ガス18を導入すると共に、プラズマアンテナ27に給電することにより、ガスプラズマ14を発生させた後、主として、ケイ素製の被エッチング部材20を塩素ガスラジカルによりエッチングして前駆体15を生成させ、温度制御手段6の調整により基板3に前駆体15を吸着させてから、塩素ガスラジカルにより前記基板に吸着した前駆体15を還元すると共に酸素ガスラジカルにより酸化してSiO2膜とする反応により、アスペクト比の大きい溝にSiO2膜を埋め込む。

(もっと読む)

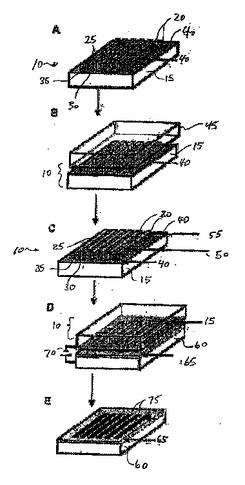

導電性コーディングされた側壁を有するナノ転写印刷スタンプを使用する方法

ナノ転写印刷法の既知の方法は、厚さ10nm未満の金属層(40)でコーティングしたスタンプ(10)を使用して、スタンプ(10)の凸部(25)から第二の表面(45)へ層(40)を転写する。本発明によれば、スタンプ(10)の側壁(35)および凹部(30)の残りの層は、材料(60)の層(65)への電荷印刷(charge print)に使用するか、または化学的測定および生物学的測定における電極として使用することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】微細なメタル配線およびヴィアホールを寸法バラツキなく形成して、寸法バラツキが低減された半導体装置を製造する方法を提供する。

【解決手段】半導体基板10上に第一のメタル配線を形成する工程、前記第一のメタル配線上に無機絶縁膜14を形成する工程、前記無機絶縁膜上に有機絶縁膜15を形成する工程、前記有機絶縁膜に凹部を形成する工程、前記凹部が設けられた有機絶縁膜上に、加熱により有機絶縁膜と反応する上層膜を形成する工程、前記上層膜を加熱処理して前記上層膜を前記有機絶縁膜と反応させ、前記凹部の側面に反応層25を成長させる工程、および、未反応の上層膜を除去し、反応層が成長したことにより縮小した凹部26を得る工程を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 ポリイミド系樹脂などの熱硬化性樹脂からなる保護膜上に強誘電体膜を有する薄膜容量素子が設けられた半導体装置において、強誘電体膜を比較的高温で形成するとき、絶縁膜が熱的ダメージを受けないようにする。

【解決手段】 ポリイミド系樹脂などの熱硬化性樹脂からなる保護膜5上に形成された下部電極8の容量素子形成領域上面に導電性接着層11を形成する。次に、導電性接着層11の上面に予め別の基板を用いて形成した強誘電体膜12を接着する。この場合、下部電極8上への強誘電体膜を有する容量素子の形成は、導電性接着層11の上面に予め別の基板に形成した強誘電体膜12を接着するだけであるので、強誘電体膜12を形成する際の処理温度が比較的高温であっても、保護膜5が熱的ダメージを受けることはない。

(もっと読む)

半導体装置およびその製造方法

【課題】 ハフニウム系高誘電体材料からなるゲート絶縁膜を用いたCMOSトランジスタのしきい値電圧を最適化する。

【解決手段】 nMOSトランジスタとpMOSトランジスタのゲート絶縁膜は、HfOX膜と、HfOX膜上に形成されたHfAlOX膜とを含んでいる。このとき、HfAlOX膜とゲート電極との界面には、ゲート電極を構成するn型多結晶シリコン膜中のシリコン原子と、HfAlOX膜中のHf原子との結合(Hf−Si結合)およびn型多結晶シリコン膜中のシリコン原子と、HfAlOX膜中のAl原子との結合(Al−O−Si結合)が生成する。そこで、HfAlOX膜中のAl濃度を変えることによって、n型多結晶シリコンの仕事関数とp型多結晶シリコンの仕事関数とがミッドギャップ(MOSトランジスタのしきい値電圧=0)を挟んで対称となるように制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】 空孔を有する低誘電率膜に配線溝やビア孔などを形成した時に、その側壁からバリアメタルや配線材料が拡散することを阻止できる半導体装置の製造方法を提供することを目的とする。

【解決手段】 基体の上に、絶縁膜を形成する工程と、前記絶縁膜に開口を形成する工程と、前記絶縁膜の前記開口の内壁面に埋込層原材料を吸着させる工程と、前記吸着させた前記埋込層原材料を加熱して埋込層を形成する工程と、前記開口を導電性材料により充填する工程と、を備えたことを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】レジストを「焦げ」の発生を防ぎつつ除去し、さらにプラズマ酸化珪素膜を半導体ウェハ内部の不純物の再分布を抑制しながら高速に形成する半導体素子の製造方法及び半導体素子を提供する。

【解決手段】レジスト301の灰化時には低めのRF電力を用いることで、レジスト301の「焦げ」の発生を防いで灰化する。レジスト301の灰化が終了した時点から高めのRF電力に切り替えることで酸化レートの高いプラズマ酸化を行い、ポリシリコンからなるN型配線部103、P型配線部104の表面に不純物の外方拡散防止膜としてのプラズマ酸化珪素膜401を形成する。熱工程を行うことなくポリシリコンをくるむようにプラズマ酸化珪素膜401を形成するため、半導体ウェハ101中の不純物を殆ど再分布させない。

(もっと読む)

半導体素子の金属配線形成方法

【課題】既存の金属配線パターンマスクを用いてダマシン工程を実施しながら層間絶縁膜の幅を最大限確保し、金属配線間の間隔を広めて相互干渉を防止することにより、半導体素子の誤動作を防止することが可能な半導体素子の金属配線形成方法を提供する。

【解決手段】絶縁膜11〜14の形成された半導体基板を提供する段階と、金属配線パターンマスクを用いたエッチング工程によって前記絶縁膜をパターニングして溝を形成するが、前記エッチング工程の際に発生するポリマーの量を制御し、パターニングされる前記絶縁膜の上部コーナー部位にラウンディング(rounding)16を形成する段階と、前記溝が埋め込まれるように金属配線を形成する段階と、このラウンディング部が除去されるようにCMP工程により全体構造上部を平坦化する段階を含む。

(もっと読む)

半導体装置

【課題】 保護膜の下に設けた配線が破損しない半導体装置を提供する。

【解決手段】 半導体装置1は、酸化シリコンからなる絶縁膜7と、窒化シリコンからなる絶縁膜8と、アルミニウムからなる配線10,11,12,13と、絶縁膜8および配線10,11,12,13を覆うポリイミド樹脂からなる保護膜14とからなり、絶縁膜8と保護膜14との間に、酸化シリコンからなる中間膜9を設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

半導体製品の製造方法

本発明は、半導体製品の製造方法に関するものである。この方法は、低k材料層を形成して、該低k材料層の中/上に導電性構造体を形成する工程と、該導電性構造体の少なくとも重複エリアにおいて、低k材料に対して範囲制限処理を施すことにより、交差領域における誘電率の値を上昇させる。これにより、高い誘電率値を有する交差領域および材料において上記導電性構造体から容量が形成される。  (もっと読む)

(もっと読む)

41 - 56 / 56

[ Back to top ]