Fターム[5F033SS13]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | CVD(化学的気相成長法) (4,764) | LPCVD(減圧CVD) (289)

Fターム[5F033SS13]に分類される特許

281 - 289 / 289

半導体装置用基板及びその製造方法、電気光学装置用基板、電気光学装置並びに電子機器

【課題】 スタックコンタクトにおける接触抵抗を抑制させる。

【解決手段】 基板と、基板上に設けられた薄膜トランジスタと、該薄膜トランジスタの上層側に設けられた配線と、該配線と薄膜トランジスタの少なくとも半導体層とを層間絶縁する層間絶縁層と、該層間絶縁層に掘られており且つ基板面上で平面的に見て長手状に延びる第1の穴、及び、夫々、第1の穴の底部から層間絶縁層を貫通して半導体層の表面に至り且つ第1の穴の長手方向に沿って配列された複数の第2の穴を含んでおり、配線と半導体層とを層間絶縁層を介して接続するコンタクトホールとを備える。

(もっと読む)

オルガノシロキサン

本発明は、少なくとも80重量%の式I:[Y0.01−1.0SiO1.5−2]a[Z0.01−1.0SiO1.5−2]b[H0.01−1.0SiO1.5−2]c[式中、Yはアリール、Zはアルケニル、aは式Iの15%−70%、bは式Iの2%−50%、cは式Iの20%−80%を表す]の化合物を含むオルガノシロキサンを提供する。本発明のオルガノシロキサンは、セラミックバインダー、高温カプセル化剤及び繊維マトリックス結合剤として使用し得る。本発明の組成物はまた別の材料と組合わせたときに優れた接着性を示すのでマイクロエレクトロニクス以外の用途またはマイクロエレクトロニクスの用途で接着促進剤として有用である。好ましくは本発明の組成物はマイクロエレクトロニクスの用途でエッチストップ、ハードマスク及び誘電体として使用される。 (もっと読む)

半導体装置の製造方法

【目的】 CVD法により形成された多孔質low−k膜上にバリアメタルを連続に形成することを目的とする。

【構成】 基体上に、有機物質原料を用いてCVD法により多孔質絶縁膜を形成するポーラスlow−k膜形成工程(S104)と、前記ポーラスlow−k膜表面に結合されるCH3基をエッチングするエッチング工程(S112)と、前記CH3基がエッチングされた前記ポーラスlow−k膜表面にALD法によりバリアメタル膜を形成するバリアメタル膜形成工程(S114)と、を備えたことを特徴とする。

(もっと読む)

ドープ窒化膜、ドープ酸化膜、およびその他のドープ膜

【課題】一般に、半導体デバイスの製造に使用される被膜、特に窒化被膜および酸化被膜を提供すること。

【解決手段】窒化シリコン、酸化シリコン、酸窒化シリコン、または炭化シリコン被膜の形成中、少なくとも1つの非シリコン前駆体(ゲルマニウム前駆体や炭素前駆体など)を添加することによって、堆積速度が改善され、または被膜の応力を調整するなどこの被膜の特性を調整することが可能になり、あるいはその両方が可能になる。また、ドープ型酸化シリコンまたはドープ型窒化シリコンまたはその他のドープ型構造では、ドーパントが存在することを利用して、このドーパントに関連する信号(目印)をエッチング・ストップとして測定することができ、またはその他の場合にはエッチング中の制御を実現することができる。

(もっと読む)

高分子膜およびその製造方法

【課題】プラズマ重合により、より低い誘電率の膜を製造する方法およびより低い誘電率の高分子膜を提供すること。

【解決手段】式(1)で示される化合物のガスを含む混合ガスを減圧下の反応室に供給する工程と、反応室内に形成されたプラズマ中を通過させることにより反応室内に設置された基板表面に前記ガスを吹き付けて、前記有機化合物を骨格に含む高分子膜を基板表面上に成長させる工程とを含む高分子膜の製造方法。該製造方法により得られる高分子膜。

(PCAは炭素原子数7以上のポリシクロ脂肪族炭化水素基。ALKは炭素原子数1〜10の二価の脂肪族炭化水素基。mは1または2。nは0または1。R1およびR2は炭素原子数1〜6のアルキル基、炭素原子数2〜6のアルケニル基、炭素原子数2〜6のアルキニル基、炭素原子数1〜6のアルコキシ基、炭素原子数6〜10のアリール基または炭素原子数6〜10のアリールオキシ基。)

(もっと読む)

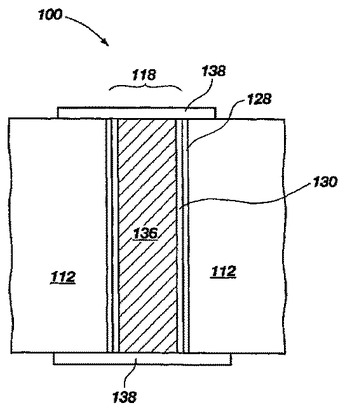

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

電子デバイス、アセンブリ、電子デバイスの製造方法

半導体基板は、共通の誘電層を有する垂直相互接続部および垂直キャパシタの両方を備えている。基板は、アセンブリを形成するために更なるデバイスと適切に組み合わせることができる。基板は、一方の面を第1のステップを含むエッチング処理で形成した後、基板の他方の面を第2のステップを含む処理で形成することができる。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

281 - 289 / 289

[ Back to top ]