Fターム[5F033SS13]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | CVD(化学的気相成長法) (4,764) | LPCVD(減圧CVD) (289)

Fターム[5F033SS13]に分類される特許

141 - 160 / 289

自己集合ナノ構造をパターン化する方法及び多孔性誘電体層を形成する方法(自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法)

【課題】 自己集合ナノ構造をパターン化しそして多孔性誘電体層を形成する方法を提供する。

【解決手段】 自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法は、1つの態様において、下側層を覆ってハードマスク層を設けるステップと、パターン化の間に保護されるべきハードマスク層の領域をフォトレジスト層により予め画定するステップと、ハードマスク層及びフォトレジスト層を覆って共重合体層を形成するステップと、共重合体層から自己集合ナノ構造を形成するステップと、自己集合ナノ構造をパターン化するためにエッチングするステップとを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】リソグラフィ処理のマージンを向上し、ゲート電極の特性劣化の虞を極力なくすことを可能とする。

【解決手段】一対の選択ゲート電極SG−SG間のほぼ中央のスペースに多結晶シリコン層4cをポリプラグとして選択ゲート電極SGと同じ幅で設けている。このため、多結晶シリコン層4a〜4cを形成するときに周期的に構成することができる。周期性の崩れを緩和することができリソグラフィ処理のマージンを向上することができる。

(もっと読む)

スペーサマスクを用いた頻度の2倍化

【課題】半導体マスクを製造する方法が記載されている。

【解決手段】最初に、犠牲マスク及びスペーサマスクを有する半導体スタックが提供される。犠牲マスクは、一連のラインを含み、スペーサマスクは、一連のラインの側壁に近接するスペーサラインを有する。次に、スペーサマスクをトリミングする。最後に、犠牲マスクを除去して、トリミングされたスペーサマスクを与える。トリミングされたスペーサマスクは、犠牲マスクの一連のラインの頻度を2倍にする。

(もっと読む)

アルミナ保護膜の配線用開口部形成方法および当該方法による半導体装置

【課題】アルミ配線上に比較的厚みの大きなアルミナ保護膜を形成して耐腐食性やヒロック防止能を向上させつつ、アルミナ保護膜を部分的に開口してアルミ配線への電気的接続を確実に行う。

【解決手段】下層アルミ配線33の表面に部分的にレジストを形成し、前記配線33の上にアルミナ保護膜35を選択的に成長させ、開口部36を持ったアルミナ保護膜35を形成する。上記レジストの除去後、前記保護膜35及び前記配線33の露出部分の上に層間絶縁膜37を形成し、アルミナ保護膜35の開口部36の上方で層間絶縁膜37をエッチングしアルミナ保護膜35の開口部36に至るスルーホール39bを形成する。スルーホール39b内と層間絶縁膜37上面に配線用アルミ材料を堆積させ層間アルミ配線40と上層アルミ配線41を形成し、層間アルミ配線40によって層間絶縁膜37の下の下層アルミ配線33と層間絶縁膜37の上面の上層アルミ配線41を接続する。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

マイクロメカニカル素子およびマイクロメカニカル素子の製造方法

本発明は、前面および後面を備えた基板を有するマイクロメカニカル素子に関する。前面は機能構造を有し、該機能構造はコンタクト領域において後面と電気的に接触接続しており、基板はコンタクト領域において少なくとも1つのコンタクトホールを有し、該コンタクトホールは後面側から基板内へと延在している。さらに本発明は、マイクロメカニカル素子の製造方法に関する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子による半導体装置の厚みの増加や立体構造による導通不良、および抵抗素子と電極との間の界面によって生じる導通性の低下などに囚われない、接続信頼性の高い抵抗素子を備えた半導体装置を提供する。

【解決手段】第一電極1を一面に備える半導体基板2、半導体基板2の一面にあり、第一電極1と整合して第一開口部を設けた第一絶縁層3、第一絶縁層3に積層し、第一開口部と連通する第二開口部を配した第二絶縁層4、前記第一開口部と、前記第二開口部と、第二絶縁層4とを覆うように配したシード層5、および第一電極1と電気的に接続し、前記第二開口部を覆うようにシード層5上に配した第二電極6、を少なくとも備える半導体装置であって、シード層5は多層をなし、少なくとも第二電極6に接したシード層5上部は第二電極6と同じパターンであり、シード層5下部は抵抗素子として機能することを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置の製造方法および半導体装置

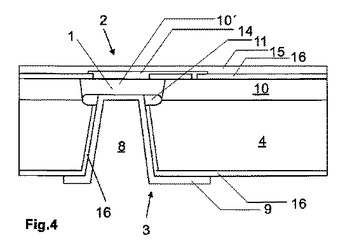

【課題】複数の積層ゲート電極間に形成される電極間絶縁膜のアスペクト比が高く電極間絶縁膜内にシームが生じたとしても当該シーム内に不要成分を侵入させることなくデバイス不良を防止できるようにする。

【解決手段】シリコン酸化膜8上で且つ多結晶シリコン層6の側面位置にシリコン窒化膜14を形成した後、多結晶シリコン層6上のシリコン窒化膜12を除去している。このため、多結晶シリコン層6の上面をウェットエッチング処理して清浄化するときにシリコン酸化膜8の中央上部にシーム8aが形成されていたとしても、当該シーム8a上を覆うようにシリコン窒化膜14がキャップ絶縁膜として形成されているため、シーム8aを拡大させることなく多結晶シリコン層6の上面を清浄化することができる。

(もっと読む)

半導体装置

【課題】トランジスタの主電極領域上のコンタクト接続不良並びに制御電極上のコンタクト接続不良を防止することができる半導体装置を提供する。

【解決手段】半導体装置(強誘電体記憶装置1)において、トランジスタ3と、強誘電体キャパシタ8とを備える。トランジスタ3の制御電極32と強誘電体キャパシタ8を被覆するバリア膜(水素バリア膜)10との間の層間絶縁膜4において、制御電極32上の第3のプラグ5(3)の上面の基板2からの高さが、第2の主電極領域34(2)上の第2のプラグ5(2)の上面の基板2からの高さに比べて高く設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層上に抵抗値の上昇が抑制されたコンタクトを備え、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10内に形成された活性領域50と、活性領域50の上面に形成されたシリサイド層45と、半導体基板10およびシリサイド層45の上に形成された第1の層間絶縁膜15と、シリサイド層45上に形成され、第1の層間絶縁膜15を貫通するコンタクトプラグ60とを備えている。コンタクトプラグ1個当たりのシリサイド層45の面積は、コンタクトプラグの面積以上、且つ、100μm2以下である。

(もっと読む)

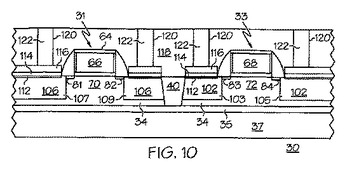

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

配線及び記憶素子の作製方法

【課題】焼成を必要とする液滴吐出法をはじめとする塗布法において、配線や導電膜の作製時における焼成温度を低減することを課題とする。

【解決手段】液滴吐出法等の塗布法を用いて導電性材料よりなるナノ粒子が分散された組成物を吐出し、その後乾燥することで該溶媒を気化させる。そして、活性酸素による前処理を行った後、焼成を行うことで、配線もしくは導電膜を作製する。このように、焼成前に活性酸素による前処理を行うことで、作製時における焼成温度を低減することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性の信頼性を向上できるようにする。

【解決手段】シリコン炭窒化膜10がシリコン酸化膜9(9a、9b)の上に形成されている。シリコン炭窒化膜10は、その比誘電率が低いため、シリコン炭窒化膜10が隣り合うゲート電極MG−MG間のシリコン酸化膜9bの内側に形成されたとしても隣り合うゲート電極MG−MG間の寄生容量を抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】被覆率としては従来と変わることなく、かつシリコン酸化膜との間で選択比の取れるシリコン窒化膜を有する半導体装置の製造方法を提供することにある。

【解決手段】半導体基板の主表面上に層間絶縁膜を形成する工程と、前記層間絶縁膜に前記半導体基板の主表面に達するコンタクトホールを形成する工程と、前記側壁にシリコン窒化膜が形成されたコンタクトホール内にTi層およびTiN層を有するバリアメタル層を形成する工程と、前記バリアメタル層が形成されたコンタクトホール内に導電層を形成する工程と、SinCl2n+2とNH3との混合ガス、またはSinCl2n−2−xとNH3との混合ガスを用い(nは2以上の自然数、xは2n+2以下の自然数)、700℃以下の成膜温度で、前記コンタクトホール内の導電層上に塩素を含有するシリコン窒化膜を形成する工程とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン型ゲートあるいはリプレース型ゲートを有する半導体装置において、ゲートパターン密度の偏りを小さくし、ダミーゲートの上面を露出させるCMP工程において、ディッシングが発生しないようにする。

【解決手段】ダマシン型ゲートあるいはリプレース型ゲートを有する半導体装置において、ゲート形成位置以外の位置14に、ダミーゲート12aを追加して配置することにより、ゲートパターン密度の偏りを小さくする。あるいはダミーゲート12aの代わりにインターフェーストランジスタ、あるいはアナログ回路用容量の電極を配置することにより、ゲートパターン密度の偏りを小さくする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】DRAMの1情報保持性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜及びゲート電極を順次形成し、前記ゲート絶縁膜及び前記ゲート電極の側部を少なくとも覆うシリコン窒化膜を形成する工程を備えた半導体装置の製造方法であって、減圧CVD法により所定の厚みのシリコン窒化物層を形成する工程と、減圧雰囲気下で前記シリコン窒化物層を窒素に暴露させる工程とを繰り返し行って、前記シリコン窒化物層を複数積層することにより、前記シリコン窒化膜を形成することを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトプラグと半導体基板との間の接触面積を十分に確保できるようにする。

【解決手段】一対の選択ゲートトランジスタのゲート電極SG間に、シリコン窒化膜11を介してBPSG膜14が形成される。BPSG膜14の上面部14aの高さ位置は各ゲート電極SGの上面部SGaの高さ位置より高さHだけ高く形成される。BPSG膜14上、ゲート電極SG上、シリコン窒化膜11上にシリコン窒化膜12が形成される。シリコン窒化膜12がシリコン窒化膜11の内側下方に延出することが無いので、一対のシリコン窒化膜11で挟まれる領域において、コンタクトホール径がシリコン窒化膜12に当接して小さくなることが無くなる。

(もっと読む)

電気光学装置及びその製造方法並びに電子機器

【課題】液晶装置等の電気光学装置において、配線の断線や容量耐圧の低下などの不具合を低減する。

【解決手段】電気光学装置は、基板(10)上に、複数の画素電極(9a)と、複数の画素電極に電気的に接続された第1導電膜(1a)と、第1導電膜の上層側に配置された第1絶縁膜(41)と、第1絶縁膜の上側表面に形成された本体部(71a)及びこの本体部から第1絶縁膜に開孔されたコンタクトホール(83)の内表面に延設された延設部(71b)を有し、第1導電膜にコンタクトホールを介して電気的に接続された第2導電膜(71)とを備える。更に、延設部上に且つコンタクトホールの内部を埋めるように形成されると共に、基板上で平面的に見て、本体部に少なくとも部分的に重ならないように形成された第2絶縁膜(610)を備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】窒化シリコン膜の成膜工程において、ポリメタルゲートの一部を構成する高融点金属の酸化物による基板の汚染を低減する半導体集積回路装置の製造技術を提供する。

【解決手段】タングステン膜を含むゲート電極7A、7B、7C上に窒化シリコン膜11を形成する際、CVD装置のチャンバ内をタングステンの酸化物が還元される雰囲気にし、チャンバ内にアンモニアを供給し続けながら、ウエハ1を600℃以上の温度で昇温する。次に、チャンバ内にアンモニアとモノシランとを供給し、これらのガスを反応させることによって窒化シリコン膜11を堆積する。次に、モノシランの供給を止め、チャンバ内にアンモニアのみを供給し続けながらウエハ1を400℃まで降温した後、チャンバ内を窒素で置換し、ウエハをアンロードする。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ間距離が十分に得られない条件であっても、キャパシタ間のショートを防止し、十分に孔径が拡大できるキャパシタの製造方法を提供する。

【解決手段】シリンダ型キャパシタ構造を有する半導体装置の製造方法であって、半導体基板上に犠牲膜(104)を形成する工程、犠牲膜をシリンダ形状にエッチング(104’)し、犠牲膜間に間隙(106)を設ける工程、前記犠牲膜間の間隙にシリンダ絶縁膜(107)を埋め込み形成する工程、前記犠牲膜を選択的に除去し、シリンダ孔(108)を形成する工程、前記シリンダ孔の内壁及び底部に下部電極を形成する工程、全面に容量絶縁膜を形成する工程、及び全面に上部電極を形成する工程を有する半導体装置の製造方法。

(もっと読む)

141 - 160 / 289

[ Back to top ]