Fターム[5F033SS13]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | CVD(化学的気相成長法) (4,764) | LPCVD(減圧CVD) (289)

Fターム[5F033SS13]に分類される特許

61 - 80 / 289

半導体装置

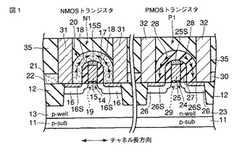

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】高さ方向に隣接するメモリセル間でワード線またはビット線を共有する構造の不揮発性記憶装置において、この不揮発性記憶装置に設けられるコンタクトを形成するための工程数を従来に比して削減することができる不揮発性記憶装置を提供する。

【解決手段】ビット線BLのいずれかに接続される複数のビット線コンタクトBCと、ワード線WLに接続される複数のワード線コンタクトWCと、を備え、ビット線コンタクトBCとワード線コンタクトWCは、複数のメモリ層の形成位置に対応するコンタクト層を貫通して形成される複数のコンタクト部81〜83と、高さ方向に隣接するコンタクト部81〜83間を接続する接続配線部41−1,41−2と、を有し、接続配線部41−1,41−2は、ビット線コンタクトBCとワード線コンタクトWCとで同じ高さのコンタクト層に形成される。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】開口不良や形状の精度に優れたコンタクトホールを有する半導体素子の提供。

【解決手段】基板4と、基板4上に第1配線パターン2と、基板4の第1配線パターン2を有する側の面に層間絶縁膜6,8と、層間絶縁膜6,8上に第2配線パターンと、を有し、且つ層間絶縁膜6,8に第1配線パターン2および第2配線パターンを連結するためのコンタクトホールCHを備え、基板4の単位面積あたりにおいて第1配線パターン2が存在する比率(密度)が、より高い領域と、より低い領域とを有し、前記比率がより低い領域におけるコンタクトホールCHの開口面積が、より高い領域におけるコンタクトホールCHの開口面積よりも小さい半導体素子。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

ジアルキルアミノ基を有する気相成長用シリコン原料及び当該材料を用いたシリコン含有薄膜の製造方法

【課題】 本発明の課題は、取り扱いが容易で、且つ酸化的熱分解が起こり易いジアルキルアミノ基を有する気相成長シリコン原料を提供することにある。

【解決手段】 本発明の課題は、ジアルキルアミノ基を有する気相成長用シリコン原料によって解決される。

(もっと読む)

不揮発性記憶装置

【課題】第1の配線と第2の配線との交差部に整流素子と不揮発性記憶素子を有する不揮発性記憶装置で、従来に比して高さを抑えることができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するビット線BLと、ビット線BLとは異なる高さに形成され、第2の方向に延在するワード線WLと、ビット線BLとワード線WLとが交差する位置にビット線BLとワード線WLの間に挟持されるように配置される抵抗変化型メモリセルと、を備え、抵抗変化型メモリセルは、抵抗変化素子20がN型半導体層10とP型半導体層30で挟まれた構造を有する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

貫通電極で貼り合わせた300mmウエハと半導体装置

【課題】ウエハを貫く貫通電極でウエハ上のデバイスを接続し、ウエハを貼り合わせて高集積で高機能の半導体装置を製造するとき、貫通電極とウエハを絶縁分離する工程とバンプを形成する工程、バンプを接続する工程があった。これらの工程を省きチップを積層した半導体装置の原価を低減することが課題であった。

【解決手段】ウエハを貫くリング状の孔にシリコン酸化膜を埋め込み、これの中の貫通電極を形成することでウエハと貫通電極を絶縁分離した。この方法で工程数が少なくなった。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

固体撮像素子

【課題】パッケージの端子数を増やさず、遮光膜の電位を固定する。

【解決手段】複数の画素が配列された画素部20が形成された半導体基板1と、半導体基板1において、光入射面の反対側の面に形成され、画素部20の駆動用信号線を含む配線3が形成された配線層13と、半導体基板1の光入射面に形成され、複数の画素のうち黒信号を決めるための暗画素を遮光する遮光膜5とを備える。配線層13に形成された、配線3の一部であるパッド6と、暗画素としてのフォトダイオード2Aを遮光する遮光膜5とが配線10により電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

成膜方法および半導体装置の製造方法

【課題】誘電率が低くかつエッチング耐性に優れた窒化シリコン系絶縁膜を形成する。

【解決手段】基材上にシラン系ガス(DCS)、窒化性ガス(NH3)及びホウ素含有ガス(BCl3)を、N2パージを逐次行いながらこの順で供給してホウ素含有窒化シリコン層を形成する工程と、このホウ素含有窒化シリコン層に、プラズマにより活性化された窒化性ガス(活性化NH3)を供給する工程とを含み、これらの工程をこの順で繰り返し行う成膜方法。

(もっと読む)

半導体装置の製造方法

【課題】本発明は多層配線構造を有する半導体装置の製造方法に関し、高い集積度が要求される場合に優れた歩留まりと高い信頼性とを確保することを目的とする。

【解決手段】トランジスタのソースドレイン領域の上層にシリコン酸化膜7を形成する。一端面がソースドレイン領域6に導通し、他端面がシリコン酸化膜7の表面に露出するように、シリコン酸化膜7の内部に導電性のパッド10を設ける。シリコン酸化膜7およびパッド10の上層にシリコン酸化膜11を形成する。一端面がパッド10に接触し、他端面が配線層14と導通するようにシリコン酸化膜11の内部にプラグとして機能する導電層を設ける。シリコン酸化膜7の表面と、パッド10の他端面は平滑な同一平面を形成する。プラグとして機能する導電層は、パッド10に比して小さく、かつ、パッド10の中央部近傍に接触するように形成する。

(もっと読む)

半導体素子の製造方法

【課題】柱状残渣の発生を抑制した半導体素子の製造方法の提供。

【解決手段】基板12上に配線層14を形成する工程と、基板12および配線層14を覆うように、第3絶縁膜22、第2絶縁膜(SiN膜)24、および第1絶縁膜(PSG膜)26を順に積層した層間絶縁層20を形成する工程と、第1絶縁膜26上にマスクパターンを形成する工程、ウェットエッチング処理によって第1絶縁膜26のコンタクトホール30形成部分を除去する工程、少なくとも等方性ドライエッチングを含むエッチング処理によって第2絶縁膜24のコンタクトホール30形成部分を除去する工程、およびエッチング処理によって第3絶縁膜22のコンタクトホール30形成部分を除去する工程、を経て配線層14表面が露出するよう層間絶縁層20にコンタクトホール30を形成する工程と、を有する半導体素子10の製造方法。

(もっと読む)

61 - 80 / 289

[ Back to top ]