Fターム[5F033SS13]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | CVD(化学的気相成長法) (4,764) | LPCVD(減圧CVD) (289)

Fターム[5F033SS13]に分類される特許

21 - 40 / 289

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、被加工材にパターンを形成するためのマスクの選択比を向上させ、プロセスコストの低減、歩留りの向上を可能とする。

【解決手段】被加工材上に所定パターンの有機膜を形成し、所定パターンの有機膜中に金属元素を導入し、金属元素が導入された所定パターンの有機膜を用いて、被加工材をエッチング処理する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

抵抗回路を有する半導体装置

【課題】高抵抗・高精度の抵抗素子からなる抵抗回路を提供する。

【解決手段】500Å以下に薄膜化した薄膜材料からなる抵抗素子の上にシリコン窒化膜などの絶縁膜を形成する。この窒化膜により抵抗素子に対するコンタクトホールの突き抜けを防止する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

二酸化ケイ素膜の製造方法

【課題】低収縮かつ低応力である絶縁膜を製造することができる方法の提供。

【解決手段】基板表面にポリシラザン組成物を塗布して塗膜を形成させ、引き続き前記塗膜を過酸化水素雰囲気下、50〜200℃で加熱することを含んでなることを特徴とする、二酸化ケイ素膜の製造方法。この二酸化ケイ素膜の製造方法によって各種絶縁膜などのアイソレーション構造を形成させることができる。

(もっと読む)

半導体装置の製造方法

【課題】SOD法によって形成するシリコン酸化膜に、ボイドが発生することを抑制する。

【解決手段】基板、基板表面に形成された溝状領域G、及び溝状領域Gに埋設されたシリコン酸化膜8を有する半導体装置の製造方法であって、溝状領域Gを含む基板の表面を覆うライナー膜6を形成するライナー膜形成工程と、ライナー膜6の表面を水洗する水洗工程と、水洗後の残留水分を除去する水分除去工程と、基板表面にポリシラザン溶液をスピンコートにより塗布する塗布工程と、アニールによりポリシラザン溶液をシリコン酸化膜8に改質する改質工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いる配線形成方法で、特に最上層の配線を含む上層配線を形成する場合、接続孔の周囲に生ずるクラウンフェンスを容易に除去して信頼性の高い半導体装置を提供する。

【解決手段】 接続孔19a、19b上に形成された開口を有するマスク層21をマスクとして、第3絶縁膜17および第3絶縁膜17より密度の小さい、あるいは比誘電率が小さい第2絶縁膜16をエッチングして配線溝22を形成すると、接続孔19bに埋め込まれた有機性材料20の突出部と同時に、第2絶縁膜16の構成材料を主成分とするクラウンフェンス23が生ずる。これに対しマスク層21の除去工程を兼ねるなどの処理において、少なくとも配線溝22の内部にプラズマ処理を施した後、第2絶縁膜16を溶解可能な処理液で処理し上記のプラズマ処理で変質したクラウンフェンス25を選択的に除去する。

(もっと読む)

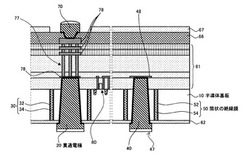

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

21 - 40 / 289

[ Back to top ]