Fターム[5F033TT07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | コンタクトホールの側壁 (799)

Fターム[5F033TT07]に分類される特許

781 - 799 / 799

半導体装置及びその製造方法

【課題】 配線間の絶縁膜を可能な限り除去して十分に低誘電率化を図り、エアギャップ形成時に配線にダメージを与えない構造を設けることで信頼性を向上させた半導体装置を提供する。

【解決手段】 複数の配線を内部に形成した絶縁膜6の上下層に当該絶縁膜6よりウェットエッチング耐性が高い絶縁膜5,9を形成してなる配線層部と、絶縁膜6よりウェットエッチング耐性が高い材料からなり、配線を被覆するようにその周囲に形成された絶縁膜7と、上下層の絶縁膜5,9及び絶縁膜7と配線が内部に形成された絶縁膜4とのエッチング耐性の違いに基づいて、上下層の絶縁膜5,9及び絶縁膜7で囲まれた配線間の絶縁膜4を選択的にエッチング除去してなるエアギャップ部12とを備える。

(もっと読む)

貫通孔形成方法、半導体装置及びその製造方法

【課題】 {100}シリコン基板からなる半導体基板の表裏面を電気的に接続する、半導体基板に対して垂直な貫通孔を、非常に容易な方法で形成する。

【解決手段】 表面に保護膜が形成された{100}シリコン基板に、保護膜を取り除くことにより所定の領域以上の大きさの半導体表面開口部を形成し、開口部にレーザ加工により、所定の領域よりも小さい内径の貫通孔を形成した後、貫通孔を異方性エッチングによって内径を拡大し、内径が該所定の大きさになった時に該エッチングを終了する。これにより基板表面より貫通孔内面に向かって逆テーパ形状の{111}結晶面を析出する事なく所定の大きさの貫通孔を形成することができるとともに、レーザ加工によって加工孔周囲および内部に発生するドロスやデブリス等を消滅させ、かつ貫通孔内面が非常に滑らかな結晶面で形成された、高品位の貫通孔を実現する事が可能である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

半導体装置及びその製造方法

【課題】 工程を複雑にすることなく実装の際の強度及び精度を向上させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】 ダイシングラインDLに沿って半導体基板10の裏面に溝14を形成する。さらに半導体基板10の裏面からパッド電極11に到達するビアホール16を形成する。そして、ビアホール16内に埋め込み電極18を形成し、それと接続してダイシングラインDL近傍に延びる配線層19を形成する。配線層19の端部には導電端子21を形成する。そして、ダイシングラインDLに沿ったダイシングにより、裏面の端部に傾斜面1sを有した半導体装置1が完成する。半導体装置1がリフロー処理により回路基板30に接続される際、流動性の増した導電性ペーストが、導電端子21及び傾斜面1sを覆う。ここで、半導体装置1の外縁における回路基板30上には、サイドフィレットを含む導電性ペースト40a,40bが形成される。

(もっと読む)

半導体チップの製造方法および半導体装置の製造方法

【課題】 貫通電極用の貫通孔の形成時間を短縮化することで生産性を向上させた半導体チップの製造方法を提供する。

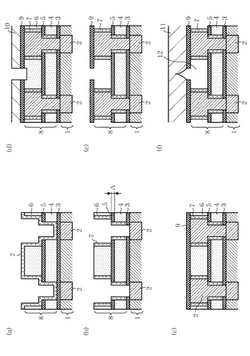

【解決手段】 まず、第1の絶縁膜3をマスク部材としてシリコン基板1の上面側に第1のトレンチ7aを例えばボッシュプロセスを用いて形成する。次に、第2の絶縁膜5をマスク部材としてシリコン基板1の裏面側に、第1のトレンチ7aに連通する第2のトレンチ7bを同じくボッシュプロセスを用いて形成する。そして、これにより形成された貫通孔8内に絶縁膜を形成した後、その貫通孔8内に導電性材料を充填して貫通電極2を形成する。

(もっと読む)

基板をエッチングするための方法及び装置

本方法及び装置は、化学式CaFbを有する第1のガス及び化学式CxHyFzを有する第2のガスの混合物(ただし、a/b≧2/3、x/z≧1/2である)に基づくプラズマの使用を通して半導体及び誘電体基板をエッチングするために提供される。この混合物は、磁気的に増強された反応性イオンチャンバ内に維持された低または中密度プラズマにおいて用いられ、優れたコーナー層の選択性、ホトレジストの選択性、下層の選択性及びプロファイルと底部のCD制御を示すプロセスを提供する。第1と第2のガスのパーセンテージは、ドープされない酸化物膜をエッチングするプラズマまたはこのような膜上でエッチング停止を与えるために、エッチング中に変えることができる。  (もっと読む)

(もっと読む)

ウエハレベルチップスケールパッケージ製造方法

【課題】パッケージスタック用ウエハレベルチップスケールパッケージを製造する方法を提供する。

【解決手段】第1面35及び第2面39と、前記第1面にチップパッドを有する複数の集積回路チップ34と、前記集積回路チップ間を走るスクライブレーン36とを有するウエハ30を備える段階と、前記ウエハの第1面に前記チップパッドを貫通する孔を形成する段階と、前記ウエハの第1面に前記孔の内面を覆うベース金属層41を形成する段階と、前記孔を充填して前記チップパッドに電極金属層42を形成する段階と、前記ウエハの第2面を研磨し、前記電極金属層を前記ウエハの第2面を介して露出する段階と、前記ウエハ第2面を介して露出した前記電極金属層にメッキバンプ43を形成する段階と、前記電極金属層間に位置するベース金属層を除去する段階と、前記スクライブレーンに沿って前記ウエハを分離する段階とを含む。

(もっと読む)

半導体装置及びその製造方法

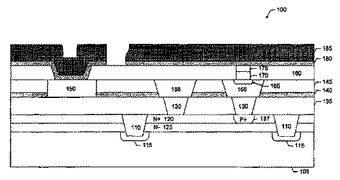

【課題】 多孔質絶縁膜を含む層間絶縁膜の誘電率を実効的に低減させ、微細で高信頼性のダマシン配線を有する半導体装置の実用化を容易にする。

【解決手段】 下層配線1上に多孔質の第1低誘電率膜2bを含む第1層間絶縁膜2が形成され、第1層間絶縁膜2に設けられたビアホール3内にその側壁に設けられた第1側壁保護膜4を介して第1バリア層5およびビアプラグ6が形成される。同様に、多孔質の第2低誘電率膜7bを含む第2層間絶縁膜7のトレンチ8内にその側壁に設けられた第2側壁保護膜9を介して第2バリア層10および上層配線11が形成される。ここで、第1側壁保護膜4および第2側壁保護膜9は多孔質の低誘電率膜で成り、その空孔の含有率は30%以下であり、空孔の寸法は2nm以下である。

(もっと読む)

改善された二重ダマシン集積構造およびその製造方法

ガスクラスターイオンビーム処理を用いた多孔質超低k値(ULK)絶縁体材料内に二重ダマシン構造を形成する方法に関して開示する。これらの方法においては二重ダマシンULK処理中におけるハードマスク層を最小にし、最終的なULK二重ダマシン構造内には、ハードマスク層が存在しない。ガスクラスターイオンビームのエッチング処理、緻密化処理、孔のシーリング処理、アッシング処理の各方法が記載されており、該方法は、材料の除去と同時にULKインターフェースの緻密化を進行させる。緻密なインターフェースとハードマスクがない新規なULK二重ダマシン構造が含まれている。 (もっと読む)

レジスト剥離中における多孔質低誘電率材料の損傷を阻止する方法

【課題】レジスト剥離中における多孔質低誘電率材料の損傷を阻止する。

【解決手段】多孔質低誘電率層内に形状を形成する方法が提供される。先ず、基板の上に、多孔質低誘電率層が配される。次いで、多孔質低誘電率層の上に、パターン形成されたフォトレジストマスクが配される。次いで、多孔質低誘電率層内に、形状がエッチングされる。形状のエッチング後は、形状の上に保護層が成長される。そして、保護層の一部が除去されるように、パターン形成されたフォトレジストマスクが剥離され、形状内に、保護層で形成された保護壁を残留させる。

(もっと読む)

多孔質絶縁膜及びその製造方法並びに多孔質絶縁膜を用いた半導体装置

半導体装置を構成する絶縁膜として有効な多孔質絶縁膜の作製方法、該絶縁膜の上下界面に接する半導体材料と高い密着性を有する多孔質絶縁膜の作製方法を提供。

少なくとも一つ以上の、分子中に環状シリカ骨格を有し且つ該環状シリカ骨格に少なくとも一つ以上の不飽和炭化水素基が結合されている有機シリカ化合物の分子蒸気、を含む気体をプラズマ中に導入し、半導体基板上に多孔質絶縁膜の成長を行う。

(もっと読む)

低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体

【課題】 低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体を形成すること。

【解決手段】 調節可能で自己整合型の低静電容量集積回路のエアーギャップ構造は、相互接続層上で第二相互接続部に隣接する第一相互接続部と、該第一相互接続部及び該第二相互接続部の隣接する側部に沿って形成されたスペーサと、該第一相互接続部と該第二相互接続部との間に形成されたエアーギャップとを含む。エアーギャップは、第一相互接続部及び第二相互接続部の少なくとも一方の上面より上方で、かつ、該第一相互接続部及び該第二相互接続部の少なくとも一方の下面より下方に延び、スペーサ間の距離が該エアーギャップの幅を定める。エアーギャップは、第一相互接続部及び第二相互接続部の隣接する側部に自己整合する。

(もっと読む)

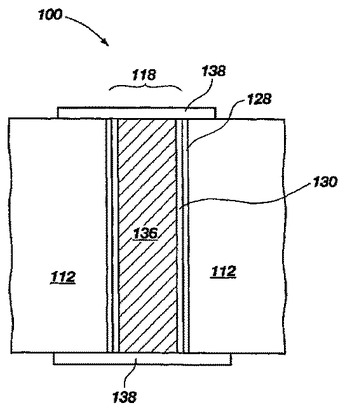

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

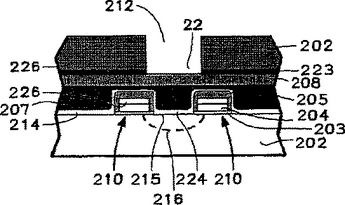

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

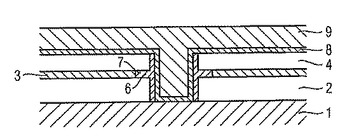

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

集積回路デバイス内の相互接続構造体

【課題】 フォトレジスト汚染の問題に悩まされないデュアル・ダマシン構造体を形成する方法を提供すること。

【解決手段】 本発明は、集積回路デバイス内のデュアル・ダマシン相互接続構造体の製造に関する。具体的には、平坦化材料及び拡散障壁材料を用いて、低kの誘電体薄膜内にシングル又はデュアル・ダマシン構造体を形成するための方法が開示される。この方法の好ましいデュアル・ダマシンの実施形態において、最初に誘電体材料にビアを形成し、次にビア内及び誘電体材料上に平坦化材料を付着させ、平坦化材料上に障壁材料を付着させる。次に、リソグラフィにより像形成材料にトレンチが形成され、障壁材料を通して平坦化材料がエッチングされ、トレンチ・パターンが誘電体材料に転写される。これらのエッチング・ステップの過程の間及び該エッチング・ステップの過程に続いて、像形成材料、障壁材料及び平坦化材料が除去される。次に、結果として得られるデュアル・ダマシン構造を金属化することができる。この方法を用いる場合、層間誘電体材料によるフォトレジスト汚染の問題が軽減される。

(もっと読む)

電子デバイス、アセンブリ、電子デバイスの製造方法

半導体基板は、共通の誘電層を有する垂直相互接続部および垂直キャパシタの両方を備えている。基板は、アセンブリを形成するために更なるデバイスと適切に組み合わせることができる。基板は、一方の面を第1のステップを含むエッチング処理で形成した後、基板の他方の面を第2のステップを含む処理で形成することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

781 - 799 / 799

[ Back to top ]