Fターム[5F033UU01]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445)

Fターム[5F033UU01]の下位に属するFターム

Fターム[5F033UU01]に分類される特許

281 - 300 / 300

半導体装置及びその製造方法

【課題】層間絶縁膜の凹凸の緩和にSOG膜が利用され、かつ段違いにホールが接近して形成される場合でも回路配線に信頼性が得られる半導体装置及びその製造方法を提供する。

【解決手段】コンタクトホール12とビアホール15の平面的な離間距離D1は、1μm以下の最小スペースとなっている。周辺回路領域に隣り合うメモリセル領域の境界に沿って第1層目金属配線層によるダミーパターン18が形成されている。このダミーパターン18は、SOG膜塗布時、その膜流動性によりメモリセル領域側に過剰に移動しようとするのを塞き止める。これにより、凹凸の密なメモリセル領域へのSOG膜の塗布に関し、メモリセル領域内部と最外周とで残り方が変わらないようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置が微細化しても細線効果による性能低下を抑制できる、高集積化に適した新たな3次元半導体装置及びその製造方法を提供することである。

【解決手段】 上記課題を解決した半導体装置は、半導体層中にこの半導体層表面に垂直に形成されたトレンチと、前記トレンチの側面及び底面の前記半導体層中に形成され、前記トレンチの深さ方向に形成された複数の素子分離と、前記トレンチの側面に沿って形成され、絶縁膜と電極とを備えた複数の機能素子と、前記電極に接続し、前記複数の機能素子を第1の方向に接続する第1の配線と、前記トレンチの側面及び底面の前記半導体層中に形成され、前記素子分離により分離され、前記機能素子を前記第1の方向は異なる第2の方向に電気的に接続する第2の配線とを具備する。

(もっと読む)

半導体チップ

【課題】 最終配線プロセス完了後でも例えばSRAMセル内の特定部分について位置を同定し、解析を行なうことが可能なダミーパターンを有する半導体チップを提供する。

【解決手段】 最上層の導体配線層の少なくとも一部分に、化学機械研磨法により平坦化を行なう際に生じるディッシングを抑えるためのダミーパターンのみからなる領域を有しており、前記ダミーパターンは前記最上層の導体配線層よりも下層に位置する半導体素子の特定の位置を提示するようレイアウトされている。ダミーパターンを観察することで、半導体チップ内のSRAMの特定部分を観察することができる。

(もっと読む)

半導体集積回路装置

【課題】 平坦化処理に支障の少ないダミーメタル配置形状の半導体集積回路装置を提供する。

【解決手段】 本発明にかかる半導体集積回路装置は、マクロセル、または、IOセルの少なくとも1つのセルを有する半導体集積回路装置であり、マクロセル、または、IOセルの周辺に挿入されるダミーメタルが、段階的にメタル占有率が変更されてなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜の高い平坦性を有する半導体装置を製造する方法を提供することを主要な目的とする。

【解決手段】 下層配線3および上層配線10が層間絶縁膜4を介在させて設けられ、かつ下層配線3と上層配線10がビアホールプラグ8aを介して電気的に接続されている半導体装置の製造方法にかかる。下層配線3を覆うように半導体基板1の上に層間絶縁膜を4形成する。層間絶縁膜4中に、下層配線3の表面を露出させるビアホール6aを形成し、同時に、ビアホール6aの存在しない層間絶縁膜4の領域に、下層配線3の深さに到達しない、ダミービアホール7aを、ビアホール6aが形成される領域から、徐々にその密度を減少させて形成する。ビアホール6aとダミービアホール7aを埋め込むように金属層8を半導体基板1の上に形成する。半導体基板1上を研磨して、ビアホールプラグ8aとダミービアホールプラグ8bを形成する。ビアホールプラグ8aに接触するように上層配線10を形成する。

(もっと読む)

論理変更用回路及びこの論理変更用回路を有する半導体装置

【課題】リーク電流の発生を抑制することにより、消費電力の低減を可能とした論理変更用回路及びこの論理変更用回路を有する半導体装置を提供する。

【解決手段】論理回路の論理構成の変更に用いる論理変更用回路及びこの論理変更用回路を有する半導体装置において、論理変更用回路には論理構成の変更に用いる論理素子を設け、この論理素子には、電源配線またはグランド配線を接続可能とする接続配線を接続し、論理素子を使用する場合には、接続配線と電源配線とをコンタクトを介して接続し、論理素子を使用しない場合には、接続配線とグランド配線とをコンタクトを介して接続した。

(もっと読む)

半導体装置

【課題】 半導体装置において、クラックによるシールリング破壊をより効率良く強力に防止することができるようにする。

【解決手段】 半導体装置は、比誘電率が3.5未満の低誘電率膜を含む半導体装置であって、平面的に見て閉ループ形となる水分遮蔽壁であるシールリング123を1本以上備え、シールリング123のうち少なくとも1本は、チップコーナー4近傍において内向きに凸形状になるシールリング凸形部10を含む。

(もっと読む)

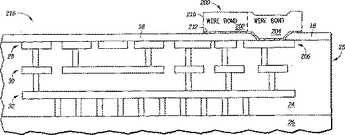

ボンディングパッドを有する半導体装置及びその形成方法

ボンディングパッド(200)は第1ワイヤボンディング領域(202)と、第2ワイヤボンディング領域(204)と、を含む。一実施形態では、第1ワイヤボンディング領域(202)がパッシベーション(18)を覆って延びる。別の実施形態では、ボンディングパッドはプローブ領域、第1ワイヤボンディング領域、及び第2ワイヤボンディング領域を有する。一実施形態では、プローブ領域及びワイヤボンディング領域がパッシベーション(18)を覆って延びる。ボンディングパッドはどのような数のワイヤボンディング領域及びプローブ領域も有することができ、かつこれらの領域をどのような構成として有することもできる。ボンディングパッドが複数のワイヤボンディング領域を含むことができるので、マルチチップパッケージにおける場合のように単一のボンディングパッドへの複数のワイヤ接続を行なうことができる。ボンディングパッドがパッシベーションを覆って延びる形でパッドを設けることができるので、集積回路チップ面積を小さくすることもできる。  (もっと読む)

(もっと読む)

半導体装置並びにそのパターン設計方法及びパターン設計用プログラム

【課題】 均一性の高い被覆率を有するダミーパターン形成方法及び均一性の高い被覆率を有する半導体装置を提供することを目的とする。

【解決手段】 ダミーパターン形成領域を複数のダミーパターン形成ユニット領域に分割し、次にダミーパターン形成ユニット領域よりも大きな面積を有する検査範囲を、各検査範囲の一部がそれぞれオーバーラップするように複数の検査範囲を設定し、続いて検査範囲内のダミーパターン形成ユニット領域内に形成するダミーパターンの仮パターン被覆率を算出し、算出された仮パターン被覆率を平均化処理して最終パターン被覆率を算出し、最終パターン被覆率に相当する面積を有するダミーパターンをダミーパターン形成ユニット領域内にパターンとして発生させる。

(もっと読む)

半導体装置

【課題】 集積度の向上が容易な半導体装置を提供する。

【解決手段】 活性領域4aには、nMOSトランジスタ10の1対のソース/ドレイン領域11、11が形成されている。1対のソース/ドレイン領域11、11に挟まれる半導体基板の領域上にゲート酸化膜を介してゲート電極層13が形成されている。ゲート電極層13は、活性領域4a上および素子分離構造上の双方に延在し、かつ素子分離構造上にコンタクトパッド部13aを有し、かつ活性領域4aとコンタクトパッド13aとの平面的な間隔S1が0.5μm未満である。

(もっと読む)

半導体ウエハおよび半導体装置の製造方法

【課題】

従来、半導体ウエハのダイシングに先立ち、レーザ照射によってスクライブライン上の層間絶縁膜を除去する際に、同じくスクライブライン上に配置されたアクセサリパターンに含まれる金属が飛散し、電極パッドを汚染していた。

【解決手段】

ダイシングに先立ちレーザ照射する必要がある程度に細いスクライブライン上であって、電極パッドに隣接する部分には金属を含むアクセサリパターンを配置しないようにした。また、金属を含むアクセサリパターンを配置したスクライブラインであって、所定の幅以下のスクライブラインには、ダイシングに先立つレーザ照射を行わないようにした。

(もっと読む)

配線パターン作成装置、配線パターン作成方法、配線パターン作成プログラムおよび記録媒体

【課題】簡単かつ最適な配線パターン処理をおこなうことにより、後工程での配線パターンの修正を防止し、LSIの歩留まりの向上を図ること。

【解決手段】完全グラフは、配線パターンWiに対応するノードNiと、配線パターン間の影響度に対応するエッジeijとから構成されている。異なるグループGmどうしの配線パターン間におけるクロストークの影響度Fijの総和Σが最小となるように、配線パターンの集合を複数のグループに分ける。完全グラフでは、エッジe12、e13、e23、e45の影響度が高く、残余のエッジe14、e15、e24、e25、e34、e35の影響度は、エッジe12、e13、e23、e45の影響度に比べて低い値とされている。これにより、エッジによって互いに連結されているノードN1〜N3のグループと、ノードN4、N5のグループとに分割される。

(もっと読む)

導体におけるジュール加熱と電流密度間の関係を確立するための方法及びシステム

例示的な一実施形態に従って、導体におけるジュール加熱とこの導体における電流密度間の関係を確立するための方法がウェーハレベル測定(500)を実行することによって実装される。この実施形態に従って、導体(118,)における抵抗の温度係数を得るためにウェーハレベル測定が実行される(ステップ502)。本方法は、又、導体の熱抵抗を判断することを含む(ステップ510)。この熱抵抗は、その後導体におけるジュール加熱と導体における電流密度間の関係を確立するために利用される(ステップ512)。そのようにして得られた関係は、その後、信頼性のある半導体デバイス設計において補助するために設計ルール、平均故障時間、及び他の情報を判断するために利用される(ステップ514)。もう1つの実施形態に従って、ウェーハレベル測定システム(100)が導体におけるジュール加熱と導体における電流密度間の関係を確立するために利用される。  (もっと読む)

(もっと読む)

2つのチップコンタクト群を備えるチップ

チップ(1)は、基板(2)と、基板(2)上に設けられた集積回路(3)と、複数の導体領域(ME1、ME2、ME3、ME4、ME5)と、導体領域および集積回路を保護するために設けられた保護層(5)とを備え、保護層(5)にはスルーホール(6、7)が設けられ、それらを介してチップコンタクト(8、9)がアクセス可能であり、追加のチップコンタクト(10、11)および接続導体(12、13)が保護層(5)上に設けられ、各追加のチップコンタクトが、接続導体を介したチップコンタクトとの導電接続部を有する。  (もっと読む)

(もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

減少されたコンタクト高さでのバイポーラ及びCMOSの集積回路構造体

【課題】 複数の高さのデバイスを含む集積回路構造体であって、このようなデバイスに形成されたコンタクトの高さを減少させるために保護層の高さを減少させた、改善された構造体を提供すること。

【解決手段】 単一の基板上に配置された複数の相補型金属酸化膜半導体(CMOS)トランジスタ及び複数の垂直バイポーラ・トランジスタを含む集積回路構造体のための方法及び構造体が開示される。垂直バイポーラ・トランジスタは、CMOSトランジスタより高さのあるデバイスである。この構造体においては、保護層が、基板の上に、及び、垂直バイポーラ・トランジスタとCMOSトランジスタとの間に配置される。配線層は保護層の上にある。垂直バイポーラ・トランジスタは、配線層と直接接触しており、CMOSトランジスタは保護層を通って延びるコンタクトによって配線層に接続されている。

(もっと読む)

斜めストライプを有するパワーグリッド構造を形成するための方法及び装置

【課題】集積回路で使用される斜めストライプを有するパワーグリッド構造を形成するための方法及び装置を提供する。

【解決手段】斜め電力ストライプ及び斜め接地ストライプを有するICのパワーグリッド構造を規定して生成する方法。ストライプが、得られるICの下部境界に対して45°又は135°の斜め方向に配置されることになるように、ストライプは、ICレイアウトのx座標軸に対してそれぞれ45°又は135°の斜め方向に配置される。斜めの電力及び接地ストライプは、斜め信号配線に有益である。ストライプは、ICの一つの層に亘って又はICの一つよりも多い層に亘って配置することができる。斜め電力ストライプは、ICの層上に様々な幅及び/又は様々な間隔幅を有することができる。斜め接地ストライプも、ICの層上に様々な幅及び/又は様々な間隔幅を有することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下層におけるクラックの発生を抑制しつつ、ボンディングパッドの下層を有効活用して装置の小型化を図る。

【解決手段】半導体装置10は、半導体基板11と、外部との電気的接続をとるための接続領域12aを有するボンディングパッド12と、半導体基板11とボンディングパッド12との間に介在する第1層間絶縁層13と、第1層間絶縁層13に埋設されたメタル配線層14とを備える。メタル配線層14は第1層間絶縁層13より硬度の小さい材質からなる。メタル配線層14の少なくとも一部は、積層方向において接続領域12aと重なり、接続領域12aと重なるメタル配線層14の領域には、積層方向に貫通し、メタル配線層14をその層方向において分離している切欠部30a〜30eが形成されているとともに、この切欠部30a〜30eに第1層間絶縁層13の一部が埋め込まれている。

(もっと読む)

信号バス配置

【課題】 バスのピッチ幅を広くすることなく信号線間のクロストークノイズを低減する。

【解決手段】 2次元レイアウトにおいて、隣接信号線BUS_A<0:L>およびBUS_B<0:M>は、異なるバスに属するする信号線となるようにバス信号線を配置する。異なるバスは、それぞれ異なるタイミングで変化する信号を伝達し、同一バス内の信号線は実質的に同一タイミングで変化する信号を伝達する。

(もっと読む)

多層配線基板及び半導体装置

【課題】エミッタ配線からバイアホール、サーマルビアを介して多層配線基板下面につながる放熱経路の熱抵抗を低減し、半導体装置全体の熱抵抗を低減すること。

【解決手段】厚さ方向に貫通孔4を有する多層配線基板3において、多層配線基板3に実装される半導体基板1がその厚さ方向に貫通孔5を有し、かつ、多層配線基板3及び半導体基板1の厚さ方向と直交する平面内において、半導体基板の貫通孔5の占める領域全体が多層配線基板内貫通孔4の占める領域に含まれている多層配線基板。

(もっと読む)

281 - 300 / 300

[ Back to top ]