Fターム[5F033VV08]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084)

Fターム[5F033VV08]の下位に属するFターム

Fターム[5F033VV08]に分類される特許

61 - 80 / 204

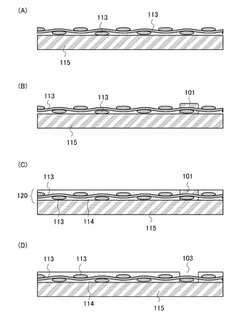

配線基板及びその作製方法、並びに半導体装置及びその作製方法

【課題】繊維体に貫通孔を空けることなく、プリプレグの内部に導電領域を形成することを課題とする。

【解決手段】シート状繊維体の両面に、該シート状繊維体の内部まで含浸した絶縁性樹脂層と、前記絶縁性樹脂層に囲まれる領域に設けられた貫通配線を有し、前記貫通配線は、前記シート状繊維体を挟んで前記絶縁性樹脂層の両面に導電性材料が露出し、該導電性材料は、前記シート状繊維体の内部まで含浸している配線基板及びその作製方法、並びに、さらに、絶縁層の表面にバンプが露出した集積回路チップとを有し、前記バンプが前記貫通配線と接触するように、前記集積回路チップが前記樹脂含浸繊維体複合基板に密接している半導体装置及びその作製方法に関する。

(もっと読む)

スパイラルインダクタ及びその製造方法

【課題】サイズが小さいだけでなく、自己共振周波数が高く、損失及び漏れ電磁場を低減したスパイラルインダクタを実現できるようにする。

【解決手段】スパイラルインダクタは、基板11の上に形成された絶縁層21とインダクタコイル31とを備えている。絶縁層21は、凸部24を有し、インダクタコイル31は凸部24の側壁上に形成されている。

(もっと読む)

半導体装置及び回路基板

【課題】小型の半導体装置においても静電容量の大きなキャパシタを配置することが可能な構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、半導体素子8が形成された半導体基板2と、半導体基板2のパッシベーション膜12を介して配置され1方向に長く形成された開口部4aを有する平面型のスロットアンテナ4と、スロットアンテナ4と並列接続する共振用キャパシタ15とを備え、共振用キャパシタ15はチップ型素子となっている。

(もっと読む)

トランス素子が形成されている半導体装置とその製造方法

【課題】トランス素子のコイル間絶縁膜をSiO2で形成すると、形成範囲を規制するのが困難である。有機質絶縁材料を利用すれば形成範囲を自在に調整できが、厚くなってしまい、2次側コイルに生じる電圧が小さくなる。

【解決手段】半導体基板上に、下側コイル135とコイル間絶縁膜140と上側コイル154の積層構造でトランス素子155が形成されている。コイル間絶縁膜140が絶縁性無機質粒子の集積物で形成されている絶縁層141aを備えている。絶縁性無機質粒子の集積物でコイル間絶縁膜を形成すると、必要な耐圧特性を得るのに必要な厚みが薄くてすむ。従って、1次側コイル154と2次側コイル135の磁気的結合係数を高め、2次側コイル135に大きな電圧を生じさせることができる。しかも、絶縁性無機質粒子の集積物でコイル間絶縁膜を形成すると、コイル間絶縁膜の形成範囲を規制しやすい。

(もっと読む)

半導体装置

【課題】積層された第1インダクタと第2インダクタの間の絶縁耐圧を高くする。

【解決手段】基板10上には、多層配線層400、第1インダクタ310、及び第2インダクタ320が形成されている。多層配線層400は、絶縁層及び配線層をこの順にそれぞれt回(t≧3)以上交互に積層したものである。第1インダクタ310は、多層配線層400の第n配線層に設けられている。第2インダクタ320は、多層配線層400の第m配線層(t≧m≧n+2)に設けられ、第1インダクタ310の上方に位置している。第n配線層と第m配線層の間に位置するいずれの配線層にも、第1インダクタ310の上方に位置するインダクタが設けられていない。第1インダクタ310及び第2インダクタ320は、電気信号を相互に伝達する信号伝達素子300を構成している。

(もっと読む)

半導体装置、通信モジュールおよび電子機器

【課題】安定した利得が得られるアンテナ素子を備えた半導体装置、通信モジュールおよび電子機器を提供すること。

【解決手段】半導体装置10は、能動素子が形成された能動面1aを有する半導体基板1と、能動面1a上に少なくとも1層以上の絶縁性樹脂層を介して設けられた第1の配線層8と、第1の配線層8に形成されたスロットアンテナ11と、スロットアンテナ11に接続された共振用キャパシタ13とを備え、スロットアンテナ11は、矩形状の開口部11bを有する平面型のアンテナ素子である。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】単位面積あたりのインダクタンス値が従来よりも大きいインダクタを内蔵した半導体装置を実現する。

【解決手段】本発明に係る半導体装置の製造方法は、第1領域2Aと第2領域2Bに区分された半導体基板2に対して、第1の配線層によって第1のインダクタ配線と第1の回路配線とを形成する工程と、第2の配線層によって第2のインダクタ配線と第2の回路配線とを形成する工程とを、複数回にわたって繰り返すことにより、半導体基板2の第1領域2Aに積層構造をなす渦巻き状のインダクタ3を形成する。

(もっと読む)

配線構造、半導体装置及び半導体装置の製造方法

【課題】 高周波信号の伝達も含めた配線抵抗を低減することができると共に、良好な遮蔽導体として機能する配線構造及びその配線構造を有する半導体装置を提供する。

【解決手段】 複数の配線層にそれぞれ設けられた配線1,3が互いに重複し、互いに電気的に複数層に亘り並列接続された配線構造であって、複数の配線層の少なくとも下層の一つの配線層が、少なくとも2本以上の並列配線に分離されて延伸しているスリット配線部を有し、上層の配線3からスリット配線部の並列配線の間隙に浸入して両側の並列配線と接続しているスリット接続部2aを有する配線構造とする。

(もっと読む)

半導体装置の作製方法

【課題】端部の勾配が急峻であり、所望の膜厚を確保することができ、マスクパターンとの形状の差が抑えられる導電膜を、エッチングを用いて作製する。

【解決手段】膜厚1μm以上10μm以下のアルミニウムまたはアルミニウム合金を含む導電膜を、ウェットエッチングを用いて所定の膜厚となるまでエッチングした後、残りをドライエッチングでエッチングすることで、サイドエッチングを抑え、なおかつマスクの膜厚が減少するのを抑える。サイドエッチングを抑え、なおかつマスクの膜厚が減少するのを抑えることで、膜厚1μm以上10μm以下といった厚膜のアルミニウムまたはアルミニウム合金を含む導電膜であっても、端部の勾配が急峻であり、所望の膜厚を確保することができ、マスクパターンとの形状の差が抑えられるようにエッチングすることが可能となる。

(もっと読む)

不具合検出機能を備えた半導体装置

【課題】層間絶縁膜の剥離を検出する半導体装置を提供する。

【解決手段】半導体チップ2の外周に沿って層間絶縁膜の剥離を検出するための信号を伝送する検査配線3が形成されている。検査配線3に検出信号を供給するための検出回路4と、検査配線3を流れた検出信号を出力するための出力端子5と、半導体チップ2に設けられた内部回路6と、内部回路6からの出力信号と、検査配線3を流れた検出信号とのいずれか一方を選択して出力端子5に供給する出力切替回路7を備える。検査配線3は適当な間隔毎に切断され、層間配線10を通して最上層配線8に載せ替えて接続されている。以上の構成により、測定端子数を増やすことなく層間絶縁膜の剥離を容易に検出することが可能となり、さらに層間絶縁膜の接着を補強することができる。

(もっと読む)

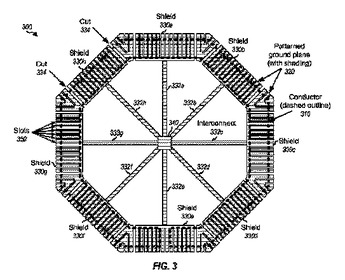

パターン化された接地平面を有するインダクタ

パターン化された接地平面を有するインダクタが、説明される。一設計においては、インダクタは、第1の層上に形成された導体と、その導体の下の第2の層上に形成されたパターン化された接地平面と、を含む。パターン化された接地平面は、オープンな中心エリアと、導体の形状に整合した形状と、を有する。パターン化された接地平面は、複数のシールド、例えば、八角形の形状の導体の8つの辺についての8つのシールド、を含んでいる。各シールドは、導体に垂直に形成された複数のスロットを有する。パターン化された接地平面を別個のシールドへと分割することと、各シールド上にスロットを形成することとは、パターン化された接地平面上の渦電流の流れを防止するのに役立ち、これは、インダクタのQを改善することができる。複数の相互接続は、複数のシールドを回路接地へと結合し、この回路接地は、導体の中心に位置することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】抵抗値が大きく、また、磁力線が回路に悪影響を及ぼすおそれがあった。

【解決手段】(1)(1a)渦巻状の巻線本体と、(1b)前記巻線本体の両端部のうち中心側の端部の近傍を起点として外側に向けて延在する配線と、(1c)前記巻線本体の前記中心側の端部と前記配線の中心側の端部とを斜めに接続するビアと、を有するインダクタと、(2)前記巻線本体により規定される仮想平面と平行に、かつ、前記巻線本体の下方に設けられている、複数の遮蔽板片からなる遮蔽板と、を含む。

(もっと読む)

半導体装置

【課題】合計長が長くなることにより抵抗値が大きくなり、また、表皮効果により、実施的な抵抗値が大きくなった。

【解決手段】インダクタを含む半導体装置であって、前記インダクタは、(1)第1の導体と、当該第1の導体の表面に形成されている、前記第1の導体より導電性が高い第2の導体と備える渦巻状の巻線本体と、(2)第3の導体と、当該第3の導体の表面に形成されている、前記第3の導体より導電性が高い第4の導体とを備え、前記巻線本体の両端部のうち中心側の端部を起点として外側に向けて延在する配線と、(3)前記巻線本体の中心側の端部と前記配線の中心側の端部とを斜めに接続するビアと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 渦巻き形状の薄膜誘導素子を備えたCSPと呼ばれる半導体装置において、シリコン基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減する。

【解決手段】 シリコン基板1と薄膜誘導素子9との間には低誘電率膜5が設けられている。これにより、シリコン基板1に発生する渦電流に起因する薄膜誘導素子9の渦電流損を低減することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】二次配線と半導体チップの電子回路部とが重なり合う場合においても、当該二次配線と当該電子回路部との間の電磁界的干渉を抑制することができると共に、ウエハの彎曲を抑えることができ、かつ、ダイシング工程において、チッピングが発生する危険性を低減することができる半導体装置を提供する。

【解決手段】半導体装置1aは、半導体チップ2において、第1の二次配線未形成領域の絶縁層が、第1の二次配線形成領域の絶縁層よりも薄く形成される。また、半導体チップ2における、電極パッド10が形成された回路形成面が伸びている方向に関し、半導体チップの縁31が、上層絶縁層12の縁である側壁部12sよりも突出している。

(もっと読む)

配線構造、インダクタ、及び半導体装置

【課題】ビアを無くす事によって、配線の線幅を太くする必要を無くし、サイズを縮小した半導体装置の提供。

【解決手段】第1の配線の一部MT1eと第2の配線の一部MT2dとが交差しなければならない箇所で、前記第1の配線の前記一部MT1e及び前記第2の配線の前記一部MT2d間に絶縁層DEbが形成されており、前記第1の配線の前記一部が、前記絶縁層の一の面に接して設けられており、前記第2の配線の前記一部が、前記絶縁層の他の面に接して設けられている。

(もっと読む)

半導体集積回路

【課題】面積が小さく、かつコストの低い半導体集積回路を提供する。

【解決手段】半導体基板1上に積層された複数の配線層と、2GHzの周波数帯域に対応して、複数の配線層のうちの1つの配線層に形成された2G用インダクタ4と、2GHzの周波数帯域よりも高い5GHzの周波数帯域に対応して、2G用インダクタ4が形成された配線層と同一の配線層に形成された5G用インダクタ5とを備え、5G用インダクタ5は、2G用インダクタ4の開口部の内側に形成されるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズを縮小することにより、LCDドライバの製造コストを低減させることのできる技術を提供する。

【解決手段】第1金属膜からなるバンプ6が形成されない領域のパッシベーション膜9上に、第2金属膜からなる容量素子7C、抵抗素子7Rまたはインダクタンス素子7L等の受動素子を形成する。第1金属膜は金膜、第2金属膜は金膜、ニッケル膜または銅膜であり、あるいは第1金属膜は下層をニッケル膜または銅膜とし上層を金膜とする積層膜、第2金属膜はニッケル膜または銅膜である。さらに、第1金属膜の厚さは第2金属膜の厚さと同じか、あるいは第2金属膜の厚さよりも厚く形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は受動素子を備えた半導体装置及びその製造方法に関し、装置の小型化を図りつつ、かつ誘電損失の発生を抑制することを課題とする。

【解決手段】半導体チップ11と、半導体チップ11を貫通して形成された15,16とを有した半導体装置であって、半導体チップ11の第1面35A(主面)に対する反対側の第2面35Bに、貫通電極15と接続したグランド層28と、貫通電極16に接続したパッチアンテナ33とをSiO2又はSiNよりなる無機絶縁層30を介して積層した構成とする。

(もっと読む)

半導体装置

【課題】インダクタからのノイズおよびインダクタへのノイズを効果的に抑制する。

【解決手段】半導体装置100は、半導体基板(102)と、半導体基板上に形成された絶縁膜106と、絶縁膜106を介して、半導体基板上に形成されたインダクタ120と、平面視でインダクタ120を囲み、インダクタ120を他の領域から隔離するガードリング108とを含む。ガードリング108は、半導体基板表面に設けられた環状の不純物拡散層110と、ガードリング108に接続し、複数の配線層にわたって延在するとともにインダクタ120が設けられた層以上の層まで延在する環状の導電体(112、114、136、および138)とを含む。

(もっと読む)

61 - 80 / 204

[ Back to top ]